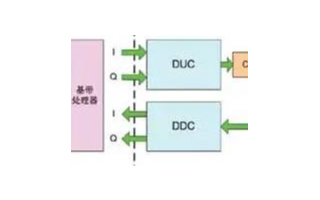

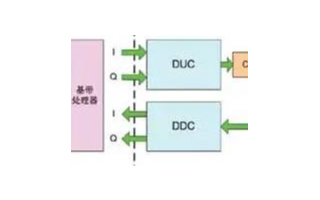

中頻技術(shù)通常包括上下變頻(DUC/DDC)、波峰因子衰減(CFR)和數(shù)字預(yù)失真(DPD)。 DUC/DDC DUC實(shí)現(xiàn)了從“復(fù)”基帶(Baseband)信號到“實(shí)”帶通(Pas***and)信號的轉(zhuǎn)換。輸入的復(fù)基帶信號采樣率相對較低

2023-10-21 18:59:00 8578

8578

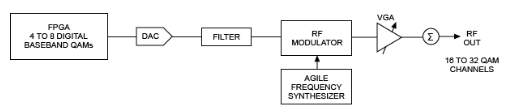

本文介紹了基于MAX5879等RF DAC的RF直接變頻發(fā)送器設(shè)計(jì),文章列舉了零中頻、正交IF調(diào)制、高中頻調(diào)制以及RF直接變頻架構(gòu),詳細(xì)介紹了RF直接變頻帶給智能手機(jī)、平板電腦等無線設(shè)備的優(yōu)勢。

2013-04-03 16:40:39 3085

3085

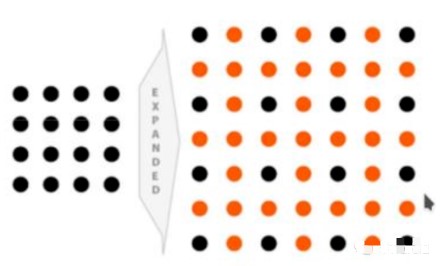

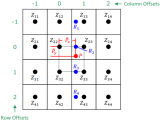

今天的算法是插值,細(xì)分是牛頓插值。關(guān)于插值可能大家聽到最多的就是圖像插值,比如100元的攝像頭有4K的分辨率???其實(shí)這里就是使用的插值算法,通過已經(jīng)有的數(shù)據(jù)再生成一些,相當(dāng)于提升了數(shù)據(jù)的量。如果我們想放大圖像,我們需要使用過采樣算法來擴(kuò)展矩陣。

2022-07-12 09:50:27 2646

2646

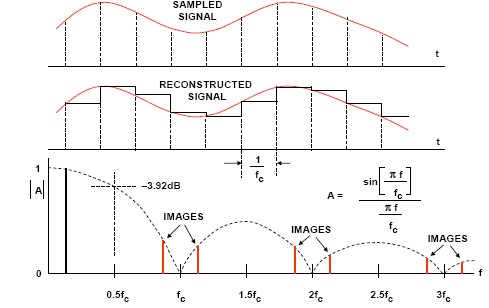

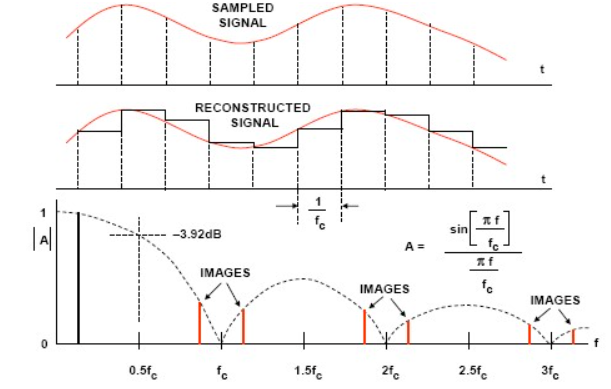

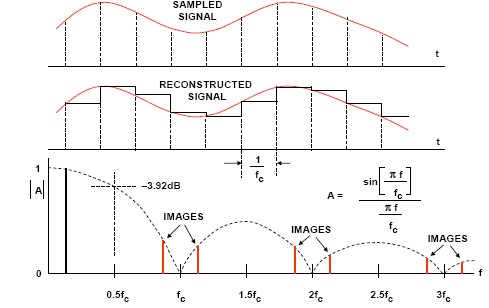

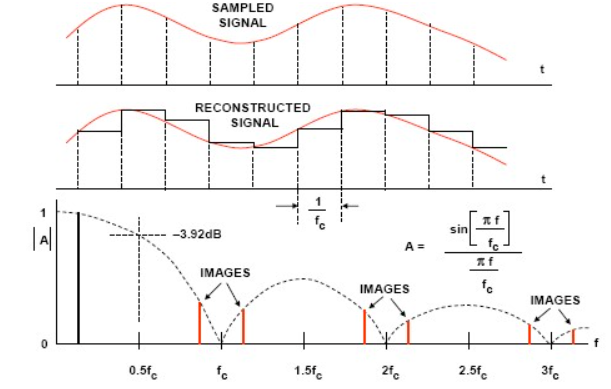

過采樣和數(shù)字濾波有助于降低對ADC前置的抗混疊濾波器的要求。重構(gòu)DAC可以通過類似的方式運(yùn)用過采樣和插值原理。

2022-08-01 09:53:59 3506

3506

過采樣和數(shù)字濾波有助于降低對ADC前置的抗混疊濾波器的要求。重構(gòu)DAC可以通過類似的方式運(yùn)用過采樣和插值原理。例如,數(shù)字音頻CD播放器常常采用過采樣,其中來自CD的基本數(shù)據(jù)更新速率為44.1 kSPS。

2021-08-25 14:53:42 3945

3945

(IF)信號。正交解調(diào)器再將中頻信號向下轉(zhuǎn)換成復(fù)基帶(BB)信號,在復(fù)基帶處,信號被雙通道模數(shù)轉(zhuǎn)換器(ADC)采樣并傳遞到數(shù)字處理器。 奈奎斯特采樣定理規(guī)定,采樣頻率必須至少是信號帶寬的兩倍;但在

2018-09-06 14:58:45

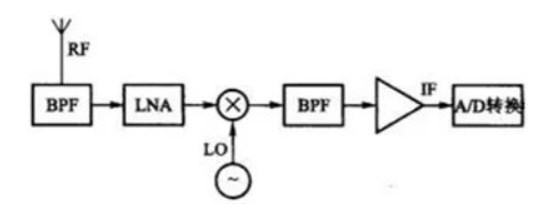

一種中頻直接采樣方案

2012-11-25 15:47:05

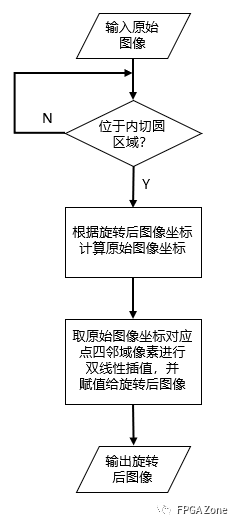

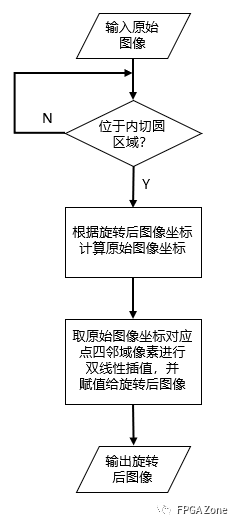

針對視頻的輸出顯示要求,重點(diǎn)介紹了基于雙線性插值算法的實(shí)現(xiàn)。ModelSim的仿真結(jié)果表明,該算法符合多屏幕顯示系統(tǒng)的要求。關(guān)鍵詞 視頻監(jiān)控;視頻圖像處理;雙線性插值;FPGA;多屏幕

2019-06-28 07:06:54

正交誤差在2°左右,即幅相誤差引入的鏡像功率在-34 dB左右。這樣的技術(shù)性能限制了信號處理器性能的提高。

2019-11-07 06:38:29

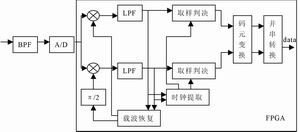

什么是數(shù)字中頻?FPGA怎么實(shí)現(xiàn)數(shù)字中頻?

2021-05-08 08:05:40

,D是插值倍數(shù)。如果我們直接用F1*D倍的采樣率采信號,得到的頻譜會(huì)發(fā)現(xiàn),就不會(huì)有中間兩個(gè)波形,因此,這兩個(gè)波形是多余的,書上叫做是鏡像頻譜。既然是多余的,我們就可以將它用一個(gè)低通濾波器濾掉,這樣

2018-11-15 00:27:19

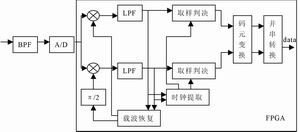

本文研究了中頻軟件無線電的實(shí)現(xiàn)方案,并設(shè)計(jì)了基于FPGA的通用硬件平臺(tái)。在此平臺(tái)上,通過PC機(jī)下載軟件,實(shí)時(shí)實(shí)現(xiàn)了軟件無線電中頻至基帶的波形處理和多種不同的調(diào)制解調(diào)方式。

2021-04-29 06:27:47

源碼-基于FPGA設(shè)計(jì)的插值濾波器設(shè)計(jì).rar (12.14 KB )

2019-05-08 06:35:28

1,背景

利用FPGA做數(shù)據(jù)處理、系統(tǒng)控制時(shí),經(jīng)常需要做線性插值。如圖(1)所示,給點(diǎn)A和B的x,y坐標(biāo),需要求A,B中間某一點(diǎn)C的坐標(biāo)。限定x取整數(shù)。

圖(1) 插值示意圖

根據(jù)A,B兩點(diǎn)即可

2023-11-20 23:10:38

上次分享了基于FPGA的線性插值的背景和方法原理,今天分享

方法原理的驗(yàn)證。

通常FPGA的開發(fā)分為電路功能設(shè)計(jì)、設(shè)計(jì)輸入、功能仿真、綜合優(yōu)化、綜合后仿真、實(shí)現(xiàn)、布線后仿真、板級仿真以及芯片編程

2023-11-23 23:09:43

采用ADC(LTC2208)、FPGA和SDRAM(HY57V561620)設(shè)計(jì)高速的數(shù)據(jù)采集及正交下變頻系統(tǒng),其中數(shù)據(jù)采樣速率90MSPS;實(shí)現(xiàn)70M中頻的數(shù)字正交下變頻…………請求大牛的幫助啊,我是小菜鳥,這方面還需要你們的大力提攜啊,萬分感謝

2014-04-01 10:44:33

本文基于隨著通信市場模塊化、小型化、低互調(diào)、高效率的發(fā)展趨勢,重點(diǎn)討論了通信設(shè)備內(nèi)模塊與設(shè)備外模塊的連接器設(shè)計(jì)與實(shí)現(xiàn),主要討論如何實(shí)現(xiàn)快插連接器的低互調(diào)以及降低電磁泄漏,介紹了母端連接器采用劈6 槽

2021-05-20 06:04:31

中頻調(diào)制解調(diào)系統(tǒng)具有哪些特點(diǎn)?如何利用FPGA去實(shí)現(xiàn)中頻調(diào)制解調(diào)系統(tǒng)?

2021-04-28 07:21:00

例如,現(xiàn)在有X,C,W三個(gè)值,每一組(X.C)對應(yīng)一個(gè)W值,我擁有幾組(X,C)和W的對應(yīng)關(guān)系(即具體數(shù)值),我要根據(jù)未知的一組(X,C)來通過插值得到W值。其中X和C沒有對應(yīng)關(guān)系,請問應(yīng)該如何在labview FPGA端實(shí)現(xiàn)。目前我只是實(shí)現(xiàn)了一維插值,即X單獨(dú)對應(yīng)W或者C單獨(dú)對應(yīng)W。

2024-05-15 14:59:36

MATLAB程序。我們知道Matlab的一個(gè)強(qiáng)大之處在于給我們提供了很多API可以調(diào)用,為我們節(jié)省了不少時(shí)間,而且大多數(shù)的函數(shù)我們都是可以看到源碼的。比如我們今天所說的插值濾波器,可以直接

2020-12-24 16:03:16

如何設(shè)計(jì)并實(shí)現(xiàn)一種高性能中頻采樣系統(tǒng)?中頻采樣系統(tǒng)系統(tǒng)總體設(shè)計(jì)由哪些組成?它們分別有什么作用?

2021-04-07 07:09:32

、數(shù)字濾波器設(shè)計(jì)(IIR、FIR及特殊形式的濾波器)等;下篇內(nèi)容包括信號的正交變換(正交變換的定義與性質(zhì)、K-L變換、DCT及其在圖像壓縮中的應(yīng)用)、信號處理中若干典型算法(如抽取與插值、子帶分解、調(diào)制

2023-09-19 08:01:36

數(shù)字陣列雷達(dá)可以實(shí)現(xiàn)陣元級的數(shù)字收發(fā),為了減少射頻前端的復(fù)雜性同時(shí)降低對高采樣率的需求,本文簡單介紹正交解調(diào)接收機(jī),或者稱為零中頻接收機(jī),從而每個(gè)陣元只需要一個(gè)本振就可以了。零中頻接收機(jī)的一個(gè)重要

2020-08-29 08:23:49

求教大俠指導(dǎo)樣條插值。如果已知一組數(shù)據(jù)【(x,y)】,對其按等間隔(非時(shí)間)采樣后【(c1,y1)】。現(xiàn)在想通過對原數(shù)據(jù)進(jìn)行樣條插值,并求出在y1時(shí)刻的x1值序列。該如何實(shí)現(xiàn)???跪求啊!!!

2013-10-31 21:36:45

以及系統(tǒng)實(shí)現(xiàn)的復(fù)雜度。本文介紹的等效時(shí)間采樣技術(shù)由于使用了FPGA 采樣技術(shù), 使得在被采樣信號的一個(gè)周期中相較于一個(gè)周期僅能采集一個(gè)點(diǎn)的順序等效時(shí)間采樣有很大的提高,并且可以控制被采集信號一個(gè)周期

2020-10-21 16:43:20

的 1Gsps 采樣率?按照常識(shí),FPGA 應(yīng)該輸出 1G 的數(shù)據(jù)速率,那么 AD9779A 的采樣率就可以達(dá)到 1G。然后我在芯片手冊中讀到有一個(gè)插值濾波器。插值 8x 時(shí),FPGA 是不是只需要輸出 125M 就能實(shí)現(xiàn) 1Gsps 的 AD9779A?,希望這方面能有詳細(xì)的解答,謝謝。

2025-06-10 06:29:02

框圖上面看,是要直接對這樣的數(shù)據(jù)進(jìn)行插值濾波么?附件紅色標(biāo)記處,DATA ASSEMBLER對 數(shù)據(jù)進(jìn)行的是什么處理?對于正交半帶濾波,貴司有相關(guān)的介紹資料么?附件DAC.PNG180.7 KB

2019-01-10 11:50:46

請問一下基于FPGA技術(shù)如何實(shí)現(xiàn)彩色圖像的Bayer插值變換?

2021-04-29 06:48:02

窄帶正交數(shù)字中頻TX單次轉(zhuǎn)換觀測RX

2018-10-10 15:38:28

高精度Σ-△DAC中插值濾波器的研究與設(shè)計(jì):基于系統(tǒng)研究插值濾波器理論,選用了兩級半帶濾波器實(shí)現(xiàn)4×插值和級聯(lián)32×采樣保持電路,設(shè)計(jì)了一種適用于高精度音頻過采樣Σ-△DAC

2009-06-21 22:42:38 54

54 根據(jù)軟件無線電的思想,用可編程器件FPGA 實(shí)現(xiàn)了QPSK 解調(diào),采用帶通采樣技術(shù)對中頻為70MHz 的調(diào)制信號采樣,通過對采樣后的頻譜進(jìn)行分析,用相干解調(diào)方案實(shí)現(xiàn)了全數(shù)字解調(diào)

2009-08-27 11:00:14 68

68 根據(jù)中頻采樣多模式數(shù)字接收機(jī)的理論,利用專用數(shù)字下變頻器、數(shù)字信號處理器為主的芯片,構(gòu)建了一種在中頻直接采樣的多模式數(shù)字接收機(jī)系統(tǒng)。并對各個(gè)模塊的應(yīng)用設(shè)計(jì),

2009-08-28 12:03:49 36

36 本文闡述了雷達(dá)中頻信號相干檢波的原理,根據(jù)該原理使用FPGA 對特定的雷達(dá)中頻信號進(jìn)行采樣來實(shí)現(xiàn)正交數(shù)字相干檢波,設(shè)計(jì)所使用軟件是MentorGraphics 的FPGA Advantage,完成了

2010-06-15 08:26:41 53

53 提出了一種數(shù)字接收機(jī)中符號同步的硬件設(shè)計(jì)方案。該方案屬于異步采樣恢復(fù)法,其插值濾波器的設(shè)計(jì)采用了理想插值算法加窗處理,較傳統(tǒng)的拉格朗日插值有更好的頻域特性。該

2010-07-05 16:33:19 17

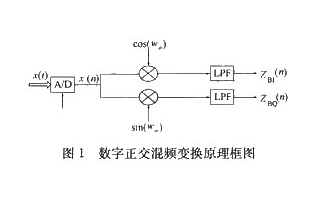

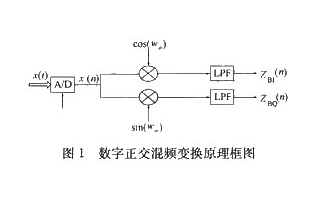

17 本文研究了用DDS加乘法器實(shí)現(xiàn)正交數(shù)字混頻器的設(shè)計(jì)及其完整的驗(yàn)證方法,用DDS產(chǎn)生的正/余弦正交本振序列與模擬信號通過A/D采樣數(shù)字化后的數(shù)字序列相乘,再通過數(shù)字低通濾波實(shí)現(xiàn)

2010-07-17 18:02:32 47

47 基于AVS運(yùn)動(dòng)補(bǔ)償分?jǐn)?shù)像素插值算法,提出了一種新的VLSI結(jié)構(gòu),滿足了AVS基準(zhǔn)檔次6.2級別(1920×1080,4:2:2,30 f/s)高清視頻實(shí)時(shí)解碼的要求。介紹了AVS分?jǐn)?shù)像素插值算法,采用一種新

2010-10-15 09:38:28 0

0 提出了一種改進(jìn)型中頻數(shù)字化正交解調(diào)結(jié)構(gòu),通過在現(xiàn)場可編程門陣列內(nèi)部對采樣數(shù)據(jù)流拆分后,分路進(jìn)行數(shù)字解調(diào)的方法,大幅降低了現(xiàn)場可編程門陣列的內(nèi)核工作頻率。解決了

2010-11-22 15:09:51 0

0

為提高中頻采樣系統(tǒng)性能,降低板級噪聲,加大采樣頻率的靈活性,設(shè)計(jì)并實(shí)現(xiàn)一種高性能中頻采樣系統(tǒng)。該系統(tǒng)利用AD9518-4實(shí)現(xiàn)可配置的采樣時(shí)鐘,根據(jù)不同的采樣要

2010-12-07 13:40:23 22

22 摘 要:本文提出了一種基于FPGA的寬帶中頻數(shù)字接收機(jī)的實(shí)現(xiàn)方法。

2006-03-11 13:19:24 1748

1748

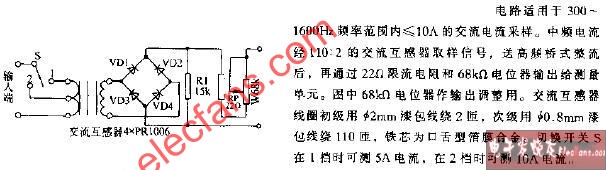

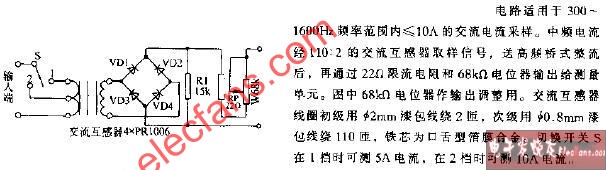

中頻大電流信號采樣電路

2009-02-10 09:10:38 1616

1616

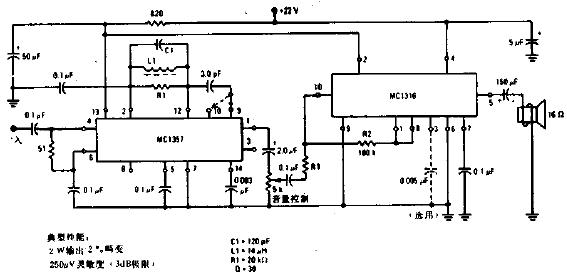

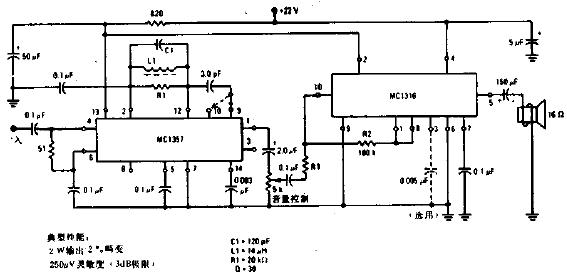

帶有正交檢波器的電視伴音中頻或調(diào)頻中頻放大器電路圖

2009-04-15 08:47:21 1265

1265

摘要:介紹了利用Altera的FPGA器件(ACEX EP1K50)實(shí)現(xiàn)直接數(shù)字頻率合成器的工作原理、設(shè)計(jì)思想、電路結(jié)構(gòu)和改進(jìn)優(yōu)化方法。

關(guān)鍵詞:直接數(shù)字

2009-06-20 13:53:19 796

796

摘要: 介紹了利用現(xiàn)場可編程邏輯門陣列FPGA實(shí)現(xiàn)直接數(shù)字頻率合成(DDS)的原理、電路結(jié)構(gòu)和優(yōu)化方法。重點(diǎn)介紹了DDS技術(shù)在FPGA中的實(shí)現(xiàn)方法,給出了采用ALTERA公

2009-06-20 14:14:36 989

989

我們是否能夠提供一款其功能可滿足客戶所有獨(dú)特設(shè)計(jì)要求的DSP內(nèi)核,我常常建議他們使用我們器件中的插值查找表來定制他們的DSP功能。

2011-03-03 09:50:50 2392

2392

在對中頻GPS信號理論建模與分析的基礎(chǔ)上,采用Matlab/Simulink構(gòu)建了一種精確的數(shù)字中頻GPS信號軟件模擬器,考慮了噪聲、欠采樣以及接收機(jī)時(shí)鐘誤差等的影響。軟件模擬器的實(shí)現(xiàn)采用Matl

2011-03-30 16:56:29 35

35 CDMA200系統(tǒng)中,信道是經(jīng)過QPSK四相擴(kuò)頻正交調(diào)制傳輸?shù)模瑪?shù)字中頻與模擬中頻相比能產(chǎn)生嚴(yán)格的幅相平衡正交信號,處理時(shí)能保證有嚴(yán)格的線性相位。為此介紹了CDMA200系統(tǒng)數(shù)字中頻調(diào)制

2011-04-08 15:20:51 43

43 針對一種線性調(diào)頻連續(xù)波(LFMCW)雷達(dá)系統(tǒng)結(jié)構(gòu),提出一種中頻接收機(jī)硬件平臺(tái)的設(shè)計(jì)方案。該方案采用AD8347正交解調(diào)器做I/Q下變頻,AD9248模數(shù)轉(zhuǎn)換器做采樣,EP3C80 FPGA做數(shù)字信號處理,

2011-04-28 10:44:24 65

65 傳統(tǒng)的中頻數(shù)字化正交解調(diào)系統(tǒng)中芯片選擇的限制及成本的大幅上升。為此提出了一種新的中頻數(shù)字化 正交解調(diào) 系統(tǒng)結(jié)構(gòu),在保留高速A/D的高數(shù)據(jù)率輸出的同時(shí),大幅降低現(xiàn)場可編程

2011-10-08 11:09:14 5660

5660

過采樣和數(shù)字濾波有助于降低對ADC前置的抗混疊濾波器的要求。重構(gòu)DAC可以通過類似的方式運(yùn)用過采樣和插值原理。例如,數(shù)字音頻CD播放器常常采用過采樣,其中來自CD的基本數(shù)據(jù)更新

2011-12-12 15:51:45 85

85 為了在LabVIEW平臺(tái)下更方便的處理非均勻采樣的心電信號,文中研究了心電信號的時(shí)域和頻域插值算法。首先采用了拉格朗日插值法、牛頓插值法、埃爾米特插值法和三次樣條插值法等四

2013-03-15 17:10:03 61

61 CCD圖像的顏色插值算法研究及其FPGA實(shí)現(xiàn)

2016-08-29 15:02:03 12

12 采用相鄰采樣求和的突發(fā)模式相位插值型CDR_覃林

2017-01-07 21:45:57 0

0 正交相位調(diào)制,理論介紹。

2017-09-20 08:51:17 10

10 摘要:高速中頻采樣信號處理平臺(tái)在實(shí)際應(yīng)用中有很大的前景,提出采用FPGA+DSP的處理結(jié)構(gòu),結(jié)合高性能A/D和D/A處理芯片,設(shè)計(jì)了一個(gè)通用處理平臺(tái),并對其主要性能進(jìn)行了測試。實(shí)驗(yàn)與實(shí)際應(yīng)用表明

2017-10-30 11:46:08 2

2 傳統(tǒng)的插值算法在視頻圖像縮放尤其是輸出高分辨率的視頻圖像時(shí),對細(xì)節(jié)方面的處理性能較差。采用多相位插值算法實(shí)現(xiàn)視頻圖像縮放,主要闡述算法的原理及算法實(shí)現(xiàn)的硬件結(jié)構(gòu)。其中硬件電路控制部分使用Xilinx

2017-11-16 11:48:09 5853

5853

實(shí)現(xiàn)了基于FPGA的雙線性CFA插值算法。該算法的處理對象是每個(gè)像素為8bit的XGA@15Hz的Bayer模板數(shù)據(jù),目的是能得到每個(gè)像素是24bit的XGA@15Hz的彩色圖像數(shù)據(jù)。輸入的數(shù)據(jù)先進(jìn)

2017-11-23 14:24:57 4931

4931

)全部奈奎斯特帶寬背后的動(dòng)因是,降低功耗、在日益密集的封裝中減輕熱量問題、降低成本、延長備用時(shí)間或電池壽命等需求在本文中,我們將探討這種類型的設(shè)計(jì)要面臨的一些挑戰(zhàn)和所擔(dān)心的問題,同時(shí)在信號帶寬接近 100MHz 時(shí),對直接轉(zhuǎn)換與中頻采樣 (IF--sampling) 進(jìn)行比較。

2017-12-04 06:33:01 2709

2709

本文運(yùn)用局部多項(xiàng)式的方法對圖像進(jìn)行插值。文中我們從一幅高分辨率圖像通過下采樣得到一張低分辨率圖像,然后對其進(jìn)行插值并求出插值圖像的峰值信噪比(PSNR)。為說明本文方法的可行性,我們把本文的方法

2017-12-20 10:02:23 1

1 多項(xiàng)式近似理論為圖像的多項(xiàng)式插值算法提出一個(gè)統(tǒng)一的理論框架。密切多項(xiàng)式近似的理論框架包括采樣點(diǎn)數(shù)目、密切階數(shù)和導(dǎo)數(shù)近似規(guī)則三個(gè)部分,它既可以用于分析現(xiàn)有的多項(xiàng)式插值算法,也可以用于開發(fā)新的多項(xiàng)式插值算法。

2018-01-05 13:55:39 0

0 本文檔的目的是介紹與高速、數(shù)模轉(zhuǎn)換器(DAC)相關(guān)的廣泛的理論和主題。該文件提供了關(guān)于采樣理論、數(shù)據(jù)表規(guī)范、常見系統(tǒng)級關(guān)注以及插值FAC、數(shù)字混合和正交調(diào)制器校正的內(nèi)插DAC的共同功能的細(xì)節(jié)。

2018-05-25 16:14:09 9

9 數(shù)據(jù)采集系統(tǒng)的總體架構(gòu)如圖1所示,其中PCI核、DMA控制器與A/D控制器均在FPGA內(nèi)部實(shí)現(xiàn)。為實(shí)現(xiàn)多路并行采樣,可選用多片A/D器件并行處理的方式,在FPGA的高速狀態(tài)機(jī)控制下,完成模擬信號經(jīng)過

2018-08-28 10:16:07 14862

14862

高速中頻采樣信號處理平臺(tái)在實(shí)際應(yīng)用中有很大的前景,提出采用FPGA+DSP的處理結(jié)構(gòu),結(jié)合高性能A/D和D/A處理芯片,設(shè)計(jì)了一個(gè)通用處理平臺(tái),并對其主要性能進(jìn)行了測試。

2018-10-18 16:36:48 5708

5708

我們可以看到,該網(wǎng)絡(luò)將傳統(tǒng)的非線性插值替換成 DUpsample,同時(shí)在 feature fuse 方面,不同于之前方法將 Decoder 中的特征上采樣與 Encoder 特征融合,本工作將 Encoder 中的特征下采樣與 Decoder 融合,大大減少了計(jì)算量 ,這都得益于 DUpsample。

2019-04-08 14:47:15 7283

7283

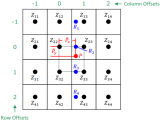

雙線性插值顧名思義是線性插值Pro,為了說明白什么是雙線性插值,首先得先從線性插值說起。那么什么又是線性呢?

2019-08-09 17:33:03 4965

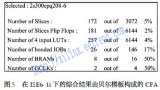

4965 ,如何在充分利用現(xiàn)有FPGA器件資源情況下能更高效的實(shí)現(xiàn)所需模塊功能是值得深入研究的。本文首先介紹了實(shí)際應(yīng)用中常見的中頻接收機(jī)各模塊,然后通過編寫各自的硬件描述語言分別映射到三種不同的FPGA芯片,最終通過布線工具軟件的布線報(bào)告得出相關(guān)的設(shè)計(jì)結(jié)論。

2019-11-28 18:00:41 6

6 電子戰(zhàn)設(shè)備的要求。為此,人們提出了對中頻信號直接采樣,經(jīng)過混頻來實(shí)現(xiàn)正交數(shù)字下變頻的方案,這種下變頻的方法可以實(shí)現(xiàn)很高精度的正交混頻,能滿足高鏡頻抑制的要求。采用可編程器件FPGA對該算法流程進(jìn)行實(shí)現(xiàn),能滿足在高采樣率下的信號時(shí)實(shí)處理要求,在電子戰(zhàn)領(lǐng)域中有著重要的意義。

2020-03-04 09:07:47 2683

2683

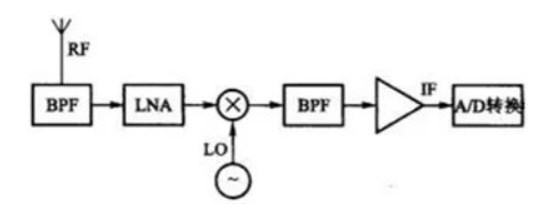

一、什么是中頻采樣,什么是IQ采樣 射頻接收系統(tǒng)通常使用數(shù)字信號處理算法進(jìn)行信號解調(diào)和分析,因此需要使用ADC對信號進(jìn)行采樣。根據(jù)采樣頻率的不同,可以分為射頻直接采樣、中頻采樣、IQ采樣。射頻采樣

2020-12-02 14:03:25 11856

11856 本文檔的主要內(nèi)容詳細(xì)介紹的是基于FPGA的AD采樣的實(shí)現(xiàn)免費(fèi)下載。

2021-01-21 15:33:54 32

32 對幾種常用的圖像縮放算法進(jìn)行了比較,在權(quán)衡了算法復(fù)雜度、縮放效果和FPGA 邏輯資源等3大因素后,選擇了雙線性插值算法來實(shí)現(xiàn)圖像縮放。重點(diǎn)介紹了雙線性插值算法和該方法的FPGA 硬件實(shí)現(xiàn)方法,包括

2021-01-25 14:51:00 6

6 該文研究了低軌道(LEO)衛(wèi)星CDMA系統(tǒng)發(fā)信機(jī)的數(shù)字部分,介紹了其結(jié)構(gòu)、算法原理及其具體實(shí)現(xiàn)。重點(diǎn)介紹了發(fā)信機(jī)數(shù)字信號處理部分在FPGA的實(shí)現(xiàn),主要包括信息數(shù)據(jù)流的處理及編碼、交織、成型濾波

2021-01-27 16:38:02 6

6 介紹了一種基于圖像的雙三次線性插值縮放算法的設(shè)計(jì)方法,并通過FPGA驗(yàn)證了設(shè)計(jì)的可行性。重點(diǎn)討論了視頻縮放的插值算法,對兩種實(shí)現(xiàn)方法在硬件資源利用率及實(shí)施效率方面進(jìn)行了比較并論證了塊狀插值實(shí)現(xiàn)方法的優(yōu)越性。最終設(shè)計(jì)實(shí)現(xiàn)了高分辨率實(shí)時(shí)視頻圖像的縮放。

2021-02-05 15:54:00 7

7 本文介紹了一個(gè)自行設(shè)計(jì)的數(shù)字化x射線影像實(shí)時(shí)處理系統(tǒng)中實(shí)現(xiàn)圖像實(shí)時(shí)縮放的子系統(tǒng)。重點(diǎn)分析了縮放涉及的插值算法,設(shè)計(jì)并實(shí)現(xiàn)了基于FPGA的三次插值的模塊,系統(tǒng)最終實(shí)現(xiàn)了對高顯示分辨率和幀率下的x線圖像的實(shí)時(shí)縮放。

2021-03-18 16:39:00 4

4 針對高速率QPSK數(shù)據(jù)傳輸鏈系統(tǒng),比較分析了數(shù)字中頻接收與零中頻接收的優(yōu)、缺點(diǎn),并提出了一種基于多相濾波的寬帶中頻正交采樣數(shù)字零中頻接收方案。基于FPGA對此數(shù)字零中頻正交變換方案進(jìn)行了實(shí)現(xiàn)和驗(yàn)證,同時(shí),對一種全數(shù)字零中頻QPSK信號的高速解調(diào)算法及其FPGA硬件實(shí)現(xiàn)進(jìn)行了介紹。

2021-03-19 17:43:12 11

11 MT-017: 過采樣插值DAC

2021-03-20 09:38:03 11

11 針對多屏幕拼接顯示系統(tǒng)中高分辨率.高清晰、低失真的顯示需求,提出了一種基于FPGA實(shí)現(xiàn)的實(shí)時(shí)視頻處理算法。在介紹了DVI接口屏幕拼接顯示的系統(tǒng)結(jié)構(gòu)及FPGA算法的主要功能后,針對算法處理對象具有視頻

2021-03-31 15:23:09 10

10 設(shè)計(jì)了一種基于FPGA的正交匹配追蹤(Orthogonal Matching Pursuit,OMP)算法的硬件優(yōu)化結(jié)構(gòu),對OMP算法進(jìn)行了改進(jìn),大大減

2021-04-08 13:28:52 3121

3121

LT5502:400 MHz正交中頻解調(diào)器,帶RSSI數(shù)據(jù)表

2021-05-23 13:31:52 6

6 今天的算法是插值,細(xì)分是牛頓插值。關(guān)于插值可能大家聽到最多的就是圖像插值,比如100元的攝像頭有4K的分辨率???其實(shí)這里就是使用的插值算法,通過已經(jīng)有的數(shù)據(jù)再生成一些,相當(dāng)于提升了數(shù)據(jù)的量。如果我們想放大圖像,我們需要使用過采樣算法來擴(kuò)展矩陣。

2022-07-12 10:03:35 1934

1934 射頻接收系統(tǒng)通常使用數(shù)字信號處理算法進(jìn)行信號解調(diào)和分析,因此需要使用ADC對信號進(jìn)行采樣。根據(jù)采樣頻率的不同,可以分為射頻直接采樣、中頻采樣、IQ采樣。射頻采樣和中頻采樣只需要一路ADC,采樣結(jié)果為

2022-07-28 09:05:47 5074

5074 :針對高速率 QPSK 數(shù)據(jù)傳輸鏈系統(tǒng),比較分析了數(shù)字中頻接收與零中頻接收的優(yōu)、缺點(diǎn),并提出了一種基

于多相濾波的寬帶中頻正交采樣數(shù)字零中頻接收方案。基于 FPGA 對此數(shù)字零中頻正交變換方案

2022-12-12 15:44:36 3

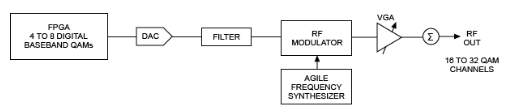

3 具有12至14位高分辨率的現(xiàn)代高速數(shù)模轉(zhuǎn)換器(DAC)為采用直接調(diào)制方案的新型發(fā)射器設(shè)計(jì)奠定了基礎(chǔ)。在此類設(shè)計(jì)中,調(diào)制后的傳輸信號直接在基頻上生成。到目前為止,這種方法僅用于生成有線電視系統(tǒng)中正交

2023-02-28 14:13:23 4233

4233

加法器、積分器和寄存器,適合于工作在高采樣率條件下,而且CIC濾波器是一種基于零點(diǎn)相消的FIR濾波器,已經(jīng)被證明是在高速抽取或插值系統(tǒng)中非常有效的單元。 我們首先產(chǎn)生一個(gè)采樣率Fs=0.78125Mhz,頻率Fout=0.078125Mhz的樣本信號,對其進(jìn)行16倍插值。這就涉及到直接頻率合成器DDS的知識(shí)。

2023-04-12 10:26:25 2701

2701 點(diǎn)擊上方 藍(lán)字 關(guān)注我們 在電阻抗多頻及參數(shù)成像技術(shù)中正交序列數(shù)字解調(diào)法的抗噪性能對信號每周期的采樣點(diǎn)數(shù)決定,采樣點(diǎn)數(shù)越多,抗噪性能越高。當(dāng)采樣信號頻率很高時(shí),為了在被采樣信號的一周期內(nèi)多采樣

2023-07-29 09:00:01 1670

1670

今天開源一個(gè)FPGA圖像處理相關(guān)的項(xiàng)目:圖像旋轉(zhuǎn)。圖像旋轉(zhuǎn)算法本身非常簡單,但是如果想讓旋轉(zhuǎn)之后的圖像更加完整、平滑,還需要進(jìn)行雙線性插值處理,因此整個(gè)算法FPGA實(shí)現(xiàn)起來還是有一定難度的。

2023-09-04 16:52:03 3157

3157

電子發(fā)燒友網(wǎng)站提供《高性能中頻采樣系統(tǒng)的設(shè)計(jì)與實(shí)現(xiàn).pdf》資料免費(fèi)下載

2023-10-18 09:57:34 0

0 中頻采樣是什么意思?中頻采樣與基帶采樣的區(qū)別? 中頻采樣與基帶采樣都是數(shù)字信號處理中常用的采樣技術(shù),它們的區(qū)別在于采樣信號的頻率不同。基帶采樣是指在信息原始頻域內(nèi)進(jìn)行采樣,而中頻采樣是指在信號已經(jīng)

2023-10-22 11:24:39 3754

3754 中頻采樣和IQ采樣是兩個(gè)在接收過程中常用的采樣方式。本文將詳細(xì)介紹什么是中頻采樣和IQ采樣,以及它們之間的比較和轉(zhuǎn)換。 一、什么是中頻采樣? 中頻采樣又稱IF采樣,是在無線電接收機(jī)中廣泛用于對接收信號進(jìn)行數(shù)字化處理的一種采樣

2023-10-22 11:24:42 9677

9677

雙三次插值又叫雙立方插值,用于在圖像中“插值”(Interpolating)或增加“像素”(Pixel)數(shù)量/密度的一種方法。通常利用插值技術(shù)增加圖形數(shù)據(jù),以便在它打印或其他形式輸出的時(shí)候,能夠增大打印面積以及(或者)分辨率。

2023-12-14 14:35:57 2592

2592

示波器是通過內(nèi)部硬件ADC對模擬信號采樣來獲取離散的數(shù)據(jù)點(diǎn),然而這些離散的數(shù)據(jù)點(diǎn)有時(shí)難以完整呈現(xiàn)出原始模擬信號的全貌。軟件插值算法的意義就在于,它能夠依據(jù)特定的數(shù)學(xué)算法,在已采集的數(shù)據(jù)點(diǎn)之間插入新的數(shù)據(jù)點(diǎn),幫助使用者更好地還原和分析模擬信號的波形。最普遍的插值算法有線性插值和正弦插值兩種方式。

2024-12-24 16:11:52 2002

2002

電子發(fā)燒友App

電子發(fā)燒友App

評論