自中高端FPGA技術(shù)成熟以來(lái),FPGA+DSP/ARM架構(gòu)的硬件設(shè)計(jì)在眾多工業(yè)領(lǐng)域得到廣泛應(yīng)用。例如無(wú)線通信、圖像處理、工業(yè)控制、儀器測(cè)量等。

2025-10-15 10:39:02 3930

3930

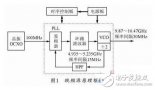

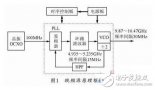

基于小數(shù)分頻鎖相環(huán)HMC704LP4設(shè)計(jì)了一種X波段跳頻源,具有相位噪聲低、雜散低、體積小的特點(diǎn)。針對(duì)指標(biāo)要求擬定設(shè)計(jì)方案,簡(jiǎn)述設(shè)計(jì)過(guò)程,給出設(shè)計(jì)參數(shù),對(duì)關(guān)鍵指標(biāo)進(jìn)行分析仿真,并給出測(cè)試曲線。

2013-10-22 10:36:54 9967

9967

本系統(tǒng)采用基于FPGA與DSP協(xié)同工作進(jìn)行視頻處理的方案,實(shí)現(xiàn)視頻采集、處理到傳輸的整個(gè)過(guò)程。

2014-10-23 15:35:49 6823

6823

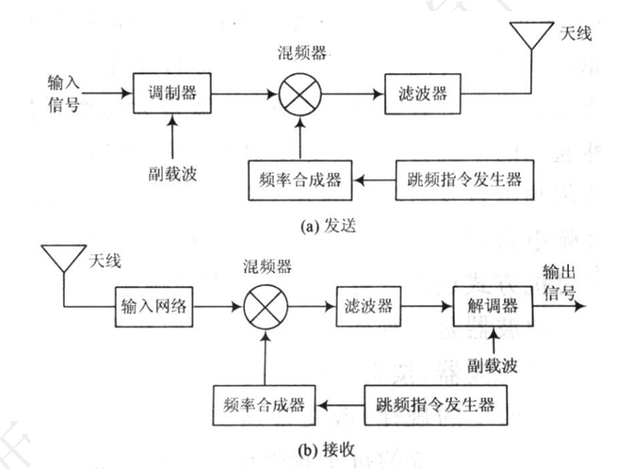

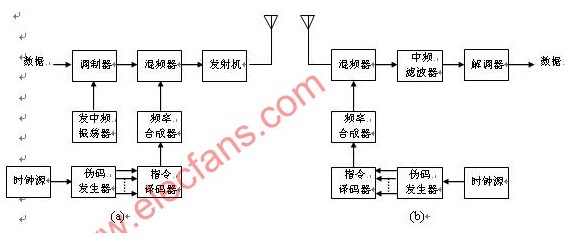

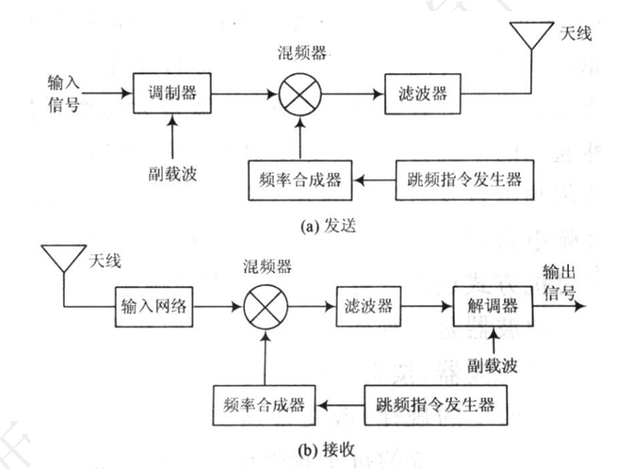

跳頻通信是一種載頻按照一定規(guī)律變化的多頻率移頻鍵控,具有抗干擾性強(qiáng)、保密性好、頻帶利用率高的特點(diǎn),易于兼容,便于構(gòu)成多種通信網(wǎng)。正是由于這些特點(diǎn),跳頻通信系統(tǒng)在現(xiàn)代軍事和交通運(yùn)輸通信中得到了廣泛

2021-06-14 14:24:00 4454

4454

跳頻功能)自組網(wǎng)電臺(tái)采用寬帶跳頻技術(shù),跳速1000-2000hop/s,跳頻帶寬大于200MHz,跳頻點(diǎn)可達(dá)256個(gè),具有很強(qiáng)的抗干擾和抗截獲通信能力 。 跳頻通信技術(shù)是在現(xiàn)代信息對(duì)抗日益激烈的形勢(shì)下迅速發(fā)展起來(lái)的,它具有很強(qiáng)的抗搜索、抗截獲、抗干擾能力

2023-08-28 09:11:47 3313

3313

本帖最后由 mr.pengyongche 于 2013-4-30 02:57 編輯

FPGA+DSP 在空中背景下運(yùn)動(dòng)目標(biāo)實(shí)時(shí)跟蹤系統(tǒng)中的應(yīng)用 摘要:針對(duì)電視跟蹤系統(tǒng)對(duì)飛行目標(biāo)的檢測(cè)與跟蹤受到速度瓶頸

2012-12-28 11:19:07

本人剛?cè)腴TFPGA,不知道如何實(shí)現(xiàn)FPGA+DSP,FPGA+ARM接口設(shè)計(jì),網(wǎng)上查詢有的說(shuō)FPGA+DSP可以通過(guò)EMIF,IP核實(shí)現(xiàn),FPGA+ARM可以通過(guò)SPI,有沒(méi)有具體硬件參考的?

2016-08-27 11:30:26

隨著同防工業(yè)對(duì)精確制導(dǎo)武器要求的不斷提高,武器系統(tǒng)總體設(shè)計(jì)方案的日趨復(fù)雜,以及電子元器件水平的飛速發(fā)展。導(dǎo)引頭信號(hào)處理器的功能越來(lái)越復(fù)雜,硬件規(guī)模越來(lái)越大.處理速度也越來(lái)越高.而且產(chǎn)品的更新速度加快

2019-08-30 06:31:29

設(shè)定為DSP核時(shí)鐘的8分頻,FPGA與DSP的實(shí)際數(shù)據(jù)傳輸率為62.5MBps。 (1) 接收部分:由編碼和緩存兩部分組成。由于鏈路口的數(shù)錯(cuò)是DDR形式的,不方便數(shù)據(jù)的緩存,本文

2019-06-21 05:00:04

本帖最后由 全都被注冊(cè)過(guò) 于 2015-8-14 23:15 編輯

fpga為主機(jī)向dsp傳數(shù),fpga的port initial會(huì)高低跳變,導(dǎo)致傳輸速度很慢(我認(rèn)為傳輸速度慢是因?yàn)槠?b class="flag-6" style="color: red">跳變導(dǎo)致的)是什么導(dǎo)致的port initial不停跳變?有人遇到過(guò)這種情況嗎?求教!

2015-08-14 18:47:58

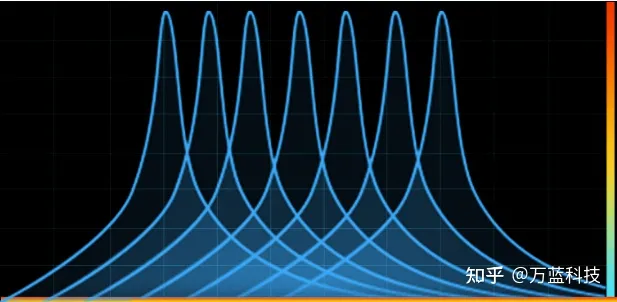

模擬和數(shù)字無(wú)線電中,跳頻被用來(lái)提高性能,避免檢測(cè)和減少干擾和干擾,如多徑和衰落。 跳頻與編碼方案結(jié)合使用,提高了從干擾和衰落中恢復(fù)信息的能力,在廣泛的頻譜范圍內(nèi)傳播信息,使系統(tǒng)更加健壯。如果一個(gè)特定

2021-12-29 09:31:37

我是通信專業(yè)學(xué),最近對(duì)跳頻通信技術(shù)感興趣,有沒(méi)有大神推薦一些介紹跳頻通信技術(shù)的文獻(xiàn)給我啊。 有沒(méi)有比較簡(jiǎn)單的跳頻器設(shè)計(jì)方案呢?

2013-04-06 23:01:08

本系統(tǒng)采用基于FPGA與DSP協(xié)同工作進(jìn)行視頻處理的方案,實(shí)現(xiàn)視頻采集、處理到傳輸的整個(gè)過(guò)程。實(shí)時(shí)視頻圖像處理中,低層的預(yù)處理算法處理的數(shù)據(jù)量大,對(duì)處理速度要求高,但算法相對(duì)比較簡(jiǎn)單,適合于用

2019-07-01 07:38:06

本人剛剛學(xué)習(xí)跳頻技術(shù),對(duì)跳頻技術(shù)不是很了解,現(xiàn)在想將跳頻技術(shù)與DSP進(jìn)行融合,不知道哪位大俠可以給我指點(diǎn)指點(diǎn)。希望哪位高手給我一份關(guān)于DSP驅(qū)動(dòng)DDS的例程,本人不勝感激!!!!!!!!

2012-10-20 17:14:08

跳頻通信系統(tǒng)作為擴(kuò)頻通信體制中的一種重要類型,以其出色的抗遠(yuǎn)近效應(yīng)、抗干擾能力,在軍用、民用通信領(lǐng)域得到了廣泛應(yīng)用。跳頻通信方式是指載波受一偽隨機(jī)碼的控制, 不斷地、隨機(jī)地跳變,可看成載波按照一定

2019-10-15 07:39:47

。近年來(lái)隨著半導(dǎo)體工藝和計(jì)算機(jī)技術(shù)的發(fā)展,dsp(Digital Signal Processor)、FPGA(Field Programmable Gates Array)等現(xiàn)代信號(hào)處理芯片越來(lái)越成熟和普遍使用,以前只能理論研究的跳頻技術(shù)有了實(shí)現(xiàn)的可能。

2019-08-28 07:13:20

。近年來(lái)隨著半導(dǎo)體工藝和計(jì)算機(jī)技術(shù)的發(fā)展,dsp(Digital Signal Processor)、FPGA(Field Programmable Gates Array)等現(xiàn)代信號(hào)處理芯片越來(lái)越成熟和普遍使用,以前只能理論研究的跳頻技術(shù)有了實(shí)現(xiàn)的可能。

2019-08-29 06:24:01

跳頻通信系統(tǒng)作為擴(kuò)頻通信體制中的一種重要類型,以其出色的抗遠(yuǎn)近效應(yīng)、抗干擾能力,在軍用、民用通信領(lǐng)域得到了廣泛應(yīng)用。

2019-10-16 08:03:45

本系統(tǒng)采用基于FPGA與DSP協(xié)同工作進(jìn)行視頻處理的方案,實(shí)現(xiàn)視頻采集、處理到傳輸的整個(gè)過(guò)程。 實(shí)時(shí)視頻圖像處理中,低層的預(yù)處理算法處理的數(shù)據(jù)量大,對(duì)處理速度要求高,但算法相對(duì)比較簡(jiǎn)單,適合于

2019-06-28 08:10:26

跳頻技術(shù)是一種具有高抗干擾性、高抗截獲能力的擴(kuò)頻技術(shù)。接收系統(tǒng)是跳頻通信系統(tǒng)中非常重要的部分,自適應(yīng)跳頻技術(shù)、高速跳頻技術(shù)、信道編碼技術(shù)、高效調(diào)制解調(diào)技術(shù)成為近年來(lái)跳頻技術(shù)發(fā)展的新動(dòng)態(tài),基于FPGA的跳頻通信接收系統(tǒng)研究有很高的應(yīng)用價(jià)值。

2019-09-25 06:15:14

圖像數(shù)據(jù)處理的工作原理是什么?基于FPGA+DSP的圖像處理系統(tǒng)待如何去設(shè)計(jì)?

2021-06-02 06:54:28

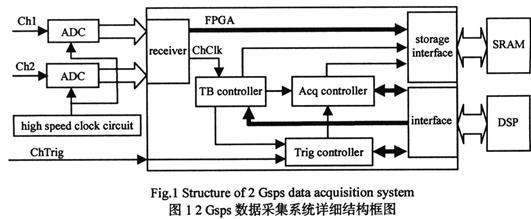

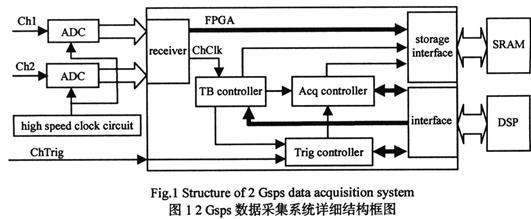

基于FPGA+DSP的高速數(shù)據(jù)采集系統(tǒng)設(shè)計(jì)

2012-06-27 17:23:53

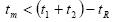

通信網(wǎng)位同步方案——隙同步的方法,并基于TI公司TMS320C54X系列DSP,采用TMS320匯編語(yǔ)言對(duì)隙同步方案進(jìn)行了硬件實(shí)現(xiàn)和分析。仿真結(jié)果表明:隙同步原理能較好地解決跳頻通信網(wǎng)中接收端的位同步

2021-07-16 07:00:00

該文檔為基于軟件無(wú)線電跳頻電臺(tái)射頻前端的研究總結(jié)文檔,是一份很不錯(cuò)的參考資料,具有較高參考價(jià)值

2023-09-25 07:56:29

隨著同防工業(yè)對(duì)精確制導(dǎo)武器要求的不斷提高,武器系統(tǒng)總體設(shè)計(jì)方案的日趨復(fù)雜,以及電子元器件水平的飛速發(fā)展。導(dǎo)引頭信號(hào)處理器的功能越來(lái)越復(fù)雜,硬件規(guī)模越來(lái)越大.處理速度也越來(lái)越高.而且產(chǎn)品的更新速度加快

2019-11-06 08:34:27

跳頻技術(shù)是一種具有高抗干擾性、高抗截獲能力的擴(kuò)頻技術(shù)。接收系統(tǒng)是跳頻通信系統(tǒng)中非常重要的部分,自適應(yīng)跳頻技術(shù)、高速跳頻技術(shù)、信道編碼技術(shù)、高效調(diào)制解調(diào)技術(shù)成為近年來(lái)跳頻技術(shù)發(fā)展的新動(dòng)態(tài),基于FPGA的跳頻通信接收系統(tǒng)研究有很高的應(yīng)用價(jià)值。

2019-09-30 08:11:55

隨著同防工業(yè)對(duì)精確制導(dǎo)武器要求的不斷提高,武器系統(tǒng)總體設(shè)計(jì)方案的日趨復(fù)雜,以及電子元器件水平的飛速發(fā)展。導(dǎo)引頭信號(hào)處理器的功能越來(lái)越復(fù)雜,硬件規(guī)模越來(lái)越大.處理速度也越來(lái)越高.而且產(chǎn)品的更新速度加快

2019-08-19 06:38:12

雖說(shuō)FPGA+DSP的數(shù)字硬件系統(tǒng)正好結(jié)合了兩者的優(yōu)點(diǎn),但有什么方法去證明FPGA+DSP系統(tǒng)中FPGA的關(guān)鍵技術(shù)是存在的呢?

2021-04-08 06:54:33

我想用FPGA+DSP做個(gè)聲相儀,有感興趣的小伙伴嗎?一起開(kāi)發(fā),在上海最好啦。先做原型機(jī)出來(lái),然后再考慮產(chǎn)品化。私聊:QQ 4010087

2017-04-25 14:53:48

在簡(jiǎn)要介紹跳頻通信技術(shù)的發(fā)展概況及跳頻源合成主要方法的基礎(chǔ)上,針對(duì)目前普遍采用的DDS 技術(shù),詳細(xì)分析了其輸出頻譜特性,并由此引出了基于DDS 的跳頻源設(shè)計(jì)方案,然后詳細(xì)

2009-01-07 10:44:34 10

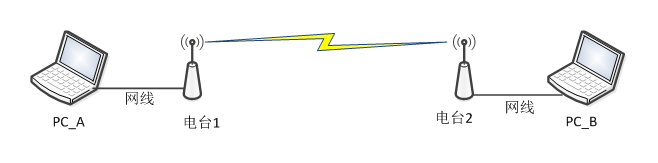

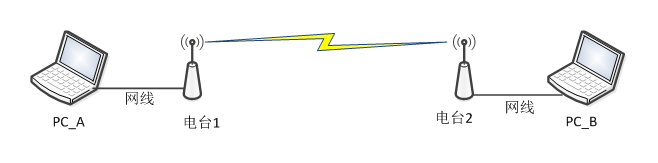

10 基于無(wú)線傳輸的模擬電臺(tái)訓(xùn)練系統(tǒng)設(shè)計(jì):針對(duì)當(dāng)前我軍通信裝備的業(yè) 務(wù)訓(xùn)練手段單一、效率低下等問(wèn)題,提出了某型電臺(tái)網(wǎng)絡(luò)模擬訓(xùn)練系統(tǒng)的總體設(shè)計(jì)方案以及無(wú)線語(yǔ)音、數(shù)據(jù)傳輸

2009-06-21 22:45:40 14

14 介紹了一種基于FPGA+DSP 的數(shù)據(jù)采集與處理平臺(tái),給出了系統(tǒng)實(shí)現(xiàn)的總體方案,并闡述了各部分硬件電路的設(shè)計(jì)。重點(diǎn)對(duì)FPGA 內(nèi)部各主要功能模塊做了詳細(xì)闡述,對(duì)各個(gè)模塊的設(shè)計(jì)方法

2009-12-19 15:59:16 34

34 簡(jiǎn)要分析了DSP+FPGA 系統(tǒng)的特點(diǎn)和優(yōu)越性,結(jié)合導(dǎo)引頭信號(hào)處理板的開(kāi)發(fā),提出了在此系統(tǒng)中,FPGA 設(shè)計(jì)的幾個(gè)關(guān)鍵技術(shù),并且給出了詳實(shí)的分析和解決方案。

2009-12-23 14:53:54 20

20 針對(duì)某機(jī)載電臺(tái)技術(shù)指標(biāo)的檢測(cè)控制需求以及該電臺(tái)激勵(lì)信號(hào)和響應(yīng)信號(hào)的特點(diǎn),提出一種以FPGA(EP1C12)作為控制核心,采用DDS(AD9850)+PLL(MC145152)數(shù)字頻率合成的跳頻信號(hào)發(fā)

2010-01-07 12:36:34 13

13 HFC傳輸系統(tǒng)的設(shè)計(jì)方案分析

由于我們的設(shè)計(jì)對(duì)象是一個(gè)“光纜、電纜CATV綜合網(wǎng)絡(luò)”,其傳輸網(wǎng)絡(luò)功能設(shè)計(jì)的指導(dǎo)思想應(yīng)該是:從目前的以“模擬”為主的“廣

2010-03-27 10:22:37 25

25 簡(jiǎn)要分析了DSP+FPGA系統(tǒng)的特點(diǎn)和優(yōu)越性,結(jié)合導(dǎo)引頭信號(hào)處理板的開(kāi)發(fā),提出了在此系統(tǒng)中,FPGA設(shè)計(jì)的幾個(gè)關(guān)鍵技術(shù),并且給出了詳實(shí)的分析和解決方案。

2010-07-21 17:28:04 18

18 闡述了跳頻通信以及多載波調(diào)制技術(shù)OFDM的特點(diǎn),并針對(duì)跳頻通信數(shù)據(jù)傳輸速率有限的局限性,在運(yùn)用高性能DSP處理器的基礎(chǔ)上,采用OFDM技術(shù)與跳頻通信技術(shù)相結(jié)合的方法來(lái)提高跳頻

2010-08-05 11:34:12 22

22 軟件無(wú)線電臺(tái)是軟件無(wú)線電技術(shù)在通信電臺(tái)中的應(yīng)用。隨著自適應(yīng)跳頻技術(shù)的發(fā)展,自適應(yīng)跳頻技術(shù)在軍事通信中得到越來(lái)越大的應(yīng)用,本文就基于軟件無(wú)線電的自適應(yīng)跳頻系統(tǒng)進(jìn)

2010-08-09 14:51:14 16

16 擴(kuò) 展 頻譜 通信是一種新的通信方式。跳頻通信是擴(kuò)展頻譜通信中的一種.跳頻通信、擴(kuò)展頻譜通信、自適應(yīng)通信及高速數(shù)字?jǐn)?shù)據(jù)通信系統(tǒng)為“90年代的通信技術(shù)”。由于擴(kuò)展頻

2010-08-20 16:49:29 18

18 同步技術(shù)是跳頻通信系統(tǒng)的關(guān)鍵技術(shù)之一,尤其是在快速跳頻通信系統(tǒng)中,常規(guī)跳頻通信通過(guò)同步字頭攜帶相關(guān)碼的方法來(lái)實(shí)現(xiàn)同步,但對(duì)于快跳頻來(lái)說(shuō),由于是一跳或者多跳傳輸

2010-11-22 15:58:14 34

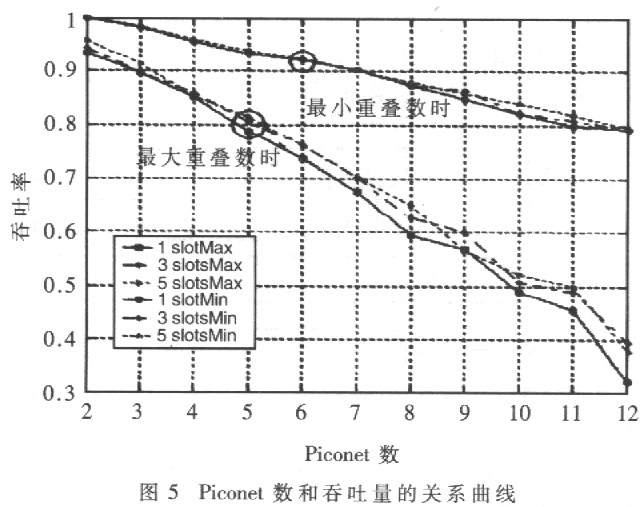

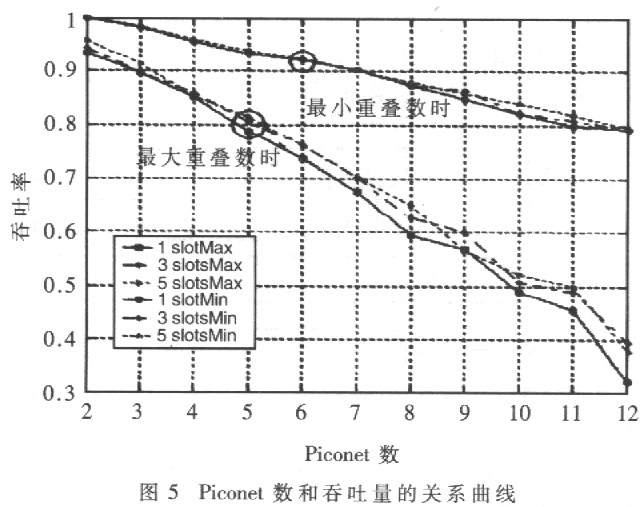

34 Bluetooth跳頻網(wǎng)絡(luò)Piconet聞干擾分析研究

摘要:分析了藍(lán)牙微微網(wǎng)間不同跳頰區(qū)段工作原理,以及不同區(qū)段跳頻碰撞數(shù)對(duì)實(shí)際吞吐量的影響,提出了不同微微網(wǎng)問(wèn)跳頻區(qū)段

2008-10-13 14:48:32 1581

1581

快速跳頻無(wú)線電臺(tái)用時(shí)鐘

要使“極好”的跟蹤干擾臺(tái)失去作用,要求跳頻速率

2008-11-24 12:42:04 1186

1186

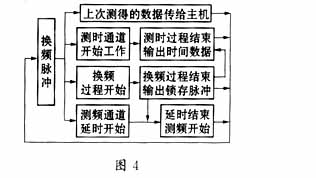

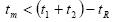

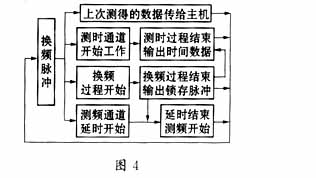

介紹了用等精度測(cè)頻和內(nèi)插技術(shù)來(lái)提高快速測(cè)頻精度的原理,說(shuō)明了基于此項(xiàng)技術(shù)對(duì)現(xiàn)有的跳頻電臺(tái)的檢測(cè)方法,給出了檢測(cè)過(guò)程的具體說(shuō)明。

2009-05-06 20:27:16 1361

1361

跳頻擴(kuò)頻通信系統(tǒng)

跳頻擴(kuò)頻通信系統(tǒng)是頻率跳變擴(kuò)展頻譜通信系統(tǒng)(Frequecy Hopping Spread Spectrum Communication Systems,F(xiàn)H-SS)的簡(jiǎn)稱,或

2009-05-22 01:23:43 5589

5589

從技術(shù)實(shí)現(xiàn)的角度而言,GSM中的跳頻的實(shí)現(xiàn)分為基帶跳頻、射頻跳頻兩種。

2009-07-29 16:12:28 891

891 基于FPGA的視頻傳輸流發(fā)送系統(tǒng)設(shè)計(jì)方案

1 引言

在目前的廣播電視系統(tǒng)中ASI接口是使用非常廣泛的一種接口形式,該接口隨同SPI一起被歐

2009-12-14 09:39:33 1567

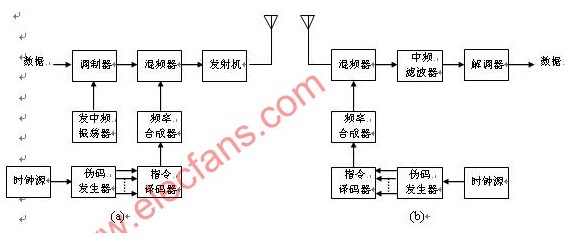

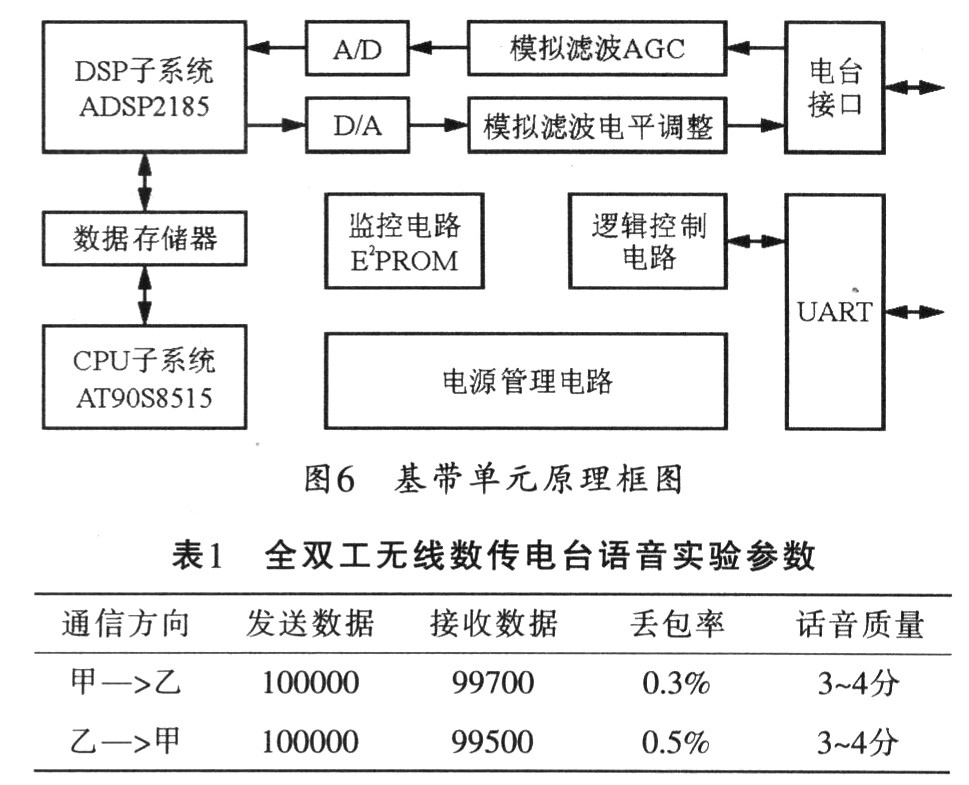

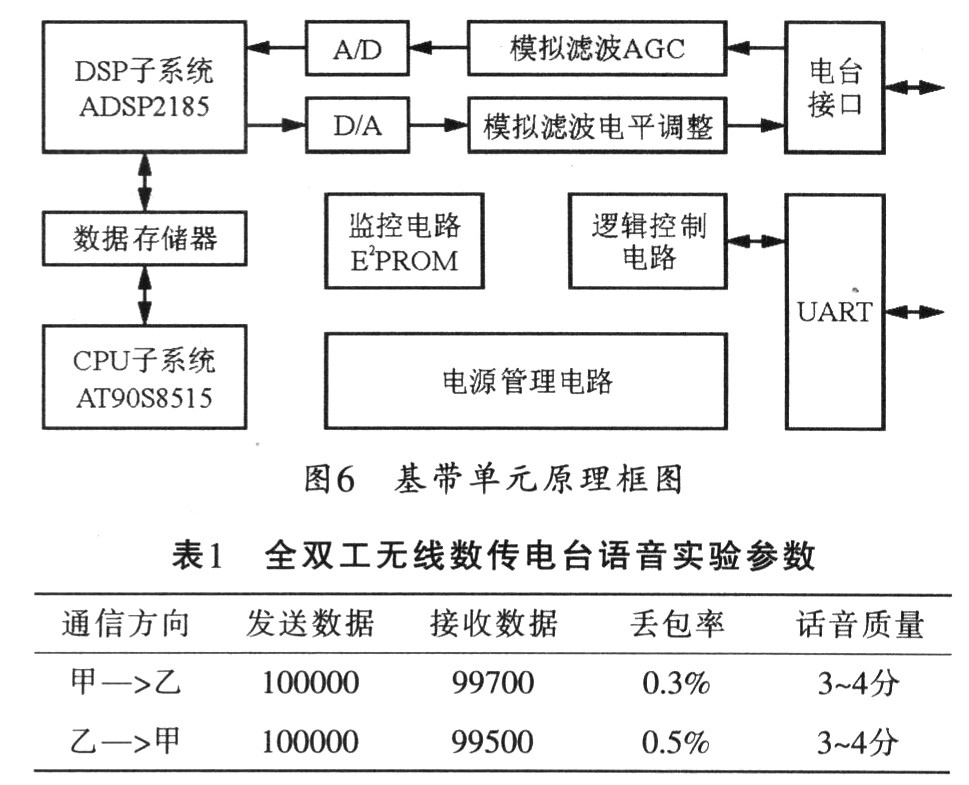

1567 全雙工無(wú)線數(shù)傳電臺(tái)設(shè)計(jì)方案

0 引言

數(shù)傳電臺(tái)在工業(yè)控制領(lǐng)域的應(yīng)用已經(jīng)十分廣泛,目前仍然是工業(yè)控制領(lǐng)域的主要傳輸手段。無(wú)線數(shù)傳

2009-12-25 09:49:01 2946

2946

摘要:在FPGA+DSP構(gòu)建的便件平臺(tái)上,以鏈路口(LINKPORT)通信協(xié)議為根據(jù),實(shí)現(xiàn)紅外圖像數(shù)據(jù)采集與顯示。重點(diǎn)描述紅外圖像數(shù)據(jù)采集與經(jīng)過(guò)LINKPORT傳入DSP,圖像壓縮與經(jīng)過(guò)LINKPORT傳出DSP以及圖像數(shù)據(jù)緩存與顯示,最后介紹了程序高度過(guò)程中的方法。樣機(jī)在實(shí)

2011-03-01 00:11:12 89

89 針對(duì)跳頻通信對(duì)信道編碼要求較高的問(wèn)題!提出了混合糾錯(cuò)方式的RS碼和重傳反饋方式相級(jí)連的方法!主要研究了RS碼的編碼解碼過(guò)程以及ARQ 協(xié)議的DSP實(shí)現(xiàn).

2011-05-16 17:33:19 51

51 摘要: 基于 軟件無(wú)線電 的基本要求和發(fā)展趨勢(shì),提出了一種應(yīng)用在軟件無(wú)線電跳頻電臺(tái)中寬頻段接收機(jī)的前端電路設(shè)計(jì)方案,分析了接收機(jī)射頻前端二次混頻方案結(jié)構(gòu)的可行性,在對(duì)

2011-06-08 11:13:02 80

80 跳頻通信系統(tǒng)是具有保密和抗干擾能力、可多址聯(lián)絡(luò)、機(jī)動(dòng)靈活的無(wú)線通信系統(tǒng)。廣泛應(yīng)用于軍警、交通運(yùn)輸、商業(yè)等專用通信網(wǎng)。l 跳頻控制器(以下簡(jiǎn)稱跳控器)是跳頻電臺(tái)的核心

2011-10-13 16:42:55 43

43 本書(shū)系統(tǒng)地闡述了跳頻序列設(shè)計(jì)、跳頻頻率合成、跳頻同步和跳頻組網(wǎng)等技術(shù),既包含了作者的研究成果,同時(shí)也總結(jié)了國(guó)內(nèi)外學(xué)者在跳頻通信取得的進(jìn)展,是國(guó)內(nèi)第一部系統(tǒng)闡述跳頻

2011-12-21 10:09:12 0

0 為了提高同步過(guò)程的建立速度和穩(wěn)定性,分析并比較了同步過(guò)程的實(shí)現(xiàn)方法,選擇了適合的同步方法,并進(jìn)一步設(shè)計(jì)了幀結(jié)構(gòu)、組網(wǎng)時(shí)隙分配方法等關(guān)鍵技術(shù)。根據(jù)本跳頻電臺(tái)特有的時(shí)

2012-04-06 15:28:30 26

26 介紹某超高速跳頻通信系統(tǒng)基帶部分的設(shè)計(jì)與實(shí)現(xiàn),該系統(tǒng)選用2FSK調(diào)制方式,并選擇合適跳頻頻帶以抑制鏡像頻率;討論了跳頻器、跳頻序列、快速位同步以及跳頻圖案同步以及跳

2012-06-04 16:25:41 2192

2192

同步技術(shù)是跳頻系統(tǒng)的核心。本文針對(duì)FPGA的跳頻系統(tǒng),設(shè)計(jì)了一種基于獨(dú)立信道法,同步字頭法和精準(zhǔn)時(shí)鐘相結(jié)合的快速同步方法,同時(shí)設(shè)計(jì)了基于雙圖案的改進(jìn)型獨(dú)立信道法,同步算

2013-05-06 14:09:20 22

22 基于FPGA+DSP實(shí)時(shí)圖像采集處理系統(tǒng)設(shè)計(jì)

2017-01-03 11:41:35 9

9 數(shù)字電路設(shè)計(jì)方案中DSP與FPGA的比較與選擇

2017-01-18 20:39:13 15

15 基于DSP和FPGA的多頻聲納采集系統(tǒng)設(shè)計(jì)_劉寅

2017-03-19 11:45:23 1

1 FPGA和Si4463的跳頻語(yǔ)音通信系統(tǒng)設(shè)計(jì)與實(shí)現(xiàn)

2017-08-31 11:05:53 15

15 1 引言 隨著航空航天技術(shù)的發(fā)展,圖像無(wú)線傳輸技術(shù)日趨成熟。而嵌入式圖像無(wú)線傳輸技術(shù)以其安裝方便、靈活、適合廣泛普及等優(yōu)點(diǎn)在廣大領(lǐng)域備受關(guān)注。本文介紹一種基于DSP的無(wú)線圖像傳輸系統(tǒng)的設(shè)計(jì)方案與實(shí)現(xiàn)

2017-10-24 10:44:19 11

11 所處理的數(shù)據(jù)量少,算法結(jié)構(gòu)復(fù)雜,適于運(yùn)算速度快,尋址靈活的DSP數(shù)字信號(hào)處理器進(jìn)行處理。這里提出了一種FPGA+DSP相結(jié)合的實(shí)時(shí)圖像處理系統(tǒng),并應(yīng)用于傳像光線束傳遞圖像。CMOS實(shí)際采集的是光線束的出端圖像,FPGA將CMOS采集的Bayer格式的

2017-10-26 15:44:56 3

3 所處理的數(shù)據(jù)量少,算法結(jié)構(gòu)復(fù)雜,適于運(yùn)算速度快,尋址靈活的DSP數(shù)字信號(hào)處理器進(jìn)行處理。這里提出了一種FPGA+DSP相結(jié)合的實(shí)時(shí)圖像處理系統(tǒng),并應(yīng)用于傳像光線束傳遞圖像。CMOS實(shí)際采集的是光線束的出端圖像,FPGA將CMOS采集的Bayer格式的

2017-10-31 17:00:34 14

14 基于DSP的無(wú)線圖像傳輸系統(tǒng)的設(shè)計(jì)方案與實(shí)現(xiàn)方法。 2 系統(tǒng)總體設(shè)計(jì)方案 圖1為該系統(tǒng)設(shè)計(jì)框圖。該系統(tǒng)分為圖像采集、圖像數(shù)據(jù)處理及無(wú)線通信3個(gè)模塊。圖像采集完成圖像數(shù)據(jù)的采集;圖像處理實(shí)現(xiàn)圖像數(shù)據(jù)的壓縮及相關(guān)處理:無(wú)線通信傳輸壓縮

2017-11-01 10:12:35 10

10 1、設(shè)計(jì)摘要 本設(shè)計(jì)定位為一話音跳頻通信系統(tǒng),采用 Logistic混沌系統(tǒng)產(chǎn)生跳頻序列,同時(shí)采用一種同步字頭法與等待跟蹤法相結(jié)合的新型同步方案動(dòng)態(tài)雙頻同步方案實(shí)現(xiàn)同步。理論分析和仿真試驗(yàn)均表明該

2017-11-14 10:28:53 26

26 采用MSK 調(diào)制的跳頻通信具有主瓣能量集中、旁瓣衰落滾降快、頻譜利用率高和抗干擾能力強(qiáng)等優(yōu)點(diǎn),在軍事通信中應(yīng)用廣泛。如美軍現(xiàn)役的聯(lián)合戰(zhàn)術(shù)信息分發(fā)系統(tǒng)采用的通信信號(hào),工作帶寬969~1 206 MHz

2017-11-24 19:02:42 2618

2618

跳頻通信是軍事通信的主要手段之一,因此在復(fù)雜的通信環(huán)境下保證跳頻通信系統(tǒng)的正常工作就變得十分重要。文章首先介紹了跳頻系統(tǒng),并給出了跳頻系統(tǒng)整體仿真圖。其次分析了跳頻系統(tǒng)中常見(jiàn)的幾種干擾,主要包括

2017-12-26 15:26:15 1

1 本文主要介紹了一種基于FPGA+DSP的視頻控制的智能交通燈設(shè)計(jì)。該交通燈由視頻采集、圖像處理和控制模塊組成,使用FPGA核心搭建專用高速視頻采集模塊,使用DSP處理器進(jìn)行實(shí)時(shí)圖像運(yùn)算,通過(guò)圖像算法提取車流量信息,最終結(jié)合模糊算法實(shí)現(xiàn)智能控制。

2018-01-09 14:15:41 2686

2686

無(wú)線電能傳輸是一種方便、安全的電能傳輸方式。以實(shí)現(xiàn)蓄電池快速無(wú)線充電的串聯(lián)一串聯(lián)( SS)型諧振無(wú)線電能傳輸系統(tǒng)為研究對(duì)象,設(shè)計(jì)蓄電池三段式充電曲線,提出一種與之相對(duì)應(yīng)的分段跳頻控制策略。根據(jù)蓄電池

2018-01-16 13:31:36 1

1 本設(shè)計(jì)定位為一話音跳頻通信系統(tǒng),采用 Logistic混沌系統(tǒng)產(chǎn)生跳頻序列,同時(shí)采用一種同步字頭法與等待跟蹤法相結(jié)合的新型同步方案——?jiǎng)討B(tài)雙頻同步方案實(shí)現(xiàn)同步。理論分析和仿真試驗(yàn)均表明該方案實(shí)現(xiàn)方法

2018-04-18 11:37:00 9969

9969

本文檔內(nèi)容介紹了MDO跳頻測(cè)試方案應(yīng)用,供參考

2018-03-14 17:06:13 1

1 本文采用ADC+高頻時(shí)鐘電路+FPGA+DSP的結(jié)構(gòu)模式,設(shè)計(jì)了一種實(shí)時(shí)采樣率為2 Gsps的數(shù)字存儲(chǔ)示波器數(shù)據(jù)采集系統(tǒng),為國(guó)內(nèi)高速高分辨率的數(shù)據(jù)采集系統(tǒng)的研制提供了一個(gè)參考方案。

2019-05-03 09:19:00 7263

7263

相關(guān)差分跳頻(DFH)通信是近年出現(xiàn)的跳頻通信方式。美國(guó)Sanders公司研制的相關(guān)跳頻增強(qiáng)擴(kuò)譜CHESS電臺(tái)就采用這種差分跳頻技術(shù),實(shí)現(xiàn)了在短波波段5 000跳/秒的跳頻速率和最高19.2 kbit·s-1的數(shù)傳速率。

2018-12-26 09:32:00 7846

7846

FPGA+DSP的數(shù)字硬件系統(tǒng)正好結(jié)合了兩者的優(yōu)點(diǎn),兼顧了速度和靈活性。本文以導(dǎo)引頭信號(hào)處理系統(tǒng)為例說(shuō)明FPGA+DSP系統(tǒng)中FPGA的關(guān)鍵技術(shù)。

2019-01-08 08:36:00 3785

3785

高速中頻采樣信號(hào)處理平臺(tái)在實(shí)際應(yīng)用中有很大的前景,提出采用FPGA+DSP的處理結(jié)構(gòu),結(jié)合高性能A/D和D/A處理芯片,設(shè)計(jì)了一個(gè)通用處理平臺(tái),并對(duì)其主要性能進(jìn)行了測(cè)試。

2018-10-18 16:36:48 5708

5708

本文根據(jù)單峰映射產(chǎn)生混沌序列極易被攻擊的特點(diǎn),采用髙維的混沌系統(tǒng)來(lái)設(shè)計(jì)混沌跳頻序列發(fā)生器。針對(duì)n維非線性數(shù)字濾波器產(chǎn)生序列的周期和分布特性,我們?cè)?b class="flag-6" style="color: red">系統(tǒng)結(jié)構(gòu)上作了相應(yīng)的設(shè)計(jì),并最終應(yīng)用FPGA(現(xiàn)場(chǎng)

2021-02-02 15:14:55 11

11 介紹了一種應(yīng)用于淺海的基于定點(diǎn)DSP的跳頻水聲遙控通訊及控制技術(shù)。在淺海環(huán)境水聲信道的多途效應(yīng)造成水聲通訊質(zhì)量急劇下降的情況下,利用跳頻編碼抗多途干擾的優(yōu)勢(shì)及υSP芯片強(qiáng)大的實(shí)時(shí)數(shù)據(jù)處理功能,實(shí)現(xiàn)低誤碼率的水聲遙控和控制。目前該技術(shù)已成功地應(yīng)用于相關(guān)試驗(yàn)控制系統(tǒng)中。

2021-05-07 09:37:18 6

6 車載超短波電臺(tái)維修檢測(cè)系統(tǒng)設(shè)計(jì)方案

2021-06-22 11:27:29 33

33 基于FPGA+DSP的高精度數(shù)字電源數(shù)據(jù)采集系統(tǒng)設(shè)計(jì)(開(kāi)關(guān)電源技術(shù)發(fā)展綜述)-該文檔為基于FPGA+DSP的高精度數(shù)字電源數(shù)據(jù)采集系統(tǒng)設(shè)計(jì)講解文檔,是一份不錯(cuò)的參考資料,感興趣的可以下載看看,,,,,,,,,,,,,,,,,

2021-09-24 11:32:01 36

36 FPGA+DSP的高精度數(shù)字電源數(shù)據(jù)采集系統(tǒng)設(shè)計(jì)(電源技術(shù)是什么檔次的期刊)-為基于FPGADSP的高精度數(shù)字電源數(shù)據(jù)采集系統(tǒng)設(shè)計(jì)講解文檔摘 要:提出了一種新的基于FPGA+DSP的高精度數(shù)字化電源

2021-09-27 11:16:45 19

19 基于FPGA+DSP彈載SAR信號(hào)處理系統(tǒng)設(shè)計(jì)

2021-12-27 18:58:51 21

21 高性能跳頻抗干擾寬帶自組網(wǎng)電臺(tái)

2022-03-02 14:15:04 4070

4070

HANHGK遠(yuǎn)距離的MESH跳頻自組網(wǎng)設(shè)備,基于FPGA方案的寬帶跳頻技術(shù),采用COFDM、分集接收、動(dòng)態(tài)TDMA、智能路由協(xié)議和寬帶跳頻抗干擾等技術(shù)開(kāi)發(fā)研制的高性能IP Mesh自組網(wǎng)產(chǎn)品針對(duì)各種

2022-03-30 14:07:20 2827

2827 測(cè)試100km視距條件下,T3S2-20W寬帶跳頻自組網(wǎng)電臺(tái)在定頻、選頻、跳頻模式下帶寬分別為5MHz、10MHz、20MHz時(shí)的的TCP灌包速率,尤其關(guān)注遠(yuǎn)距離條件下跳頻模式的傳輸速率。

2022-05-09 16:57:59 2002

2002

電子發(fā)燒友網(wǎng)站提供《基于FPGA+DSP模式的智能相機(jī)設(shè)計(jì).pdf》資料免費(fèi)下載

2023-10-08 10:37:16 3

3 電子發(fā)燒友網(wǎng)站提供《基于軟件無(wú)線電跳頻電臺(tái)射頻前端的研究.pdf》資料免費(fèi)下載

2023-10-26 14:30:49 5

5 FPGA+DSP核心板是基于中科億海微EQ6HL130型FPGA芯片搭配國(guó)產(chǎn)DSP開(kāi)發(fā)的高性能核心板卡。對(duì)外接口采取郵票孔連接方式,可以極大提高信號(hào)傳輸質(zhì)量和焊接后的機(jī)械強(qiáng)度。核心板卡的系統(tǒng)框圖如下

2025-06-20 14:12:22 912

912

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論