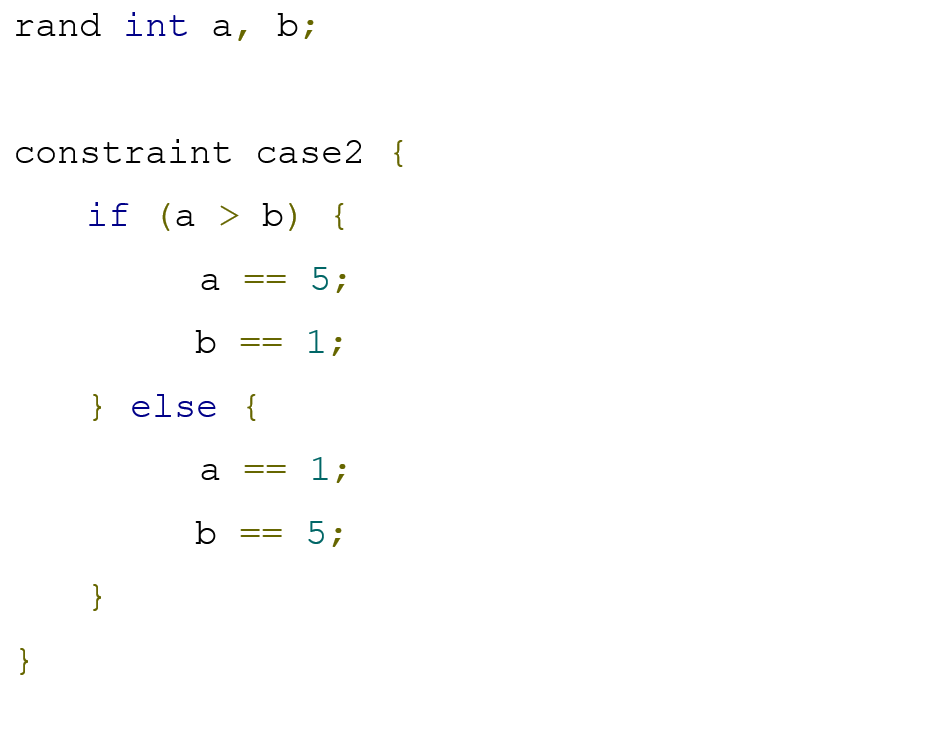

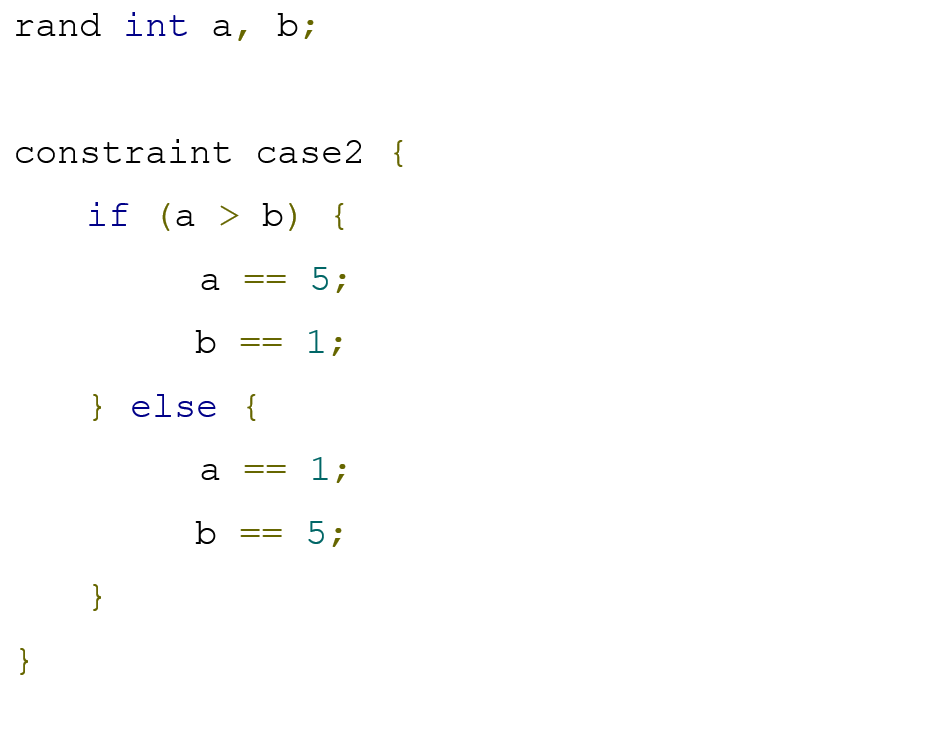

摘 要 隨著硬件設計復雜度的激增,驗證已被廣泛認為是制約整個芯片設計流程的瓶頸。基于仿真的驗證通常通過生成一系列滿足特定布爾/位向量約束的隨機激勵驗證設計行為。在該驗證方法學中,驗證效率很大程度

2023-06-06 10:28:51 1035

1035

為了擴展VME總線和CAN總線的應用范圍,充分利用兩種總線的不同傳輸特點,采用了模塊設計方法,提出一種基于FPGA和MCU的總線轉換方案。該方案給出了FPGA與上位VME總線部分的VME總線接口

2019-06-28 08:24:19

摘要:為了實現對非相干雷達的接收相參處理,基于數字穩定校正(DSU)的原理,采用ALTERA公司的StratixⅡ系列芯片和VHDL編程語言,設計了一種基于FPGA的DSU硬件實現方法。實驗結果表明

2019-06-28 08:27:33

摘要:UART作為RS232協議的控制接口得到了廣泛的應用,將UART的功能集成在FPGA芯片中,可使整個系統更為靈活、緊湊,減小整個電路的體積,提高系統的可靠性和穩定性。提出了一種基于FPGA

2019-06-21 07:17:24

摘 要:提出了一種基于FPGA的任意鎖相倍頻算法。通過對倍頻系統總體結構的分析,提出了實現該算法的原理及其具體的設計方法,同時提供了一個基于FPGA器件完成的設計實例。仿真和實測結果表明了該算法的正確性及可實現性,并在實際的項目中驗證了該算法的良好性能。

2013-12-04 22:29:00

中,數字信號處理系統經常要進行高速、高精度的FFF運算。現場可編程邏輯陣列(FPGA)是一種可定制集成電路,具有面向數字信號處理算法的物理結構。用FPGA實現FFT處理器具有硬件系統簡單、功耗低的優點

2019-07-03 07:56:53

實時采集、高精度測量等。FPGA的特點是完全由用戶通過軟件進行配置和編程,從而完成某種特定的功能,且可以反復擦寫,因此,以FPGA為核心進行電路搭建已成為當前數字系統設計的主流方法。本文利用FPGA設計了一種多通道頻率測量系統,易于擴展,精度較高,符合實際的需求。

2019-06-27 07:23:11

在單片FPGA芯片上實現數據傳輸、姿態解算和位置解算等功能的導航解算系統,節省了小型無人機寶貴的空間和成本,提出了一種導航信息的FPGA并行解算方法,充分發揮FPGA的并行數據處理能力提高解算速度,一次導航解算過程只需20微秒。

2019-07-03 06:57:34

本文概述了開發這種系統所必須面對的各種設計挑戰,并講解了Altium公司的最新電子設計環境Nexar如何為FPGA設計提供一種全新的方法。這種方法不僅可將處理器有效地集成入FPGA之中,而且成為一種挖掘現有以及未來大容量、低成本FPGA部件應用潛力的系統級

2021-05-08 06:02:24

本文提出了一種基于嵌入式系統和Internet的FPGA動態配置方案。

2021-05-27 06:38:55

求大佬介紹一種基于現場可編程門陣列(FPGA)的同步方案?

2021-04-08 06:25:03

分享一種具有低功耗意識的FPGA設計方法

2021-04-29 06:15:55

本文介紹了一種基于FPGA利用VHDL硬件描述語言的數字秒表設計方法,

2021-05-11 06:37:32

電源解決方案那么,如何才能簡化設計呢?幸運的是,有多種解決方案都有助于實現簡化。在本文中,我將重點介紹兩種能夠幫助您快速便捷地實現設計目標的創新技術。第一種需要著重介紹的技術是用于創建 FPGA

2019-06-03 09:14:17

本文提出了一種基于FPGA的NoC驗證平臺。詳細討論了該驗證平臺中FPGA硬件平臺和NoC軟件的基本功能,并闡述了TG/R,MPU,MPI以及NoC軟件的可重用性等特點。通過一個實例仿真驗證的結果說明了該驗證平臺的基本功能和優越性。

2021-05-06 07:20:48

本文介紹一種以FPGA為核心,設計了一種基于FPGA的數字秒表?

2021-05-10 06:40:32

STM32開發板的硬件部分有哪些?STM32開發板的軟件部分有哪些?怎樣去新建一種基于庫函數的工程?

2021-08-12 06:22:09

我想在任何FPGA設計完成之前為VCCINT / VCCO / VCCAUX構建一個穩壓器。是否有一種智能方法可以準確估算FPGA的功耗?以上來自于谷歌翻譯以下為原文I'm trying

2019-05-21 06:58:03

OLED簡介及特點一種OLED顯示屏顯示漢字的硬件配置和軟件設計方法

2021-04-22 06:19:25

本文根據FPGA的結構特點,圍繞在FPGA上設計實現八位微處理器軟核設計方法進行探討,研究了片上系統的設計方法和設計復用技術,并給出了指令集和其調試方法,提出了一種基于FPGA的微處理器的IP的設計方法。

2021-04-29 06:38:37

本文主要研究了一種基于FPGA、自頂向下、模塊化、用于提取位同步時鐘的全數字鎖相環設計方法。

2021-05-06 08:00:46

本文介紹了一種基于FPGA芯片的高速智能節點的硬件結構和軟件設計,旨在提高現在LON網絡的智能節點的處理能力和通用性。

2021-05-06 08:20:28

遠程在線更新FPGA程序系統的硬件結構是怎樣構成的?怎樣去設計一種遠程在線更新FPGA程序系統?

2021-06-18 09:16:18

本文基于某車型門窗控制器(DCM:Door Control Module)的PCBA提出一種有限元分析中PCBA的簡化建模方法,并進行有限元仿真模態分析。通過仿真模態分析結果與試驗模態分析結果對比,驗證所提出的簡化建模方法計算結果的準確性。

2021-04-19 06:20:44

本文提出一種精簡的FPGA的編程電路,很適合大規模地在便攜式小型儀表產品中應用。

2021-04-30 07:05:39

求大神分享一種高檔FPGA可重構配置方法

2021-04-29 06:16:54

求大佬分享一種基于FPGA的NAND FLASH控制器的設計方法?

2021-05-08 07:46:27

求大佬分享一種基于FPGA的OLED真彩色動態圖像顯示的實現方法

2021-06-01 06:38:14

萌新求助,求一種DSP硬件驅動開發方法

2021-10-22 06:53:30

本文介紹了一種FPGA和IPX2805之間的SPI4.2接口模塊設計的方法,對硬件設計進行了說明,著重闡述了FPGA內部SPI4.2接口模塊設計。

2021-05-06 09:22:44

介紹DES的密鑰算法,提出一種用預計算簡化密鑰計算的方法并公布了預計算的C語言源程序。這種方法對 DES的硬件實現有非常好的簡化效果。

2009-04-07 09:41:55 14

14 通過定義節點編碼圖概念,提出一種不需要拓撲排序的求解關鍵路徑的新算法。該算法擴充圖的鄰接表的存儲結構,使圖的存儲與算法求解過程共享同一存儲空間。從圖的源節點開

2009-04-23 10:29:25 7

7 針對變換域通信系統,提出了一種采用雙m序列控制的基函數相位映射方法,分析、仿真了所產生的不同基函數的相關性與時域隨機性等性能與特點。采用所提出的基函數生成方法

2009-05-12 21:46:28 13

13 本文提出了一種求解非線性約束優化的全局最優的新方法—它是基于利用非線性互補函數和不斷增加新的約束來重復解庫恩-塔克條件的非線性方程組的新方法。因為庫恩-塔克條

2009-08-11 10:53:17 16

16 本文討論了一種可在FPGA 上實現的FFT 結構。該結構采用基于流水線結構和快速并行乘法器的蝶形處理器。乘法器采用改進的Booth 算法,簡化了部分積符號擴展,使用Wallace 樹結構和4-2

2009-09-11 15:46:40 16

16 一種求解電大平臺天線互耦的時域積分方程快速算法:該文針對電大尺寸平臺天線互耦問題,提出一種基于幾何繞射理論加速的時域積分方程快速算法。在求解時域積分方程的經典時

2009-10-29 13:01:52 26

26 一種帶狀線定向耦合器場分布的求解:通過兩次利用Schwarz-Christoffel變換函數,先把理想的帶狀線變換到實軸上,然后再變換成為平板電容器,得到與兩次變換過程相對應的兩個變換函

2009-11-01 14:59:17 17

17 一種基于FPGA的圖像中值濾波器的硬件實現:隨著超大規模集成電路(VLSI) 技術的不斷發展,圖像的并行處理技術也得到飛速發展。現場可編程門陣列(FPGA) 是在專用集成電路(ASIC) 的基礎

2009-11-01 15:18:41 31

31 一種解決函數優化問題的免疫算法:介紹了免疫算法的基本概念,以及人工免疫系統中的克隆選擇原理,基于該原理,結合遺傳策略中的高斯變異算子,提出一種免疫算法來解決函數

2009-11-08 16:47:38 14

14 介紹了一種基于FPGA+DSP 的數據采集與處理平臺,給出了系統實現的總體方案,并闡述了各部分硬件電路的設計。重點對FPGA 內部各主要功能模塊做了詳細闡述,對各個模塊的設計方法

2009-12-19 15:59:16 34

34 本文實現了一種基于ARM-Linux 的FPGA 程序加載方法,詳細討論了加載過程中各個階段程序對配置管腳的操作,給出了硬件實現,編寫了運行于ARM 處理器的嵌入式Linux上的驅動程序。

2009-12-19 16:26:26 31

31 本文提出估計白噪聲中一個或多個復指數序列的參數(復指數序列的頻率和功率、白噪聲的方差)的一種新方法,該方法根據數據的2p個自相關函數值,相繼求解兩個線性方程組,即可

2010-01-12 18:56:56 15

15 GPS RTK轉換參數求解方法摘要:GPS RTK 技術是目前測量中具有定位快速, 精度高的一種先進的測量方法. 主要介紹了RTK 在應用過程中求解轉換參數的方法, 著重對求解

2010-04-26 11:33:47 71

71 一種硬件細分方法的研究與應用

對光柵傳感器原始信號進行細分是采用各類光柵器件進行高精度位置測量、角度測量過程中不可或缺的一個環節。細分方法多種多樣,

2009-05-04 21:45:14 612

612 一種密鑰可配置的DES加密算法的FPGA

摘 要: 在傳統的DES加密算法的基礎上,提出一種對密鑰實行動態管理的硬件設計方案,給出了其FPGA實現方法。通過對DES加密

2009-09-19 09:14:05 1348

1348

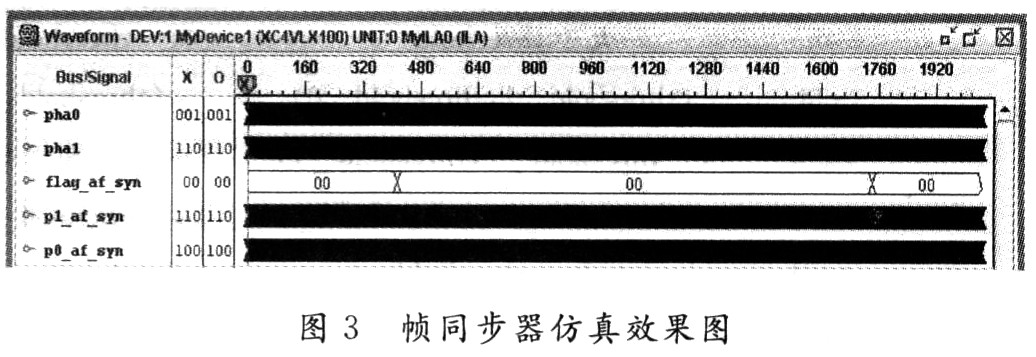

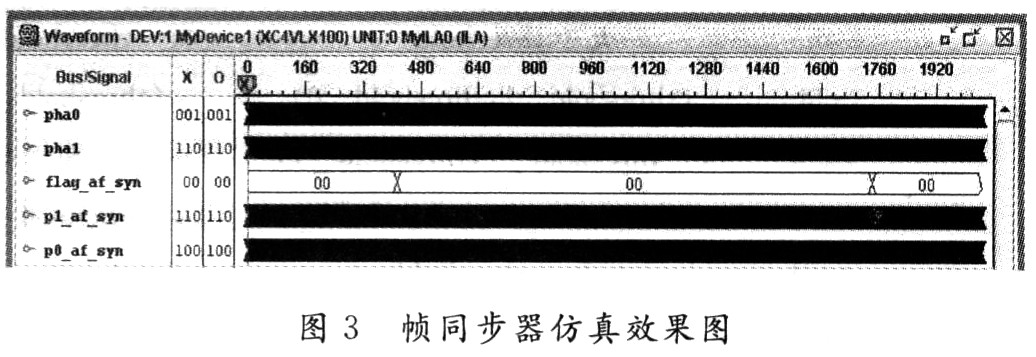

一種高速幀同步和相位模糊估計的方法及其FPGA實現

摘要:提出僅依靠接收符號和本地同步碼快速確定MPSK調制符號的幀同步,并同時估計其相位模糊值的計算方法,給

2010-01-27 09:38:17 1833

1833

基于現場可編程(FPGA)技術和硬件描述語言VHDL的設計和綜合,通過自頂向下的設計方法和模塊化設計思想,在Quartus II環境下能定制、仿真、下載驗證和實現CPU功能。通過VHDL語言定制了運算器ALU模塊和調用宏模塊定制了RAM模塊,介紹了基于FPGA的CPU設計方法,

2011-03-15 17:39:19 178

178 FPGA在現代電子系統設計中,由于其卓越性能、靈活方便而被廣泛使用,但基于SRAM的FPGA需要從外部進行配置,配置數據很容易被截獲,故存遮安全隱患。總結了當前FPGA的加密方法;提出了一種基于外部單片機的FPGA加密方法,該方法中使用外部單片機配合FPGA產生

2011-03-16 14:22:24 48

48 SPI 串行總線是一種常用的標準接口,其使用簡單方便而且占用系統資源少,應用相當廣泛。本文將介紹一種新的通用的SPI 總線的FPGA 實現方法。

2011-09-09 11:58:27 67

67 本文提出了一種用FPGA實現糾錯編碼的設計思想,并以Altera MAX+PluslI為硬件開發平臺。利用FPGA編程的特點,用軟件編程方法,很好的解決了糾錯編碼中存在的碼速變換和實時性問題,實現

2011-11-10 17:10:59 61

61 誤碼儀是評估信道性能的基本測量儀器。本文介紹的誤碼儀結合FPGA 的特點,采用全新的積分式鑒相結構,提出了一種新的誤碼測試方法,經多次測試驗證,方案可行,設計的系統穩定。

2012-05-02 14:31:02 1291

1291

一種求解動態及不確定性優化問題的新方法_劉曉

2017-01-07 18:56:13 0

0 一種求解車輛垂向振動系統H_2_H_多目標控制的方法_孟建軍_白歡_牟健_銀銘_

2017-01-14 22:32:46 0

0 一種簡化的永磁無刷直流電機直接轉矩控制方法

2017-01-21 12:00:29 4

4 一種簡化的三維模糊制器_沈勇

2017-03-19 11:46:13 0

0 DSP硬件驅動程序的一種方法

2017-10-19 10:48:45 1

1 設計了一種基于FPGA的驗證平臺及有效的SoC驗證方法,介紹了此FPGA驗證軟硬件平臺及軟硬件協同驗證架構,討論和分析了利用FPGA軟硬件協同系統驗證SoC系統的過程和方法。利用此軟硬件協同驗證

2017-11-17 03:06:01 5210

5210

文中介紹了一種基于FPGA的數字秒表設計方法。采用VHDL硬件描述語言,運用ModelSim等EDA仿真工具。該設計具有外圍電路少、集成度高、可靠性強等優點。最后經實驗驗證,該數字秒表計時準確,輸入

2017-11-18 12:13:01 10629

10629 為了更準確地描述帶有記憶效應的射頻(RF)功放特性,基于傳統的動態X參數模型,結合功放長期記憶效應以及短期記憶效應機理,提出一種新型動態X參數功放建模方法。新模型保留X參數模型的靜態核函數,利用雙

2017-11-29 15:51:45 1

1 提出了一種基于FPGA的時鐘跟蹤環路的設計方粢,該方粢簡化了時鐘跟蹤環路的結構,降低了時鐘調整電路的復雜度。實際電路測試結果表明,該方集能夠使接收機時鐘快速準確地跟蹤發射機時鐘的變化,且時鐘抖動小、穩準度高、工作穩定可靠。

2017-11-30 15:10:20 5

5 針對程序中因存在路徑條數過多或復雜循環路徑而導致路徑驗證時的路徑搜索空間過大,直接影響驗證的效率和準確率的問題,提出一種基于可滿足性模理論(SMT)求解器的程序路徑驗證方法。首先利用決策樹的方法

2017-12-11 13:49:41 1

1 ,由猶豫模糊有序加權平均算子集結多屬性及權重信息獲得雙方的匹配度;進而建立一種基于匹配度的多目標優化模型,并使用極大極小法轉化為單目標優化模型求解得到匹配方案;最后,進行實例分析和對比,所提方法得到目標函數值分別

2017-12-14 14:04:34 0

0 隨機時變背包問題(randomized time-varying knapsack problem,簡稱RTVKP)是一種動態背包問題,也是一種動態組合優化問題,目前其求解算法主要是動態規劃的精確

2018-01-03 10:27:38 0

0 針對基本灰狼優化( GWO)算法存在求解精度低、收斂速度慢、局部搜索能力差的問題,提出一種改進灰狼優化(IGWO)算法用于求解約束優化問題。該算法采用非固定多段映射罰函數法處理約束條件,將原約束優化

2018-01-04 15:59:48 0

0 完整準確地提取函數調用圖是基于函數調用圖進行惡意程序相似性分析的基礎。為此,提出一種動靜結合的惡意程序函數調用圖提取方法。在對程序進行靜態反匯編的基礎上抽取惡意程序的可執行路徑,使用隱藏信息主動發現

2018-02-24 13:52:24 0

0 動力學求解時,有兩種思路:一種是對多維時空動力學方程進行時空分離,如改進準靜態法是一個快速高效的求解方法;另外一種是直接求解多維時空動力學方程,并采用處理剛性問題的方法,例如,采用臼法求解中子時空動力學方程,這種

2018-03-12 14:54:54 0

0 和通過Altera的 Avalon 存儲器映射(MM)總線連接的外設組合。這些處理器極大地簡化了最終應用程序,但需要強大的編程背景和復雜工具鏈的知識。這可能會妨礙調試,特別是如果硬件工程師需要一種簡單的方法來讀取和寫入外設而不會影響軟件工程師。

2019-08-07 10:45:00 3384

3384 采用有限差分方程近似地代替偏徽分方程對二維場城中的電位函數進行分析,給出了一種新的處理方法,并設計 了相應的二維電位函數有限差分法求解的MATLAB應用程序。

2019-12-10 08:00:00 1

1 結合社區中的節點屬性與結構信息,提出一種子空間異常社區檢測方法。在待檢測社區集合中,設計基于屬性平均距離的子空間求解策略、基于負熵加權的子空間推斷策略及子空間融合求解策略,挖掘每個社區的屬性權重

2021-04-02 14:27:55 3

3 電子發燒友網為你提供跳上 Avalon 總線:一種簡化的 FPGA 接口資料下載的電子資料下載,更有其他相關的電路圖、源代碼、課件教程、中文資料、英文資料、參考設計、用戶指南、解決方案等資料,希望可以幫助到廣大的電子工程師們。

2021-04-22 08:52:00 7

7 為了快速處理布料的碰撞檢測并獲得真實的接觸摩擦仿真效果,提岀一種基于罰函數的碰撞/接觸解決方案。首先,采用質點-彈簧模型進行布料的仿真模擬,在彈簧形變方向添加改進的阻尼力,以減少粒子之間的振蕩來保證

2021-04-22 11:17:48 21

21 研究絕對值函數的3個光滑逼近函數的性質,并采用圖像展示了逼近效釆。進而提岀求解凸二次規劃問題的新方法:將凸二次規劃轉化為非線性方程組,采用光滑逼近函欻進行處理,得到光滑非線性方程鉏,進而利用高階牛頓法進行求解。數值實驗結果表明:本文方法收斂快、迭代次數少。

2021-04-30 14:39:36 3

3 求解得到一種線性插值DA隨機優化方法不產生累積偏差的個體收斂界,以保證正則化損失函數結構下優化方法的個體收斂精度。實驗結果表明,與隨機加速方法相比,該方法具有較快的個體收斂速率與較高的收斂精度。

2021-05-25 16:20:52 4

4 一種基于FPGA的分頻器的實現說明。

2021-05-25 16:57:08 16

16 電子學報第七期《一種可配置的CNN協加速器的FPGA實現方法》

2021-11-18 16:31:06 15

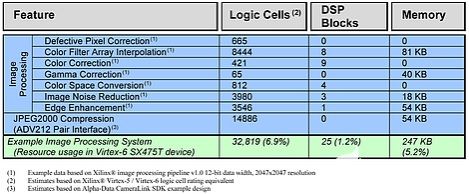

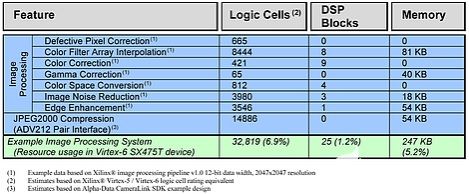

15 監控系統中對更高質量視頻圖像的需求需要在傳感器和可用視頻數據之間建立高級鏈接。僅由軟件處理組成的圖像處理系統無法滿足這些需求,基于ASIC的系統無法提供所需的靈活性。由于像素處理的計算密集型特性,使用JPEG2000編碼的基于FPGA的成像處理設計提供了一種強大而靈活的方法。

2022-10-27 16:45:47 1650

1650

電子發燒友網站提供《一種以硬件語言向Arduino發送消息的方法.zip》資料免費下載

2022-11-02 16:14:20 0

0 傅里葉級數展開的求解方法 傅里葉級數展開是一種將周期函數分解為一系列正弦或余弦函數的方法。該方法在數學、物理、信號處理、圖像處理和工程等領域中得到廣泛應用。本文將探討傅里葉級數展開的定義、求解方法

2023-09-07 16:47:58 7876

7876 電子發燒友網站提供《基于FPGA的一種SDRAM控制器簡易化設計方法.pdf》資料免費下載

2023-10-26 09:08:37 0

0 電子發燒友網站提供《含受控源網絡戴維寧等效電路的一種求解方法.pdf》資料免費下載

2023-11-18 11:52:49 0

0 本文描述了一種簡單高效配置FPGA的方法,該方法利用微處理器從串行外圍接口(SPI)閃存配置FPGA設備。這種方法減少了硬件組件、板空間和成本。

2024-10-24 14:57:24 2382

2382

電子發燒友App

電子發燒友App

評論