本文深入介紹GMSL技術(shù),重點說明用于視頻數(shù)據(jù)傳輸?shù)南袼啬J胶退淼滥J街g的差異。文章將闡明這兩種模式之間的主要區(qū)別,并探討成功實施需要注意的具體事項。

2025-10-10 13:49:02 2004

2004

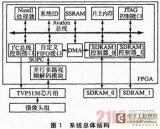

設(shè)計了一種基于FPGA的實時視頻圖像采集處理電路系統(tǒng)。采用FPGA作為整個系統(tǒng)的控制和圖像數(shù)據(jù)處理中心。DDR2 SDRAM為高速儲存模塊核心器件,CMOS 7670為視頻圖像采集器件。

2018-02-10 02:43:55 20488

20488

,最終提供后端可以處理的數(shù)字視頻數(shù)據(jù)。? 視頻數(shù)據(jù)計算模塊 首先接收來自前一個模塊的數(shù)字視頻數(shù)據(jù),然后完成對數(shù)字視頻數(shù)據(jù)的計算。一般數(shù)據(jù)接收由 FPGA 完成,根據(jù)需要可以選擇專用芯片,如 DSP

2018-12-05 09:22:21

伴隨視頻數(shù)據(jù)輸出的行同步信號。 PCLK113用于視頻數(shù)據(jù)總線同步的時鐘信號。 XCLK114外部(FPGA)輸給CMOS Sensor芯片工作的時鐘信號。 VD7115CMOS Sensor輸出

2015-06-01 12:27:01

各位大神,求指導(dǎo)!小弟的項目是這樣的,FPGA開發(fā)板對采集到的視頻數(shù)據(jù)做圖像處理,需要將處理后的視頻數(shù)據(jù),傳輸給ARM,然后讓ARM通過以太網(wǎng)傳輸視頻數(shù)據(jù)。小弟想知道,如何實現(xiàn)讓FPGA開發(fā)板傳輸視頻數(shù)據(jù)給ARM開發(fā)板???求指導(dǎo)!謝謝

2014-02-26 10:04:25

SAA7113 輸出的視頻圖像數(shù)據(jù)通過 8 位總線 VPO 傳輸給 FPGA,FPGA 需要將數(shù)據(jù)保存到 SRAM中。由于 PAL 制電視信號是隔行掃描,分為奇數(shù)場和偶數(shù)場分別傳輸,數(shù)字化以后仍然

2018-12-11 09:47:09

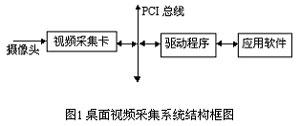

,存儲在電腦中,成為可編輯處理的視頻數(shù)據(jù)文件。按照其用途可以分為廣播級視頻采集卡,專業(yè)級視頻采集卡,民用級視頻采集卡。視頻采集卡又稱視頻捕捉卡,用它可以獲取數(shù)字化視頻信息,并將其存儲和播放出來。很多

2016-03-02 08:29:49

視頻數(shù)據(jù)存儲時,32bit Y CB Y CR ,其中Y和cbcr的范圍是多少0~255,還是-127~128或者16~243?轉(zhuǎn)換為RGB是0~255么?

2020-08-19 09:56:30

控制著傳感器初始化的開始與結(jié)束,傳感器初始化完成后圖像采集模塊將采集到的數(shù)據(jù)寫入 DDR 控制模塊,LCD 頂層模塊從 DDR 控制模塊中讀出數(shù)據(jù),完成了數(shù)據(jù)的采集、緩存與顯示。需要注意的是圖像數(shù)據(jù)采集

2025-10-24 06:53:17

模擬的視頻數(shù)據(jù)通過adc (4路)送到FPGA,直接將數(shù)據(jù)通過cameralink線送到顯示屏幕上顯示,圖像卻分塊。我用攝像頭的datavalid信號的上升沿作為視頻幀的起始位置,可能數(shù)據(jù)經(jīng)過adc

2024-11-04 21:59:15

我想實現(xiàn)采集攝像頭數(shù)據(jù),在屏幕上顯示視頻同時存儲在sd卡上。此功能已經(jīng)完成,但是播該視頻時想要在畫面上顯示每一幀的時間,應(yīng)該如何保把時間和視頻數(shù)據(jù)一起保存起來,這樣播放視頻時就帶有時間了。百度上沒有找到答案,哪位高手可以指點一下謝謝!

2023-09-04 07:42:33

你好,我嘗試使用FX3 DVK,以便將數(shù)字視頻數(shù)據(jù)從連接到DVK的圖像傳感器發(fā)送到PC主機。視頻數(shù)據(jù)需要按原樣傳輸,我不想壓縮它,也不想把它轉(zhuǎn)換成特定的格式。我想把一個包含圖像數(shù)據(jù)的緩沖區(qū)傳送

2019-06-17 08:01:03

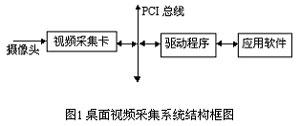

核心,以WinCE為軟件平臺,能實時、連續(xù)地采集清晰的視頻數(shù)據(jù)。1 系統(tǒng)結(jié)構(gòu)框圖及視頻數(shù)據(jù)采集原理視頻數(shù)據(jù)采集系統(tǒng)結(jié)構(gòu)如圖1所示。從圖1中可以看出。系統(tǒng)由嵌入式微處理器S3C2440、存儲器(包括

2019-08-06 08:30:15

L138用BT656方式采集TW9910的視頻數(shù)據(jù)(9910只能輸出UYVY格式視頻數(shù)據(jù)),攝像頭視頻制式為PAL制式,BUFFER已獲取到視頻數(shù)據(jù),使用PYUV播放采集數(shù)據(jù)時圖像顯示不正常,不使

2018-06-21 10:28:07

。TMS320C6748為表準(zhǔn)工業(yè)極DSP處理器,主頻高達(dá)456MHZ,具有非常豐富的外設(shè)接口,非常適合智能家居音視頻數(shù)據(jù)采集與處理系統(tǒng)。板子的例程和相關(guān)資源非常豐富,非常適合研究、學(xué)習(xí)。計劃收到板子先

2015-09-10 11:17:52

請問主板從PCI接口獲取視頻數(shù)據(jù)后如何才能將其播放出來呢? 我的意思是采用PCI接口將外部視頻數(shù)據(jù)傳輸給CPU板,硬件上就是CPU通過PCI橋外擴PCI設(shè)備。軟件上是如何實現(xiàn)的呢?Windows下和VxWorks下的應(yīng)用程序都是怎么做的? 感謝您的回答!

2015-04-27 14:38:53

接收到ITU656標(biāo)準(zhǔn)的數(shù)據(jù)后,首先進(jìn)行解碼處理,將有效視頻數(shù)據(jù)提取出來,FPGA內(nèi)部的主要功能如下:● IIC接口實現(xiàn),用于初始化或控制ADV7180● ITU656協(xié)議解碼,提取有效視頻圖像數(shù)據(jù)

2017-01-05 17:15:52

看過創(chuàng)龍的教學(xué)視頻后受益匪淺,視頻中提到CCS的simulation是用來進(jìn)行算法仿真的,如果我要對圖像處理的算法用simulation進(jìn)行測試,那視頻數(shù)據(jù)源要怎么設(shè)計?

2020-04-26 08:42:14

選擇。視頻處理和圖形生成需要存儲海量數(shù)據(jù),FPGA內(nèi)部的存儲資源無法滿足存儲需求,因此需要配置外部存儲器。與DDR2 SDRAM相比,DDR3 SDRAM帶寬更好高、傳輸速率更快且更省電,能夠滿足

2019-06-24 06:07:53

芯片。最后,考慮到系統(tǒng)占用的面積和以后版本的升級,要求FPGA的內(nèi)部資源盡量豐富。為此,系統(tǒng)最終選用了Altera公司Cyclone系列FPGA。 考慮到視頻數(shù)據(jù)的存儲和顯示是同時進(jìn)行的,而SDRAM

2018-12-11 10:59:36

基于FPGA的高清視頻采集與顯示系統(tǒng)

2012-08-17 23:57:42

評估板THEVA215-V2用于評估THCV216的傳輸視頻數(shù)據(jù)。每個都有一個THCV216。該套件可以傳輸全高清/ 60Hz / 30bit和HD / 120Hz / 30Bit的視頻數(shù)據(jù)

2020-08-27 14:11:50

本篇要分享的是基于XilinxFPGA的視頻圖像采集系統(tǒng),使用攝像頭采集圖像數(shù)據(jù),并沒有用到SDRAM/DDR。這個工程使用的是OV7670 30w像素攝像頭,用雙口RAM做存儲,顯示窗口為

2018-07-03 10:56:57

本篇要分享的是基于XilinxFPGA的視頻圖像采集系統(tǒng),使用攝像頭采集圖像數(shù)據(jù),并沒有用到SDRAM/DDR。這個工程使用的是OV7670 30w像素攝像頭,用雙口RAM做存儲,顯示窗口為

2018-07-09 09:31:05

如何使用DM8148采集HDMI輸出的視頻數(shù)據(jù)呢,有沒有這樣的參考設(shè)計方案和源碼?

2018-06-21 15:02:59

你好,我的FPGA接收視頻,視頻格式是1080p@ 60fps,YYY2。這是使用“32位從FIFO同步”傳輸視頻數(shù)據(jù)的唯一方法嗎?32位數(shù)據(jù)格式是什么?(D:7:0]?D [15:8]?D [23∶16]?,D [31:24]?我不知道如何分配我的視頻數(shù)據(jù)謝謝

2019-09-26 13:26:58

工業(yè)現(xiàn)場因為環(huán)境復(fù)雜,實時性要求高,常常需要對一處或多處重要位置同時進(jìn)行監(jiān)控,且能夠在需要時切換其中一幅畫面全屏顯示。這就要求設(shè)計一種實時視頻監(jiān)控系統(tǒng),既能夠滿足工業(yè)現(xiàn)場應(yīng)用的特殊環(huán)境,具有體積小、功耗低、可定制的特點,又能夠?qū)Χ帱c進(jìn)行同時采集和同屏顯示以及對其中的一路進(jìn)行切換。

2019-11-11 08:31:58

將640 x 480的視頻數(shù)據(jù)輸入給TVP5158進(jìn)行解碼處理,可是輸出的是640 x 240 的視頻數(shù)據(jù),這是什么原因?qū)е碌哪兀?

2024-12-20 07:12:54

怎么實現(xiàn)基于WinCE的嵌入式視頻數(shù)據(jù)采集系統(tǒng)設(shè)計?

2021-06-03 06:39:40

開發(fā)板的四核1.4GHz處理器在視頻監(jiān)控數(shù)據(jù)處理方面表現(xiàn)優(yōu)異。視頻監(jiān)控系統(tǒng)會產(chǎn)生大量的視頻數(shù)據(jù),需要進(jìn)行實時編碼、解碼和分析。該處理器能夠高效地完成這些任務(wù),確保視頻畫面的流暢播放和準(zhǔn)確分析。無論是高清

2025-05-30 10:24:23

有沒有講基于FPGA的關(guān)于視頻采集、處理、存儲、顯示等的書籍

2014-10-27 23:16:37

本帖最后由 一只耳朵怪 于 2018-5-31 16:59 編輯

各位專家,我在做6467T 視頻圖像處理時涉及到視頻數(shù)據(jù)的提取,我不知道視頻數(shù)據(jù)獲取需要的操作步驟,數(shù)據(jù)的存放地址是多少,求賜教!

2018-05-31 03:07:58

fpga怎么采集u***攝像頭出來的視頻數(shù)據(jù)并進(jìn)行相應(yīng)的處理???

2014-12-16 17:11:01

本帖最后由 一只耳朵怪 于 2018-6-21 11:29 編輯

大家好!請教一個問題, AM5728系統(tǒng)是如何通過OpenCL調(diào)用Cortex-M4采集視頻數(shù)據(jù)呢? 視頻數(shù)據(jù)從HDMI Camera輸入進(jìn)來,視頻數(shù)據(jù)為1080p。還請不吝告知! 謝謝大家!

2018-06-21 04:52:31

我知道DM8148的HDMI是TX,我想知道DM8148的HDMI接口可以用來接收視頻數(shù)據(jù)嗎? 比如把電腦等視頻輸出設(shè)備的HDMI接口連接DM814的HDMI接口,DM8148可以采集輸出的視頻數(shù)據(jù)嗎。謝謝

2019-08-26 11:03:57

請問如何查看將此demo中采集到的視頻數(shù)據(jù)的存儲地址,或是圖像二維數(shù)組的地址。我想只有知道圖像二維數(shù)組的地址后,才能將demo所采集的數(shù)據(jù)進(jìn)行處理,對嗎?

2019-05-07 04:51:11

的位置或多觸摸信息需要發(fā)送回中央單元。關(guān)鍵點在于控制數(shù)據(jù)傳輸方向與視頻數(shù)據(jù)流傳輸方向相反。要實施這種控制通道,標(biāo)準(zhǔn)方法是分別運行與視頻鏈路并行的控制線路 — 從攝像頭到主機設(shè)備或從主機設(shè)備到顯示屏…

2022-11-22 07:08:44

FPGA。考慮到視頻數(shù)據(jù)的存儲和顯示是同時進(jìn)行的,而SDRAM存儲器是單端口器件,數(shù)據(jù)的寫入和讀出不能同時進(jìn)行,故需要兩塊SDRAM同時進(jìn)行乒乓操作來完成數(shù)據(jù)的連續(xù)讀寫。最終選用了Micron公司的型號為

2019-04-22 07:00:11

Cyclone系列FPGA。 考慮到視頻數(shù)據(jù)的存儲和顯示是同時進(jìn)行的,而SDRAM存儲器是單端口器件,數(shù)據(jù)的寫入和讀出不能同時進(jìn)行,故需要兩塊SDRAM同時進(jìn)行乒乓操作來完成數(shù)據(jù)的連續(xù)讀寫。最終選用

2019-05-05 09:29:33

Cyclone系列FPGA。考慮到視頻數(shù)據(jù)的存儲和顯示是同時進(jìn)行的,而SDRAM存儲器是單端口器件,數(shù)據(jù)的寫入和讀出不能同時進(jìn)行,故需要兩塊SDRAM同時進(jìn)行乒乓操作來完成數(shù)據(jù)的連續(xù)讀寫。最終選用了Micron

2019-04-23 07:00:10

引言 本文從實際應(yīng)用的角度出發(fā),采用FPGA作為主控芯片,設(shè)計了一款數(shù)字視頻接口轉(zhuǎn)換設(shè)備,該設(shè)備針對于MT9M111這款數(shù)字圖像傳感器產(chǎn)生的ITU-R BT.656格式數(shù)據(jù)進(jìn)行采集、色彩空間變換

2019-04-17 07:00:05

支持配置芯片。最后,考慮到系統(tǒng)占用的面積和以后版本的升級,要求FPGA的內(nèi)部資源盡量豐富。為此,系統(tǒng)最終選用了Altera公司Cyclone系列FPGA。考慮到視頻數(shù)據(jù)的存儲和顯示是同時進(jìn)行的,而

2019-05-29 05:00:03

我想利用筆記本同步采集音頻和視頻數(shù)據(jù) 可是不知道為什么音頻數(shù)據(jù)才一次就出錯 視頻沒事 請高手指點 萬分感謝

2012-05-29 20:50:25

實例是提供觸摸屏顯示器,其中的位置或多觸摸信息需要發(fā)送回中央單元。關(guān)鍵點在于控制數(shù)據(jù)傳輸方向與視頻數(shù)據(jù)流傳輸方向相反。要實施這種控制通道,標(biāo)準(zhǔn)方法是分別運行與視頻鏈路并行的控制線路 — 從攝像頭到主機

2018-09-17 16:02:15

介紹了一種基于DSP 的MPEG-4 視頻壓縮系統(tǒng)中,利用FPGA 控制視頻數(shù)據(jù)實時采集并對原始視頻數(shù)據(jù)進(jìn)行預(yù)處理的設(shè)計方案及實現(xiàn),解決了原始視頻數(shù)據(jù)格式與MPEG-4 壓縮算法不兼容的

2009-08-26 08:57:59 14

14 本文主要闡述了實時圖像處理系統(tǒng)中的一種視頻采集與存儲方案,討論了設(shè)計中的難點與要點。視頻圖像的采集與存儲都是由FPGA 來進(jìn)行控制,采用硬件描述語(Verilog)和自頂向下

2009-09-23 10:32:39 19

19 視頻圖像采集及處理技術(shù)在遠(yuǎn)程視頻監(jiān)控和可視電話中有著廣泛的應(yīng)用前景,驅(qū)動視頻采集設(shè)備和獲取視頻數(shù)據(jù)并進(jìn)行相應(yīng)的處理,是實現(xiàn)這些應(yīng)用的基礎(chǔ)。針對這些應(yīng)用,構(gòu)建了一個

2010-02-23 15:42:03 30

30 數(shù)字視頻圖像采集和存儲的ASIC芯片設(shè)計摘 要:介紹了基于電話線傳輸系統(tǒng)的遠(yuǎn)程視頻報警系統(tǒng)中, 其數(shù)字視頻圖像的采集和存儲的A S IC 芯片設(shè)計。分析了設(shè)計方面的技術(shù)難

2010-06-18 16:32:30 48

48 視頻圖像采集及處理技術(shù)在遠(yuǎn)程視頻監(jiān)控和可視電話中有著廣泛的應(yīng)用前景,驅(qū)動視頻采集設(shè)備和獲取視頻數(shù)據(jù)并進(jìn)行相應(yīng)的處理,是實現(xiàn)這些應(yīng)用的基礎(chǔ)。針對這些應(yīng)用,構(gòu)建了一個

2010-07-14 17:30:11 31

31 在由ARM+DSP組成的嵌入式視頻處理平臺當(dāng)中,需要將視頻數(shù)據(jù)從DSP端發(fā)送給ARM處理器,以便ARM將視頻數(shù)據(jù)傳輸?shù)竭h(yuǎn)端服務(wù)器進(jìn)行處理。提供了一種ARM與DSP雙核之間視頻數(shù)據(jù)通信的解

2010-10-25 16:09:06 38

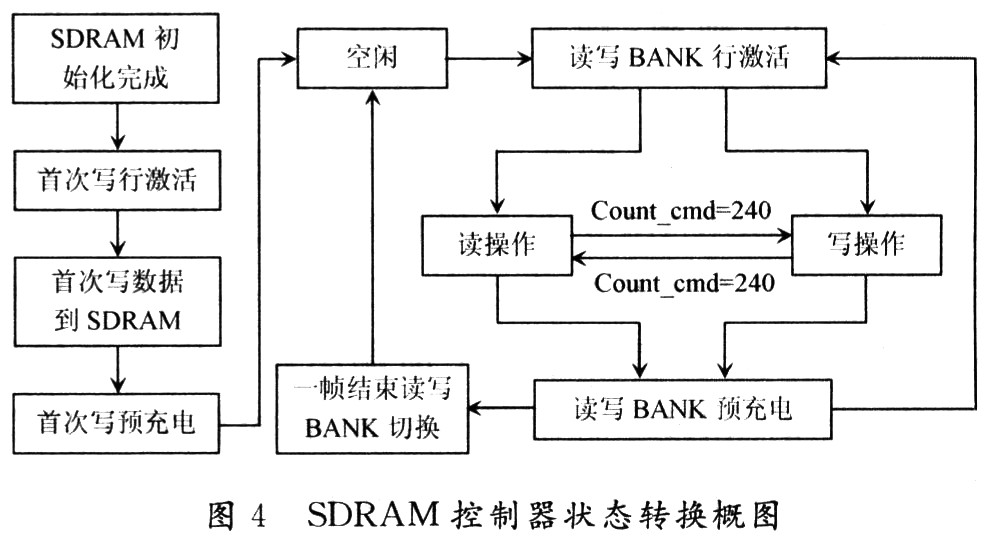

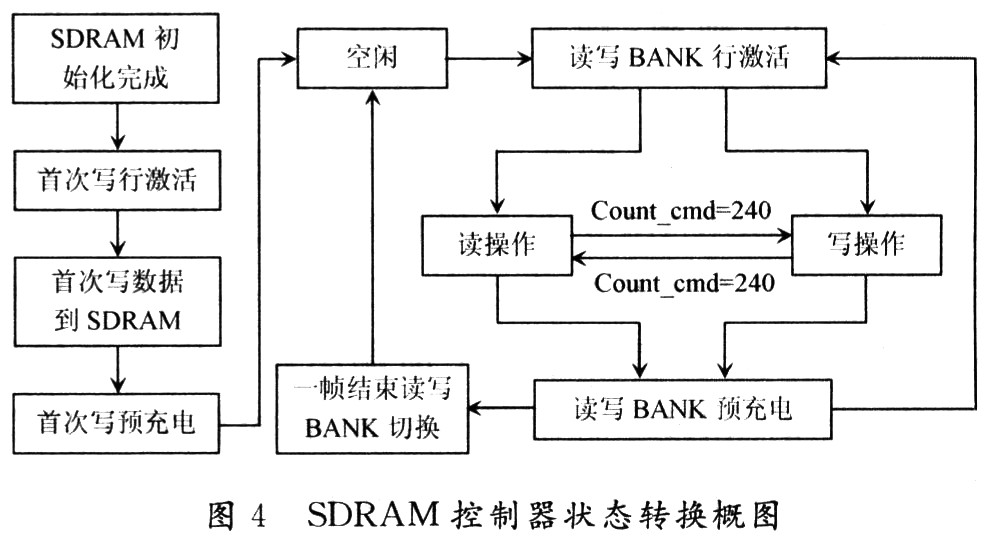

38 實時視頻采集系統(tǒng)的SDRAM控制器設(shè)計

0 引 言 在PAL→VGA的實時視頻采集系統(tǒng)中,由于視頻數(shù)據(jù)流的數(shù)據(jù)量大、實時性要求高。需要高速大容量的存

2009-11-24 09:33:19 1179

1179

摘要:介紹了視頻采集存儲系統(tǒng)的硬件設(shè)計及主要模塊的數(shù)據(jù)處理流程、系統(tǒng)測試結(jié)果。采集制式為PAL的視頻信。號,經(jīng)過視頻解碼器TVP5150轉(zhuǎn)換為數(shù)字視頻數(shù)據(jù),利用TMS320DM642和CPLD器件及與非門Flash等主要器件實現(xiàn)了集視頻數(shù)據(jù)采集、以太網(wǎng)傳輸、存儲、壓縮于

2011-02-28 00:59:31 93

93 本文介紹了一種基于FPGA的視頻采集與顯示系統(tǒng)的設(shè)計。系統(tǒng)以FPGA為核心,配合高分辨率CCD圖像傳感器、ADC模數(shù)轉(zhuǎn)換、視頻編碼器等,實現(xiàn)了高清視頻實時采集與顯示。詳細(xì)闡述了色彩插

2011-08-19 10:53:51 5274

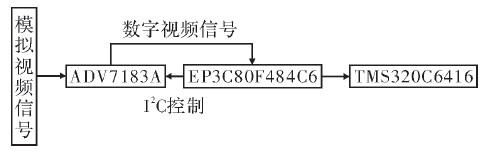

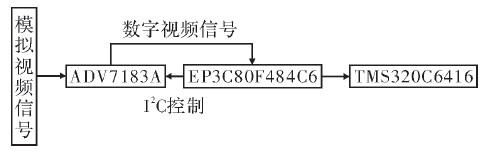

5274 利用FPGA控制視頻解碼芯片ADV7183A,從而輸出8 bit的YCrCb 型4:2:2的視頻數(shù)據(jù),再將其進(jìn)行隔點采樣,得到320256的灰度圖像數(shù)據(jù),并傳輸給DSP,由DSP顯示的采樣數(shù)據(jù)達(dá)到設(shè)計要求,為后來的濾波處理提

2011-11-30 17:19:55 41

41 針對視頻采集系統(tǒng)需要對攝像頭輸出的復(fù)合視頻信號進(jìn)行快速轉(zhuǎn)化、采樣、存儲的要求,設(shè)計基于高速A/D轉(zhuǎn)換器TLC551O的視頻采集系統(tǒng)。模擬視頻信號通過A/D轉(zhuǎn)換器轉(zhuǎn)化為8位灰度值,

2012-05-17 08:55:31 4490

4490

摘 要:研究一種基于FPGA的多路視頻合成系統(tǒng)。系統(tǒng)接收16路ITU656格式的視頻數(shù)據(jù),按照畫面分割的要求對視頻數(shù)據(jù)流進(jìn)行有效抽取和幀合成處理,經(jīng)過視頻編碼芯片轉(zhuǎn)換成模擬信號輸出

2012-09-12 17:18:31 99

99 FPGA實現(xiàn)的視頻圖像縮放顯示,下來看看。

2016-08-29 15:02:03 29

29 基于FPGA的某型雷達(dá)視頻采集預(yù)處理模塊設(shè)計

2016-08-30 15:10:14 34

34 實時、合理的視頻數(shù)據(jù)采集。本文針對自行研制的基于TMS320DM642(以下簡稱DM642)DSP的視頻處理板卡,使其在C64x系列DSP的實時操作系統(tǒng)DSP/BIOS的環(huán)境下運行,實現(xiàn)基于類/微驅(qū)動模型的視頻采集驅(qū)動程序,并進(jìn)一步描述采用EDMA(增強的直接存儲器存

2017-10-20 11:23:40 0

0 選用TMS320DM642作為系統(tǒng)CPU,并采用最新視頻編碼標(biāo)準(zhǔn)H.264壓縮算法,實現(xiàn)基于CDMA網(wǎng)絡(luò)傳輸?shù)臒o線視頻監(jiān)控和視頻數(shù)據(jù)存儲系統(tǒng)。 隨著運營商在國內(nèi)大部分地區(qū)推出GRPS和CDMA1x

2017-11-01 10:35:00 1

1 實時、合理的視頻數(shù)據(jù)采集。本文針對自行研制的基于TMS320DM642(以下簡稱DM642)DSP的視頻處理板卡,使其在C64x系列DSP的實時操作系統(tǒng)DSP/BIOS的環(huán)境下運行,實現(xiàn)基于類/微驅(qū)動模型的視頻采集驅(qū)動程序,并進(jìn)一步描述采用EDMA(增強的直接存儲器存取

2017-11-03 15:44:28 1

1 在變電站中,為了保證現(xiàn)場環(huán)境、設(shè)備外部狀況的全面監(jiān)測,需要安裝大量的攝像頭進(jìn)行晝夜監(jiān)控,攝像頭采集的視頻數(shù)據(jù)量比其他的環(huán)境狀態(tài)數(shù)據(jù)、設(shè)備狀態(tài)數(shù)據(jù)量要大得多。數(shù)據(jù)信息的快速傳輸是站內(nèi)狀態(tài)實時監(jiān)控實現(xiàn)

2017-11-15 16:27:42 14

14 FPGA仿真篇-使用腳本命令來加速仿真二 基于FPGA的HDMI高清顯示借口驅(qū)動 基于FPGA灰度圖像高斯濾波算法的實現(xiàn) FPGA為什么比CPU和GPU快 基于Xilinx FPGA的視頻圖像采集

2018-02-20 20:44:00 1728

1728

隨著視頻監(jiān)控系統(tǒng)的廣泛應(yīng)用,小到一棟大樓、一個社區(qū),大到一座城市都部署了大量的視頻監(jiān)控系統(tǒng),對于視頻數(shù)據(jù)的安全問題也日益凸顯,如何有效保障視頻采集端到服務(wù)端的視頻數(shù)據(jù)保密,也是視頻采集監(jiān)控系統(tǒng)刻不容緩需要解決的問題。

2018-06-29 15:27:58 4304

4304

多媒體通信技術(shù)的發(fā)展為信息的獲取和傳輸提供了豐富的手段,視頻數(shù)據(jù)是其中不可缺少的重要組成部分,而視頻數(shù)據(jù)的獲取離不開視頻采集系統(tǒng)。目前,視頻采集系統(tǒng)的應(yīng)用極為廣泛,許多產(chǎn)品和設(shè)施,例如遠(yuǎn)程監(jiān)控、可視電話、會議電視等等,都需要采集視頻信息。

2018-12-21 07:24:00 3213

3213

BT656的YCrCb型4:2:2視頻數(shù)據(jù),可以根據(jù)BT656的標(biāo)準(zhǔn)提取有效視頻,這樣減少了編程工作,降低了FPGA與ADV7183A的連線,從而為FPGA控制其他芯片節(jié)約了引腳,提供了設(shè)計的靈活性。

2018-11-19 08:37:00 4701

4701

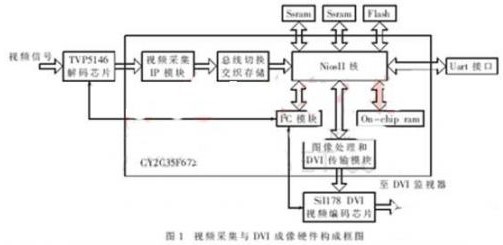

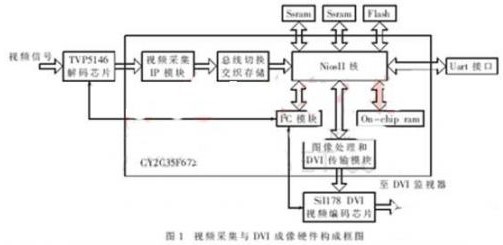

,模擬視頻數(shù)據(jù)經(jīng)視頻解碼芯片輸出ITU-RBT.656格式數(shù)據(jù)送入FPGA,通過時序控制和NiosII軟核把視頻解碼數(shù)據(jù)依序存儲在SSRAM中,并進(jìn)行裁剪、交織、顏色處理。

2019-04-22 08:28:00 2946

2946

針對圖像處理實時性要求高的領(lǐng)域,利用最新的可編程片上系統(tǒng)技術(shù),設(shè)計并實現(xiàn)了基于可編程邏輯器件FPGA的視頻圖像采集及顯示系統(tǒng)?系統(tǒng)以NIOS II軟核為主控制器,將圖像采集?圖像處理及存儲?圖像顯示

2018-09-07 17:14:47 32

32 設(shè)計了一種基于FPGA的視頻實時采集系統(tǒng), 視頻數(shù)據(jù)通過視頻解碼器、雙口RAM、內(nèi)存控制器, 然后存入片外SDRAM中。根據(jù)視頻處理算法的要求和SDRAM的特點, 對視頻數(shù)據(jù)的存儲格式及讀寫時序進(jìn)行了優(yōu)化, 提高了系統(tǒng)的數(shù)據(jù)傳輸速率, 能夠滿足后續(xù)視頻處理系統(tǒng)的需要。

2018-10-18 17:25:35 7

7 芯片,構(gòu)建一個集成NiosII軟核處理器、存儲器、I/O接口、自定義外設(shè)的可編程片上系統(tǒng)系統(tǒng)(System On Programmable Chip,SOPC)。利用FPGA高速并行處理能力,可同時對多路視頻數(shù)據(jù)進(jìn)行視頻解碼,大大提高系統(tǒng)數(shù)據(jù)采集前端的處理能力。

2019-02-11 09:39:26 2549

2549

,基于DSP的海量視頻數(shù)據(jù)的實時處理的關(guān)鍵則是實時、合理的視頻數(shù)據(jù)采集。本文針對自行研制的基于TMS320DM642(以下簡稱DM642)DSP的視頻處理板卡,使其在C64x系列DSP的實時操作系統(tǒng)DSP/BIOS的環(huán)境下運行,實現(xiàn)基于類/微驅(qū)動模型的視頻采集驅(qū)動程序,并進(jìn)一步描述采

2019-02-03 00:09:01 836

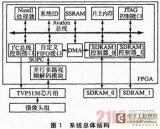

836 提出了一種基于FPGA+ARM的多路視頻采集系統(tǒng)的設(shè)計與實現(xiàn)方法。該視頻采集系統(tǒng)不僅能對多路快速變化的視頻信號進(jìn)行采集和處理,而且能應(yīng)用為系統(tǒng)信號發(fā)生設(shè)備.系統(tǒng)采用FPGA為核心高速時序邏輯控制

2019-11-19 15:51:42 21

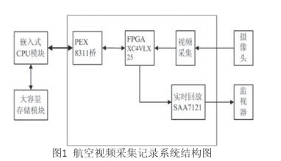

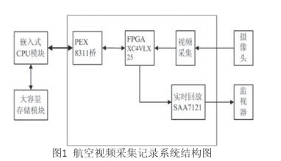

21 可編程邏輯器件(FPGA)進(jìn)行視頻解碼處理。解碼后的數(shù)字視頻,一方面通過SAA7121視頻編碼器直接送給監(jiān)視器,讓飛行員實時掌握訓(xùn)練情況與效果:另一方面通過高速PCIe總線傳送給嵌入式CPU模塊進(jìn)行視頻數(shù)據(jù)壓縮存儲,供事后分析。航空視頻采集記錄系統(tǒng)總體結(jié)構(gòu)如圖1所示。

2020-04-04 11:07:00 1423

1423

網(wǎng)絡(luò)視頻存儲服務(wù)器是一種用于視頻和音頻數(shù)據(jù)壓縮、存儲和處理的嵌入式設(shè)備。它廣泛應(yīng)用于遠(yuǎn)程監(jiān)控和bbb0。網(wǎng)絡(luò)視頻存儲服務(wù)器采用MPEG4或MPEG2壓縮格式,根據(jù)技術(shù)規(guī)范對視頻數(shù)據(jù)進(jìn)行壓縮編碼,以滿足存儲和傳輸?shù)?b class="flag-6" style="color: red">需要。

2020-07-07 10:40:54 3264

3264 設(shè)計了一種基于FPGA的視頻字符疊加系統(tǒng),利用視頻解編碼芯片和FPGA對視頻數(shù)據(jù)進(jìn)行采集和處理,生成所需的帶字符的視頻。介紹了系統(tǒng)的硬件構(gòu)成,YUV數(shù)字視頻信號,I2C控制,視頻字符疊加的原理和具體的程序設(shè)計思想,并對其中的難點進(jìn)行了詳細(xì)分析。本設(shè)計可以在視頻的任意位置疊加字符和圖像,內(nèi)容變動時容易修改.

2020-12-03 16:48:32 24

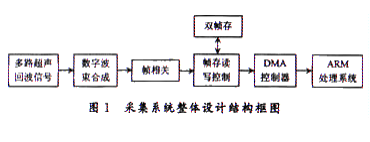

24 隨著計算機技術(shù)、多媒體技術(shù)以及通信技術(shù)的發(fā)展,數(shù)字視頻技術(shù)得到了越來越廣泛的應(yīng)用。在數(shù)字視頻技術(shù)的研究中,視頻數(shù)據(jù)傳輸是一個技術(shù)關(guān)鍵。本文針對視頻數(shù)據(jù)流數(shù)據(jù)量大、實時性要求高的特點,采用流模式傳輸,將視頻采集數(shù)據(jù)通過DMA從存儲資源緊張的片內(nèi)緩存區(qū)搬運至片外SDRAM幀緩沖區(qū),實現(xiàn)圖像的高速傳輸。

2021-03-16 13:45:23 2702

2702

ADA4417-3:用于高清視頻數(shù)據(jù)表的集成三路視頻過濾

2021-04-14 17:34:30 2

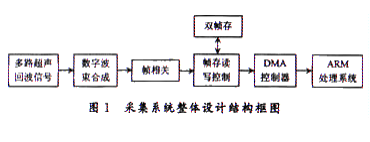

2 由顯示器進(jìn)行顯示。在基于FPGA+ARM 9硬件平臺的全數(shù)字化B超診斷儀中,前端探頭返回的回波電信號需由實時采集系統(tǒng)進(jìn)行波束合成、相關(guān)處理、采集并傳輸至ARM嵌入式處理系統(tǒng),視頻信號數(shù)據(jù)量大,實時性要求高

2021-04-18 09:08:41 4095

4095

,通常只需要將其存儲一兩天,然后將其復(fù)制到云中即可根據(jù)需要將其保存很長時間。這樣,企業(yè)可以維持運營穩(wěn)定性,并遵守可能需要連續(xù)多年保留數(shù)據(jù)的法律要求。 調(diào)查表明,在未來幾年中,將累積大量的視頻數(shù)據(jù)。近年來,視

2021-05-13 10:59:43 5712

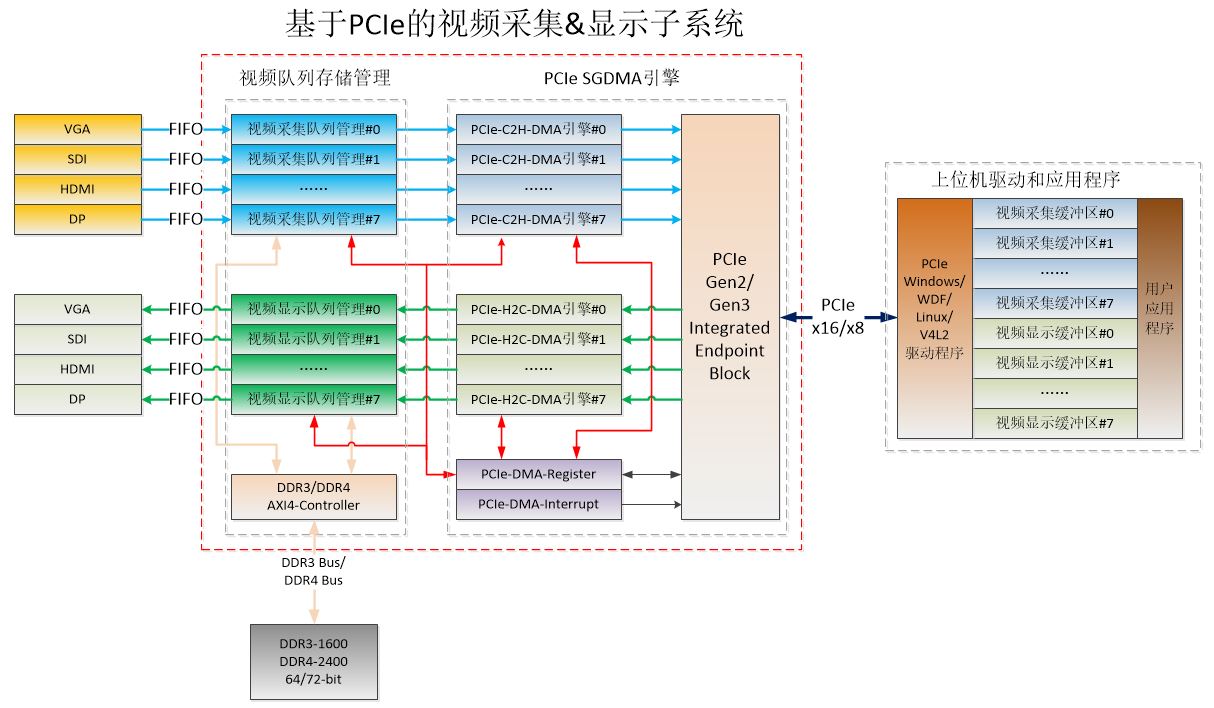

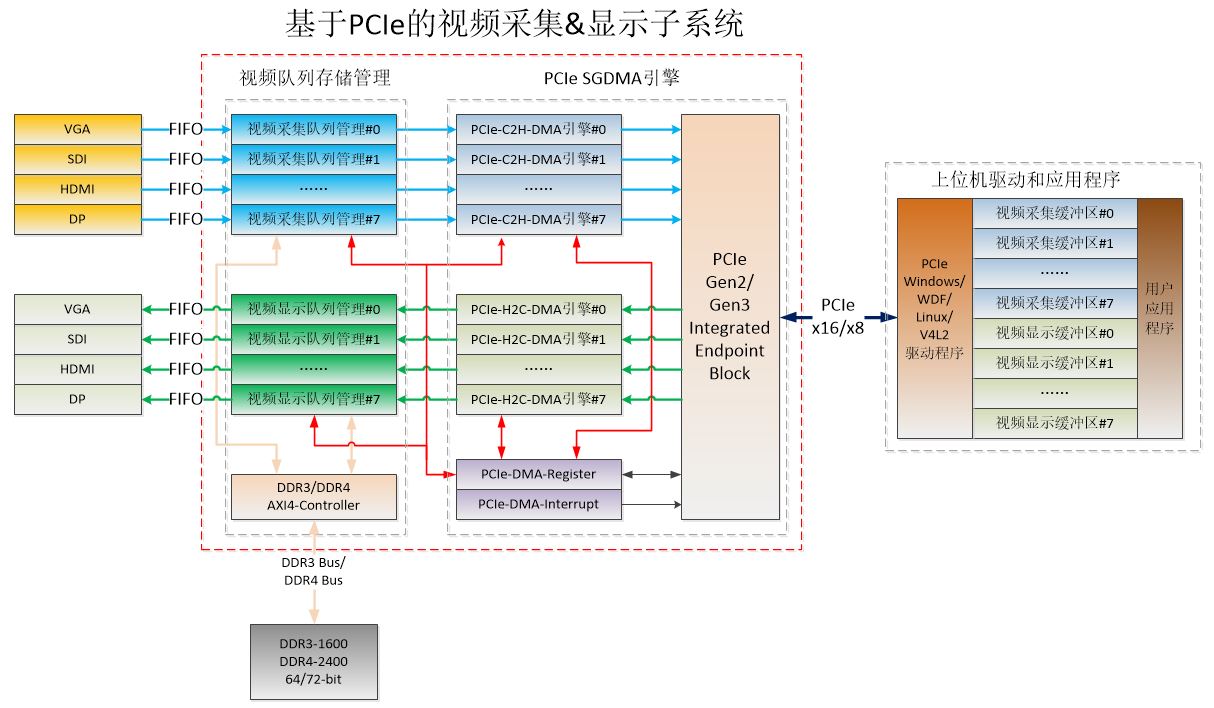

5712 實驗室數(shù)據(jù)采集 , 視頻數(shù)據(jù)收發(fā)卡 , 信號采集、分析 , PCIe的視頻數(shù)據(jù)卡 , 模擬輸出,存儲

2023-12-22 09:40:16 1011

1011

實驗室數(shù)據(jù)采集 , FPGA邏輯視頻采集 , 高速視頻采集卡 , PCIe視頻采集卡 , 視頻程序開發(fā)

2024-01-05 09:44:24 1550

1550

視頻采集與顯示子系統(tǒng)可以實時采集多路視頻信號,并存儲到視頻采集隊列中,借助高效的硬實時視頻幀出入隊列管理和PCIe C2H DMA引擎,將采集到的視頻幀實時傳遞到上位機采集緩沖區(qū)。在超帶寬視頻采集

2024-02-22 20:05:39 1910

1910

隨著智慧安防的不斷進(jìn)步,越來越多的行業(yè)進(jìn)行了安防的升級,其中,對于安防攝像頭所產(chǎn)生的視頻數(shù)據(jù)的存儲處理成為了關(guān)注點。很多行業(yè)企業(yè)對于視頻監(jiān)控的存儲要求都是至少三個月,便于后期的調(diào)取和應(yīng)對突發(fā)

2025-01-07 17:32:13 864

864

電子發(fā)燒友App

電子發(fā)燒友App

評論