編碼和調制是無線通信技術中最核心最深奧的部分,極化碼(polar code)是由土耳其畢爾肯大學(bilkent)Erdal Arikan教授于2008年首次提出,其論文從理論上第一次嚴格證明了在二進制輸入對稱離散無記憶信道下,極化碼可以“達到”香農容量,并且有著低的編碼和譯碼復雜度。

2016-11-21 18:10:30 17148

17148 BCD碼的硬件實現,采用左移加3的算法,具體描述如下:(此處以8-bit 二進制碼為例) 1、左移要轉換的二進制碼1位2、左移之后,BCD碼分別置于百位、十位、個位3、如果移位后所在的BCD碼列大于或

2017-05-11 16:21:02

BP算法、最小和算法、Offset最小和算法、改進的譯碼,如何用vs編碼實現

2017-05-08 22:01:02

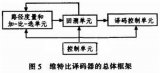

【作者】:申睿;鄧運松;向波;陳赟;曾曉洋;【來源】:《小型微型計算機系統》2010年03期【摘要】:提出一種通用的QC-LDPC碼譯碼器架構.該架構采用一種特殊的綁定結構和一個可配置的循環移位網

2010-04-24 09:26:56

的不足,同時也方便在現場可編程門陣列(FPGA)中增加一些其他相關的應用功能,因此在FPGA中實現CVSD語音編譯碼調制功能的前景將是非常廣闊的。這里將詳細介紹什么是CVSD?其算法分析如何在FPGA中實現?

2019-08-07 07:04:27

什么是Turbo碼的迭代譯碼算法?Turbo 碼獲得優異性能的第二個重要因素是應用了基于最大后驗概率準則 (MAP) 的迭代譯碼算法。當前Turbo譯碼算法有哪些?(1) 標準算法(MAP)它對

2008-05-30 16:24:49

提高。這種級聯碼結構最早于80 年代被美國宇航局NASA 加入深空遙測信號的傳輸協議,目前在視頻通信中廣為應用。道有少量隨機錯誤時,通過內碼就可以糾正;如信道的突發錯誤超出內碼的譯碼能力,則由外碼來糾正

2008-05-30 16:16:10

什么是硬判決和軟判決Viterbi 譯碼算法 ?接收到的符號首先經過解調器判決,輸出0、1 碼,然后再送往譯碼器的形式,稱為硬判決譯碼。即編碼信道的輸出是0、1 的硬判決信息。我們選擇似然概率P

2008-05-30 16:11:37

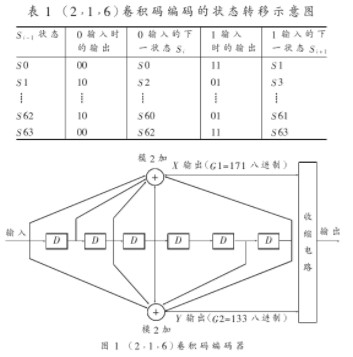

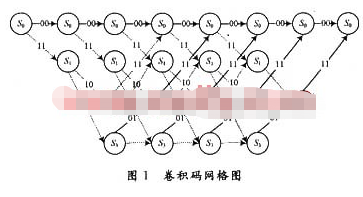

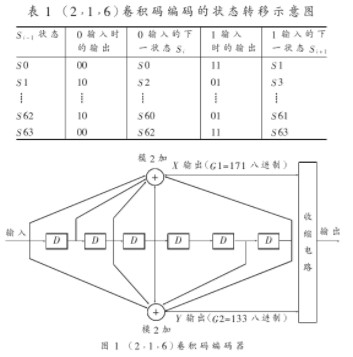

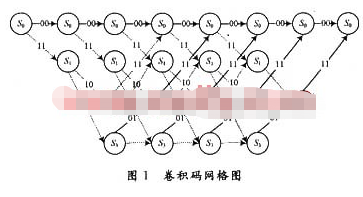

由于卷積碼優良的性能,被廣泛應用于深空通信、衛星通信和2G、3G移動通信中。卷積碼有三種譯碼方法:門限譯碼、概率譯碼和Viterbi算法,其中Viterbi算法是一種基于網格圖的最大似然譯碼算法,是卷積碼的最佳譯碼方式,具有效率高、速度快等優點。

2019-11-01 08:05:38

。另外由于旋轉因子需要進行0°、-90°或+90°三種預旋轉,所以預旋轉還要分配兩位二進制數,這樣存儲旋轉系數的ROM就為18位的ROM。改進的CORDIC算法結構如圖1所示,所有旋轉因子所對應

2011-07-11 21:32:29

。1 適用于圖像分割的改進遺傳算法1.1 算法的基本原理1.1.1 編 碼 基于坐標位置的閾值分割法(閾值曲面方法)具有抗噪聲能力強的特點,對一些用單閾值分割法不易

2009-09-19 09:36:47

糾錯方法,廣泛應用于衛星通信和移動通信中。V iterbi譯碼算法是用于卷積碼譯碼的一種最大似然算法,采用迭代譯碼原理。為提高譯碼性能,Hagenauer提出了軟判決V iterbi算法(SOVA),該算法序列檢測的概率最大,比硬判決提高2.2 dB。早全文下載

2010-04-26 16:08:39

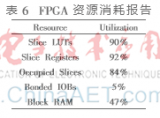

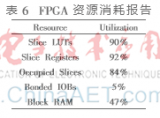

一種在FPGA中實現的基于軟判決的Viterbi譯碼算法,并以一個(2,1,2)、回溯深度為10的軟判決Viterbi譯碼算法為例驗證該算法,在Xilinx的XC3S500E芯片上實現了該譯碼器,最后對其性能做了分析。 關鍵詞: OFDM;Viterbi譯碼;軟判決;FPGA

2009-09-19 09:41:24

本文通過對長BCH碼優化方法的研究與討論,針對標準中二進制BCH碼的特性,設計了實現該譯碼器的FPGA硬件結構。

2021-06-15 09:23:27

BCH碼是目前最為常用的糾錯碼之一,我國的數字電視廣播地面傳輸標準DTMB也使用了縮短的BCH碼作為前向糾錯編碼的外碼。針對該BCH碼的特點,采用BM譯碼算法,設計了一種實時譯碼器。與其它設計方案

2021-05-25 07:04:32

Turbo碼自1993年提出以來[1],由于其接近香農極限的優異譯碼性能,一直成為編碼界研究的熱點。近年來,用戶對通信質量的要求越來越高,學者們已將研究重點從理論分析轉移到Turbo碼的實用化上來

2019-08-22 07:28:46

截短Reed-Solomon碼譯碼器的FPGA實現提出了一種改進的BM算法,并在此基礎上提出了一種大量采用并行結構的截短RS碼譯碼器的實現方式。驗證表明,該算法能顯著提高基于FPGA的RS譯碼

2009-09-19 09:39:43

截短Reed_Solomon碼譯碼器的FPGA實現提 出 了 一 種 改 進 的 算 法 并 在 此 基 礎 上 提 出 了 一 種 大 量 采 用 并 行 結 構 的 截 短 碼譯 碼 器 的 實

2012-08-11 15:50:06

Turbo碼編碼器的FPGA實現Turbo碼譯碼器的FPGA實現Turbo碼編譯碼器的性能有哪些?

2021-05-07 06:06:23

編譯碼的原理是什么?如何對編譯碼算法進行仿真測試?

2021-04-28 06:54:22

在做HDB3碼編譯碼器的實驗,查到資料說FPGA只能處理單極性碼,而HDB3碼是雙極性碼。想請教下是所有的FPGA的芯片都只能處理單極性碼么?如果是的,那么想處理雙極性碼的話要加什么樣的輔助電路才能用FPGA處理雙極性碼?

2016-09-14 16:31:36

數字圖像處理原理是什么?簡單Ferret算法原理是什么?改進的Ferret算法原理有哪些步驟?改進的Ferret算法和目前常用的測量算法有哪些不同?

2021-04-15 06:58:37

不規則重復累計碼BP譯碼算法具有接近Shannon限優越性能,但具有較高的復雜度。為了降低復雜度,提出了IRA碼最小和算法和曲線折線化算法。最小和算法具有簡單、容易實現的特

2008-11-20 12:12:20 9

9 針對LDPC碼與RS碼的串行級聯結構,提出了一種基于Chase的聯合迭代譯碼方法。軟入軟出的RS譯碼器與LDPC譯碼器之間經過多次信息傳遞,性能可以逼近最大似然譯碼。模擬結果顯示:

2009-05-12 21:47:25 22

22 本文基于Altera的FPGA(StatixⅡ-EP2S30F484C3)架構,實現了碼率為1/2,幀長為1008bits的規則(3,6)LDPC碼譯碼器。所采用的最小-和算法相對于傳統的和-積算法在不損失譯碼性能的前提下,

2009-06-06 14:12:20 31

31 快速相關攻擊是一種重要的序列密碼分析方法。該文提出一種基于卷積碼的序列譯碼的快速相關攻擊算法,首先利用特殊的校驗方程將線性分組碼轉化為低碼率卷積碼,然后用卷積碼的

2009-06-17 07:47:48 15

15 面向IEEE 802.16e 中 LDPC 碼,分析了各種譯碼算法的譯碼性能,歸一化最小(NMS)算法具備較高譯碼性能和實現復雜度低的特點。提出一種基于部分并行方式的LDPC 譯碼器結構,可以滿

2009-08-05 08:46:59 24

24 RS 碼以其強大的糾正隨機錯誤和突發錯誤的能力,被廣泛地應用于各種數字通信系統中,本文首先敘述了RS 碼譯碼的基本原理,給出了實現RS 碼軟判決譯碼的方法和用DSP 實現譯碼的

2009-08-19 10:26:07 22

22 文章首先介紹了Turbo 碼的編碼結構和用于Turbo 碼迭代譯碼的最大后驗概率譯碼算法;然后提出了在幾種不同方案下Turbo 碼的信息隱藏技術,對隱藏信息前后的譯碼效果進行了理論分

2009-08-24 10:00:08 14

14 VSPC-LDPC串行級聯碼的結構與性能分析:提出了一種基于LDPC碼和縱向單奇偶校驗(VSPC)乘積碼的級聯編碼方法。該方法利用LDPC碼能否成功地譯碼的判定信息以取代常規乘積碼中的橫向校

2009-10-20 18:01:32 15

15 基于可靠性更新的低復雜度B譯碼算法:基于部分符號更新策略的BP (Belief Propagation)譯碼算法減少了LDPC (Low-Density Parity-Check)碼的譯碼運算量,提高了譯碼效率。然而在其譯碼過程中,由

2009-10-29 13:09:21 16

16 該文結合雙向M-BCJR 算法,提出了一種用于頻率選擇性信道條件下的V-BLAST 系統的改進迭代譯碼算法。該算法通過改進度量函數與引入Kullback-Leibler 距離計算進行雙向搜索的方法,在保

2009-11-17 13:58:53 12

12 本文以CCSDS 推薦的7/8 碼率LDPC 碼為例,提出了一種適于高碼率LDPC 碼譯碼器的硬件結構優化方法。高碼率的LDPC 碼通常也伴隨著行重與列重的比例較高的問題。本方法是在拆分校驗矩

2009-11-25 15:21:25 26

26 該文從譯碼速率、硬件實現的復雜度和誤碼率3 個方面對比研究了兩種典型的高速譯碼算法:Turbo 型和積算法與并行加權比特翻轉算法。以準循環LDPC 碼為對象,給出了Turbo 型和積算

2009-11-25 15:26:58 9

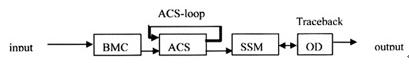

9 Turbo 碼的工程應用與實現是近年來研究工作的熱點。Turbo 碼采用反饋迭代譯碼結構,成員譯碼器使用最大后驗概率(MAP)譯碼算法譯碼,由于MAP 算法含有大量的指數運算與對數運算,

2009-11-27 15:15:31 7

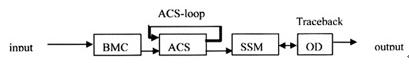

7 本文探討了無線通信中廣泛涉及的差錯控制問題,介紹了卷積碼的編譯碼原理。提出了一種卷積碼編碼,及其高速Viterbi 譯碼的實現方案,對譯碼的各個組成部分作了分析,并在FP

2010-01-06 15:06:59 13

13 規則LDPC碼的密度進化方法及其高斯近似:密度進化方法是分析現代高效糾錯編譯碼漸進性能的新方法。在簡要闡述LDPC碼及其和積算法的基礎上,較系統的論述了密度進化方法的基本

2010-01-12 18:55:09 18

18 文章分析了Turbo 碼的MAP 類譯碼算法后,針對傳統Log—MAP 譯碼算法的特性,提出了一種改進的Log—MAP 譯碼算法。仿真結果表明,新的算法在降低譯碼復雜度的同時較好地保持了譯

2010-01-15 11:51:47 13

13 針對分組Turbo 碼自適應Chase 譯碼算法存在的缺陷,該文提出自適應量化測試序列數的分組Turbo 碼譯碼算法。該方法以測試序列數C 為研究對象,依出錯概率大小選擇錯誤圖樣,并利用

2010-02-10 12:15:52 3

3 IRA碼的譯碼通常是利用BP譯碼算法來實現的,但是BP譯碼算法的硬件電路復雜。為了讓譯碼算法在復雜度和譯碼性能之間取得較好的折衷,提出一種改進型IRA譯碼算法,該算法采用偏

2010-07-05 16:23:56 21

21 本文探討了無線通信中廣泛涉及的差錯控制問題,介紹了卷積碼的編譯碼原理。提出了一種卷積碼編碼,及其高速Viterbi譯碼的實現方案,對譯碼的各個組成部分作了分析,并在FPGA中實現

2010-07-21 17:20:04 22

22 對光碼分多址(OCDMA)的誤碼特性和卷積碼進行研究,根據兩者的特點提出了一種新的基于OCDMA多址干擾信道模型的卷積碼譯碼方法。針對這種新型卷積碼譯碼方法的抗誤碼性和譯

2010-08-26 16:40:22 17

17 針對固定碼長Turbo碼適應性差的缺點,以LTE為應用背景,提出了一種幀長可配置的Turbo編譯碼器的FPGA實現方案。該設計可以依據具體的信道環境和速率要求調節信息幀長,平衡譯碼性

2010-11-11 16:07:59 26

26 LDPC編譯碼LDPC碼是一種線性分組奇偶校驗碼,它采用基于因子圖的置信傳播(Belief Propagation,BP)迭代譯碼算法進行譯碼。其性能接近Turbo碼,不規則LDPC碼甚至超過Tur

2009-03-01 17:36:05 2334

2334

摘要:提出了基于歐氏算法和頻譜分析相結合的RS碼硬件編譯碼方法;利用FPGA芯片實現了GF(2 8)上最高速率為50Mbps、最大延時為640ns的流式譯碼方案,滿足了高速

2009-06-20 14:19:33 1136

1136

Viterbi譯碼原理

Viterbi譯碼算法(簡稱VA算法)是由Viterbi在1967年首先提出的,它是一種針對卷積碼的最大似然譯碼算法。他不是在網格

2009-11-13 18:50:34 7893

7893

卷積碼/Viterbi譯碼,卷積碼/Viterbi譯碼是什么意思

卷積碼在一個二進制分組碼(n,k)當中,包含k個信息位,碼組長度為n,每個碼組的(

2010-03-18 14:09:21 2453

2453 Turbo碼雖然具有優異的譯碼性能,但是由于其譯碼復雜度高,譯碼延時大等問題,嚴重制約了Turbo碼在高速通信系統中的應用。因此,如何設計一個簡單有效的譯碼器是目前Turb

2010-11-25 10:10:26 2375

2375

針對低密度奇偶校驗(LDPC)譯碼算法性能低的問題,提出一種基于最小和的高效譯碼算法。該算法從概率的角度分析消息的傳遞過程中校驗節點的更新過程,得到近似的最小和算法等式,

2011-05-18 18:54:20 0

0 該文介紹了兩種Viterbi 譯碼器回溯譯碼算法,通過對這兩種算法硬件實現結構上的優化,給出了這兩種算法的FPGA 實現方法,比較了兩種實現方法的優缺點。最后將其應用在實際的Viter

2011-05-28 15:18:48 33

33 本文設計實現了一種支持WIMAX標準的碼長、碼率可配置LDPC碼譯碼器,通過設計一種基于串行工作模式的運算單元,實現了對該標準中所有碼率的支持

2011-06-08 09:52:17 2537

2537

本文設計的譯碼器,利用Tail-biting卷積碼的循環特性,采用固定延遲的算法與維特比算法結合,在FPGA上實現和驗證,能達到135.78 MHz時鐘

2011-08-05 11:57:37 5423

5423

提出了一種新的動態補償最小和譯碼算法,并將本算法和修正最小和譯碼算法進行了性能比較。仿真結果顯示,動態補償最小和譯碼雖然算法迭代的收斂速度有所減慢,但具有比修正最

2011-10-08 15:05:33 27

27 卷積碼是深度空間通信系統和無線通信系統中常用的一種差錯控制編碼。它克服了分組碼由于以碼塊為單位編譯碼而使分組間的相關信息丟失的缺點。(2,1,8)卷積碼在2G、3G通信系統

2011-10-12 15:05:59 1966

1966

針對Turbo乘積碼(TPC)譯碼復雜度高、運算量大的缺點,分析了一種改進的TPC譯碼算法。該算法以Chase迭代算法為基礎,通過對錯誤圖樣重新排序產生新的測試序列,其伴隨式可從前次伴

2011-12-05 14:07:55 20

20 利用ME算法實現結構設計了一種低資源占用率、低成本的高速RS譯碼器。邏輯綜合及仿真結果表明,基于Altera公司CycloneII系列FPGA的RS(255,239)譯碼器,工作時鐘達210 MHz,可滿足數據速率1.68 Gb

2011-12-15 17:23:28 28

28 在描述置信傳播(BP)譯碼算法基礎上, 研究和分析了兩種降低復雜度的譯碼算法。Min.Sum 算法主要討論了簡化校驗節點的消息更新運算,并應用密度進化方法對此算法進行極限性能分析

2012-03-31 15:22:03 7

7 針對傳統的Max-Log-Map譯碼算法時效性差、存儲空間開銷大的特點,本文對傳統的Max-Log-Map譯碼算法進行了改進。改進的算法對前、后向度量使用了蝶形結構圖,便于DSP實現;將原始幀均分

2012-07-27 17:55:16 42

42 介紹了符合CCSDS標準的RS(255,223)碼譯碼器的硬件實現結構。譯碼器采用8位并行時域譯碼算法,主要包括了修正后的無逆BM迭代譯碼算法,錢搜索算法和Forney算法。采用了三級流水線結構實現

2013-01-25 16:43:46 68

68 香農的學生Gallager首次提出了LDPC碼的概念和完整的譯碼方法,目前LDPC碼正向著高速高增益的方向發展。文中針對目前對高速LDPC碼譯碼技術的迫切需求,以CCSDS標準近地通信(8176,7154)

2013-07-26 11:17:00 0

0 活躍。對人工魚群算法改進方法進行了論述,從自身改進和與其他算法融合兩個大方向進行評述,為后續改進型人工魚群算法的研究提供了理論基礎。

2016-01-04 17:13:49 12

12 低密度奇偶校驗碼(LDPC碼)譯碼主要包括基于硬判決和基于軟判決的譯碼。文章對這兩種譯碼方法中的典型算法(BF算法和BP算法)和一種改進的對數域算法(APP-LLR算法)進行了仿真研究;比較并分析了

2016-01-04 17:13:49 13

13 基于FPGA的RS碼電路設計,編碼譯碼原理。

2016-03-30 16:32:42 2

2 截短Reed_Solomon碼譯碼器的FPGA實現

2016-05-11 11:30:19 11

11 基于遺傳算法的信源信道聯合譯碼方法,有需要的下來看看

2016-07-20 16:51:51 3

3 實時圖像增強算法改進及FPGA實現,下來看看

2016-09-17 07:28:24 15

15 一種基于改進線性規劃的LDPC碼混合譯碼算法_陳紫強

2017-01-07 16:52:06 0

0 改進的MIMO系統球譯碼檢測算法_仵丹

2017-03-19 19:04:23 2

2 改進匹配方法的BFG_GMPHD濾波算法_趙斌

2017-03-19 19:04:39 1

1 提出了一種實用的LDPC碼譯碼停止準則,利用信息節點的對數概率似然比來控制迭代次數,避開了設置停止準則門限,可以很快判斷出譯碼情況,較其他方法省去了大量繁雜的計算。

2017-09-07 19:38:11 10

10 的低運算復雜度、低誤碼平臺譯碼的改進算法。 該算法校驗節點的運算采用修正最小和算法,外信息的更新采用串行方式,既保持了串行和積算法在有限迭代次數下譯碼門限低的優點,又降低了節點運算復雜度和誤碼平臺。用定點DSP芯片實現的非規則LDPC碼譯碼器的實測結果表明,該算法能以較低的實現復雜度獲

2017-10-20 10:41:11 0

0 采用易于FPGA實現的歸一化最小和算法,通過選取合適的歸一化因子,將乘法轉化成移位和加法運算。在高斯白噪聲信道下,仿真該譯碼算法得出最佳的譯碼迭代次數,并結合Xilinx XC7VX485T資源確定

2017-11-16 12:59:01 3910

3910

該文通過對低密度校驗(LDPC)碼的編譯碼過程進行分析,提出了一種基于FPGA 的LDPC 碼編譯碼器聯合設計方法,該方法使編碼器和譯碼器共用同一校驗計算電路和復用相同的RAM 存儲塊,有效減少

2017-11-22 07:34:01 5141

5141

卷積碼是Elias在1955年最早提出的,稍后,Wozencraft在1957年提出了一種有效譯碼方法,即序列譯碼。Massey在1963年提出了一種性能稍差,但比較實用的門限譯碼方法,由于這一實用性進展使卷積碼從理論走向實用。

2019-10-06 09:59:00 1749

1749

中小長度的數據報文業務為主,所以突發通信中的Turbo碼的碼長也是中等長度以下的。本文面向突發數據通信中的信道編碼應用,研究了短幀長Turbo碼編譯碼算法的FPGA實現。實現中采用了優化的編譯碼算法,以降低譯碼復雜度和譯碼延時。最后仿真和測試了Turbo譯碼器的糾錯性能和吞吐量。

2018-07-12 08:15:00 4457

4457

信道編譯碼技術可以檢測并且糾正信號在傳輸過程中引入的錯誤,能夠保證數據進行可靠的傳輸[1]. LDPC碼的校驗矩陣具有稀疏的特性,因此存在高效的譯碼算法,其糾錯能力非常強。1981年,Tanner

2017-11-30 10:21:27 5864

5864

1996年LDPC(低密度奇偶校驗,Low-Density Parity-Check)碼是性能限與香農限僅差0.0045 dB的一種差錯控制碼,譯碼采用SPA(和積算法),但其性能受Tanner圖中

2017-12-26 11:09:14 0

0 不規則重復累積碼(IRA)的譯碼通常采用置信傳播(BP)譯碼算法,然而BP譯碼算法需進行雙曲正切函數計算,復雜度高,不利于硬件實現。為此,提出一種基于分段函數修正和預檢測機制結合的譯碼算法,通過對折

2018-01-08 15:52:39 0

0 。基于稀疏矩陣的二分圖,首先改進了PEG算法用以構造規則I_DPC,然后用BCH碼作子碼替換LDPC中的單奇偶校驗碼來構造PFGGLDPC,最后重點研究了PFG-GDPC的譯碼算法,提出一種聯合BCH

2018-03-09 11:21:20 0

0 coding,RS-CC碼)以構造等效刪除信道,并采用實時性高的短I_T碼實現糾刪功能。設計了一種適合短I.T碼的譯碼算法,同時給出了編碼度分布的選取方法。仿真結果表明,與已有短噴泉碼相比,文中短I_T碼成功譯碼時所需編碼冗余更少,應用到級聯方案后的數據傳輸可靠性明顯提高

2018-03-20 16:19:12 0

0 卷積碼是廣泛應用于衛星通信、無線通信等各種通信系統的信道編碼方式。Viterbi算法是一種最大似然譯碼算法。在碼的約束度較小時,它比其它概率譯碼算法效率更高、速度更快,譯碼器的硬件結構比較簡單。隨著

2019-04-24 08:29:00 3644

3644

信道的是二進制信號序列。為了充分利用信道輸出信號的信息,提高傳輸系統譯碼的可靠性,首先把信道的輸出信號量化,將Q電平量化序列輸入Viterbi譯碼器,因此本文采用的VB譯碼算法為軟判決譯碼算法。

2019-07-11 08:01:00 4031

4031

本文對2004年由王鵬提出的LDPC碼迭代編碼算法[11]進行改進,轉變為適用于多元LDPC碼的編碼算法,稱為多元迭代編碼算法;2005年,Hu Xiaoyu提出了漸進邊增長(Progressive Edge Growth,PEG)構造算法[12],該算法譯碼性能好,但編碼復雜度較高。

2018-09-23 08:59:00 5484

5484

第三代移動通信系統多種方案中,考忠將Turbo碼作為無線信道的編碼標準之- ~。 本文討論了Turbo碼的編譯碼基本原理,對Turbo碼的幾種常用的編譯碼算法進行了分析,并在給出編譯碼器模型的基礎上,用MATLAB語言實現了整個系統的計算機仿真并給出參

2019-01-04 10:40:42 19

19 極化碼的譯碼算法研究近年來發展迅速,其中成為研究熱點的連續刪除(Successive Cancellation,SC)譯碼算法的基本思想是通過對信息位的比特似然概率值的判斷來進行譯碼。

2019-01-06 11:19:55 5766

5766

由于卷積碼優良的性能,被廣泛應用于深空通信、衛星通信和2G、3G移動通信中。卷積碼有三種譯碼方法:門限譯碼、概率譯碼和Viterbi算法,其中Viterbi算法是一種基于網格圖的最大似然譯碼算法

2020-08-11 17:41:23 1390

1390

為塊準循環結構,從而能夠并行化處理譯碼算法的行與列操作。使用這個架構,我們在Xilinx Virtex-5 LX330 FPGA上實現了(8176,7154)有限幾何LDPC碼的譯碼器,在15次迭代的條件下其譯碼吞吐量達到800Mbps。

2021-01-22 15:08:39 9

9 RS碼在通信領域有著廣泛的應用,其中最重要的是關鍵方程的求解.傳統歐幾里德算法在求解關鍵方程時需要進行多項式次數的判斷,從而造成硬件電路復雜,譯碼速度下降.通過對綜合除法進行推廣,提出了一種改進

2021-02-01 14:25:00 10

10 分組進行并行譯碼,每個分組采用并行結構進行譯碼,具有更快的收斂速度和更少的存儲空間。為了對一個具有并行結構的數據包進行解碼,首先將LDC碼分為若干個超碼。然后用并行BCJR算法對每個超碼進行解碼。為了進一步簡化算法的內部結構和復雜度,提出了一種改進的陪集算法。基于Alte

2021-02-03 14:46:00 9

9 結構化LDPC碼可進行相應擴展通過對編譯碼算法,優化編譯碼結構進行調整,降低了編譯碼囂硬件實現中的關鍵路徑遲延,并采用Xilinx公司的Virtex一4 VLX80 FPGA芯片實現了一個碼長10 240,碼率1/2的非正則結構化LDPC碼編碼器和譯碼器。實現結果表明:該編碼器信息吞吐量為1.878 Gb/

2021-03-26 15:58:00 12

12 給出了跳頻系統中 Turbo碼譯碼器的FPGA( field programmable gate array)實現方案。譯碼器采用了MaxLog-map譯碼算法和模塊化的設計方法,可以對不同幀長

2021-04-01 11:21:46 5

5 基于FPGA的800Mbps準循環LDPC碼譯碼器

2021-06-08 10:31:31 26

26 并執行MC方法,以衡量剩余位信道的差錯概率,從剩余位中挑選差錯概率較低的位并與第1階段中最可靠的位組成極化碼的信息位集合。仿真結果表明,與MC方法相比,TPMe方法能夠降低計算復雜度,提髙譯碼效率。

2021-06-08 16:04:32 5

5 卷積碼是一種信道糾錯編碼,在通信中具有廣泛的應用。在發送端根據生成多項式進行卷積碼編碼,在接收端根據維特比(Viterbi)譯碼算法進行譯碼,能夠有效抵抗信道噪聲的影響,在誤碼率門限之下可以對傳輸過程中發生的突發錯誤進行糾錯。

2022-04-28 15:02:12 14741

14741

電子發燒友App

電子發燒友App

評論