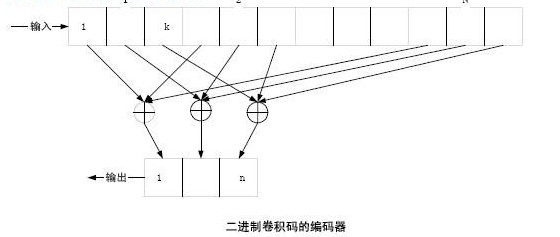

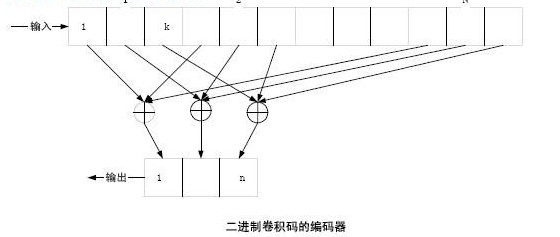

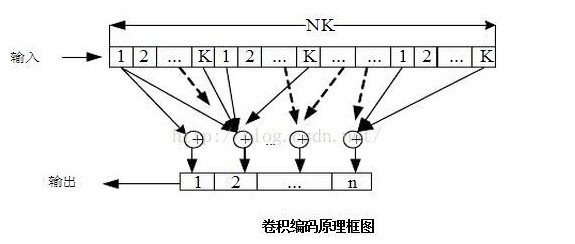

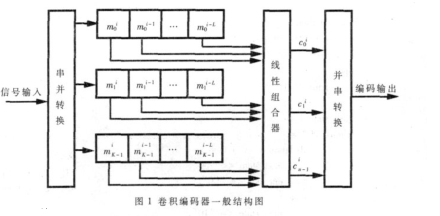

卷積碼將k個信息比特編成n個比特,但k和n通常很小,特別適合以串行形式進行傳輸,時延小。

2018-08-21 09:36:40 16754

16754

請問各位大神,我想問一下用FPGA做卷積碼有什么注意的地方?

2015-04-07 12:57:40

【作者】:王中鵬;陳林;曹子崢;董澤;【來源】:《光電子.激光》2010年03期【摘要】:將卷積碼成功地應(yīng)用到直接檢測的光正交頻分復(fù)用(OFDM)光纖傳輸實驗系統(tǒng)。實驗中,產(chǎn)生了2 Gb/s

2010-04-23 11:30:18

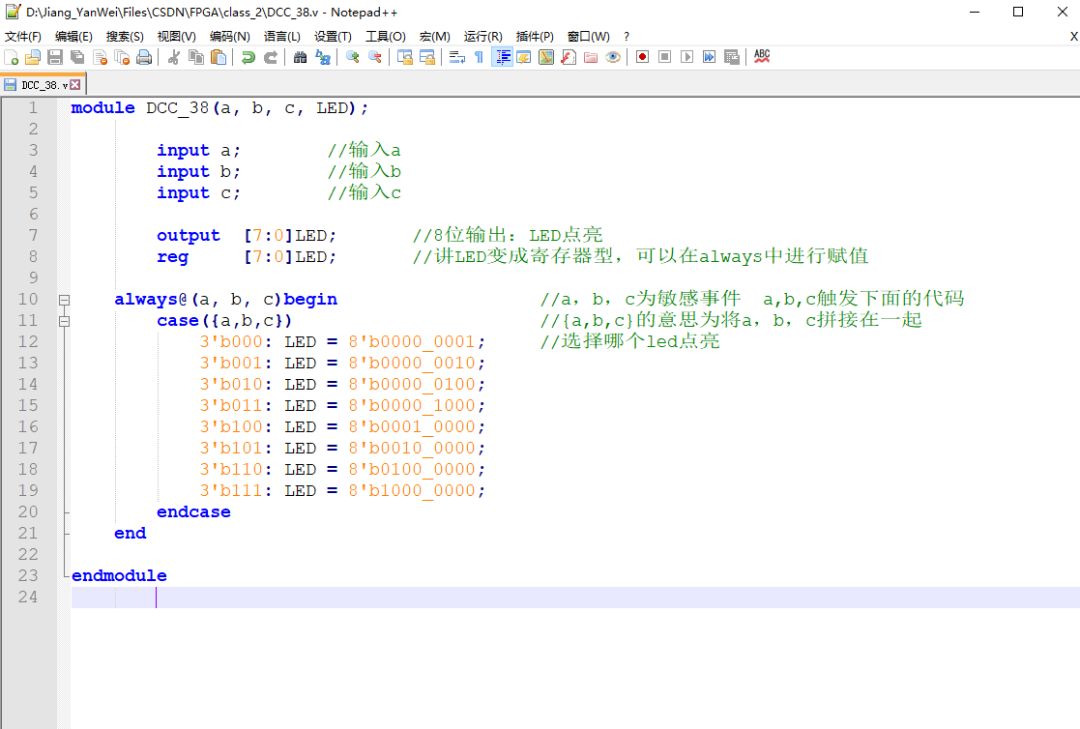

譯碼器1. 譯碼器定義譯碼器是一種用以檢測輸入位(碼)的特定組合是否存在,并以特定的輸出電平來指示這種特定碼的存在的數(shù)字電路。——《數(shù)字電子技術(shù)基礎(chǔ)系統(tǒng)方法》譯碼器的功能是將具有特定含義的二進制碼

2021-12-07 09:37:27

各位專家大俠,我現(xiàn)在在做LTE的PBCH的譯碼,編碼是采用的咬尾卷積碼,輸入信號長度為40,碼率為1/3,約束長度為7,編碼時,寄存器的初始狀態(tài)放的是輸入序列的最后6位信息,最終輸出為120比特

2018-06-21 05:05:53

什么是卷積碼分組碼是把k 個信息元編成n 個碼元的碼字,每個碼字的n ? k 個校驗位僅與本碼字的k 個信息元有關(guān),而與其他碼字無關(guān)。為了達到一定的糾錯能力和編碼效率,分組碼的碼長一般都比較大。編譯碼

2008-05-30 16:06:52

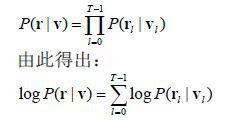

BCJR 算法做了一定修正,對 α 和β 作歸一化。對約束長度為N 的卷積碼,每一分量,使似然加法完全變成求最大值運算,則得到MAX-LOG-MAP 算法。它大大降低了存儲量和計算復(fù)雜度,而譯碼性能僅惡化

2008-05-30 16:24:49

。由此可見,級聯(lián)碼適用于組合信道。由于內(nèi)碼譯碼器的錯誤往往是連續(xù)出現(xiàn)的,一般在內(nèi)外編碼器之間需要一個交織器,接收端也相應(yīng)地增加反交織器。級聯(lián)碼的組合方式很多,如外碼采用RS 碼,內(nèi)碼用二進制分組碼或卷積碼

2008-05-30 16:16:10

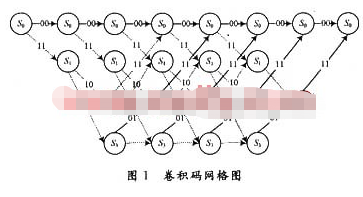

Viterbi 譯碼算法可以簡單概括為“相加-比較-保留”,譯碼器運行是前向的、無反饋的,實現(xiàn)過程并不復(fù)雜。我們來分析Viterbi 算法的復(fù)雜度: (n, k, N) 卷積碼的狀態(tài)數(shù)為 條幸存

2008-05-30 16:11:37

請問各路大神有沒有基于multisim的線性分組碼 循環(huán)碼 卷積碼的編譯碼電路圖啊,在這里謝過你們了

2015-04-23 17:56:37

譯碼算法可以簡單概括為“相加-比較-保留”,譯碼器運行是前向的、無反饋的,實現(xiàn)過程并不復(fù)雜。我們來分析Viterbi 算法的復(fù)雜度: (n, k, N) 卷積碼的狀態(tài)數(shù)為2k (N?1) ,對每一時

2008-05-28 15:03:31

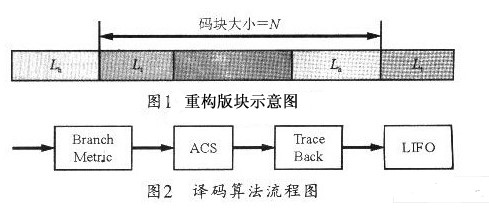

由于卷積碼優(yōu)良的性能,被廣泛應(yīng)用于深空通信、衛(wèi)星通信和2G、3G移動通信中。卷積碼有三種譯碼方法:門限譯碼、概率譯碼和Viterbi算法,其中Viterbi算法是一種基于網(wǎng)格圖的最大似然譯碼算法,是卷積碼的最佳譯碼方式,具有效率高、速度快等優(yōu)點。

2019-11-01 08:05:38

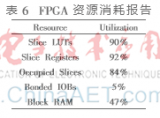

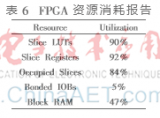

【摘要】:Viterbi譯碼器在通信系統(tǒng)中應(yīng)用非常普遍,針對采用DSP只能進行相對較低速率的Vit-erbi譯碼的問題,人們開始采用FPGA實現(xiàn)高速率Viterbi譯碼。本文首先簡單描述了

2010-04-26 16:08:39

求助!大佬們,問一下用FPGA實現(xiàn)卷積碼編解碼的難度。

2023-10-16 23:26:26

LDPC碼是近年來發(fā)展較快且日趨成熟的一種信道編碼方案,因其具有的優(yōu)越性能和實用價值而被人們認知,但由于隨機結(jié)構(gòu)的LDPC碼編譯碼器硬件實現(xiàn)較為復(fù)雜,具有的準循環(huán)特性QC_LDPC碼已成為IEEE802.11n(WiFi)、IEEE802.16e(WiMAX)、(DVB—S2)等眾多標準的信道編碼方案。

2019-09-30 07:19:45

如何利用VHDL實現(xiàn)線性分組碼編譯碼器的設(shè)計?

2021-04-28 06:41:40

由于卷積碼具有較好的糾錯性能,因而在通信系統(tǒng)中被廣泛使用。采用硬件描述語言VerilogHDL或VHDL和FPGA(FieldProgrammableGateArray——現(xiàn)場可編程門陣列)進行數(shù)字通信系統(tǒng)設(shè)計,可在集成度、可靠性和靈活性等方面達到比較滿意的效果。

2019-10-14 06:02:23

如何使用VHDL語言設(shè)計卷積碼編解碼器?

2021-04-29 06:39:03

本文通過對長BCH碼優(yōu)化方法的研究與討論,針對標準中二進制BCH碼的特性,設(shè)計了實現(xiàn)該譯碼器的FPGA硬件結(jié)構(gòu)。

2021-06-15 09:23:27

BCH碼是目前最為常用的糾錯碼之一,我國的數(shù)字電視廣播地面?zhèn)鬏敇藴蔇TMB也使用了縮短的BCH碼作為前向糾錯編碼的外碼。針對該BCH碼的特點,采用BM譯碼算法,設(shè)計了一種實時譯碼器。與其它設(shè)計方案

2021-05-25 07:04:32

本文研究了RS碼的實現(xiàn)方法,并基于Xilinx的FPGA芯片Spartan-6 XC6SLX45完成了RS編譯碼器的設(shè)計,同時對其進行了仿真和在線調(diào)試,并給出了功能仿真圖和測試結(jié)果。時序仿真結(jié)果表明,該編譯碼器能實現(xiàn)預(yù)期功能。

2021-06-21 06:23:53

基于FPGA的Turbo碼編譯碼器各模塊實現(xiàn)的 VHDL或verilog HDL程序。急求啊謝謝大神啦!!

2015-06-08 22:45:24

截短Reed-Solomon碼譯碼器的FPGA實現(xiàn)提出了一種改進的BM算法,并在此基礎(chǔ)上提出了一種大量采用并行結(jié)構(gòu)的截短RS碼譯碼器的實現(xiàn)方式。驗證表明,該算法能顯著提高基于FPGA的RS譯碼器

2009-09-19 09:39:43

截短Reed_Solomon碼譯碼器的FPGA實現(xiàn)提 出 了 一 種 改 進 的 算 法 并 在 此 基 礎(chǔ) 上 提 出 了 一 種 大 量 采 用 并 行 結(jié) 構(gòu) 的 截 短 碼譯 碼 器 的 實

2012-08-11 15:50:06

畢業(yè)設(shè)計 基于EDA的CMI碼編碼譯碼器的設(shè)計,共20頁,7505字 摘要 CMI碼是一種應(yīng)用于PCM四次群和光纖傳輸系統(tǒng)中的常用線路碼型,它具有碼變換設(shè)備簡單、便于時鐘提取、有一定的糾錯能力

2009-03-25 13:19:20

Turbo碼編碼器的FPGA實現(xiàn)Turbo碼譯碼器的FPGA實現(xiàn)Turbo碼編譯碼器的性能有哪些?

2021-05-07 06:06:23

針對LDPC碼與RS碼的串行級聯(lián)結(jié)構(gòu),提出了一種基于Chase的聯(lián)合迭代譯碼方法。軟入軟出的RS譯碼器與LDPC譯碼器之間經(jīng)過多次信息傳遞,性能可以逼近最大似然譯碼。模擬結(jié)果顯示:

2009-05-12 21:47:25 22

22 本文基于Altera的FPGA(StatixⅡ-EP2S30F484C3)架構(gòu),實現(xiàn)了碼率為1/2,幀長為1008bits的規(guī)則(3,6)LDPC碼譯碼器。所采用的最小-和算法相對于傳統(tǒng)的和-積算法在不損失譯碼性能的前提下,

2009-06-06 14:12:20 31

31 快速相關(guān)攻擊是一種重要的序列密碼分析方法。該文提出一種基于卷積碼的序列譯碼的快速相關(guān)攻擊算法,首先利用特殊的校驗方程將線性分組碼轉(zhuǎn)化為低碼率卷積碼,然后用卷積碼的

2009-06-17 07:47:48 15

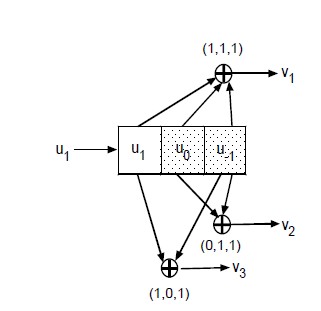

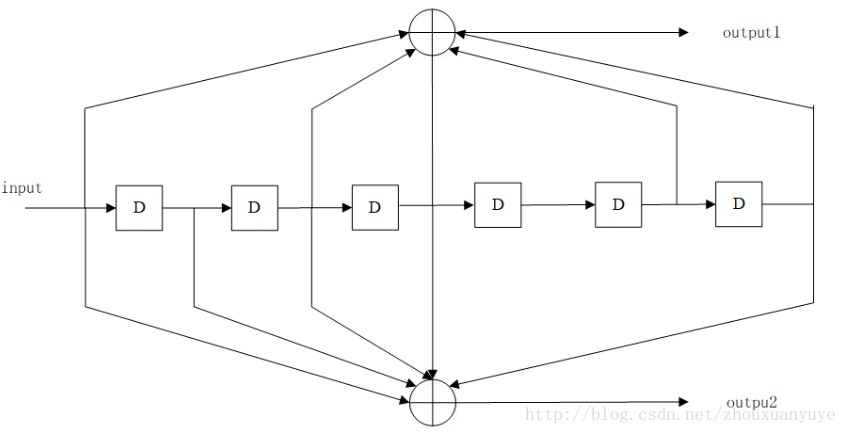

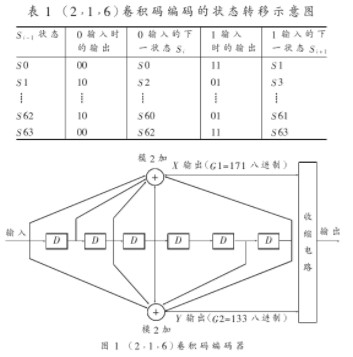

15 卷積碼是一種性能優(yōu)良的差錯控制編碼。本文闡述了卷積碼編解碼器的基本工作原理,在MAX+PLUS2 軟件平臺上,給出了利用復(fù)雜可編程邏輯器件設(shè)計的(2,1,6)卷積碼編解碼器電路

2009-08-10 08:39:06 24

24 本文以CCSDS 推薦的7/8 碼率LDPC 碼為例,提出了一種適于高碼率LDPC 碼譯碼器的硬件結(jié)構(gòu)優(yōu)化方法。高碼率的LDPC 碼通常也伴隨著行重與列重的比例較高的問題。本方法是在拆分校驗矩

2009-11-25 15:21:25 26

26 EDA卷積碼編解碼器實現(xiàn)技術(shù)針對某擴頻通信系統(tǒng)數(shù)據(jù)糾錯編碼的需要, 構(gòu)造并分析了(2 , 1 , 6) 卷積碼編解碼器的基本工作原理, 提出了基于MAX + plus Ⅱ開發(fā)平臺的(2 , 1 ,

2009-12-05 16:17:42 0

0 本文探討了無線通信中廣泛涉及的差錯控制問題,介紹了卷積碼的編譯碼原理。提出了一種卷積碼編碼,及其高速Viterbi 譯碼的實現(xiàn)方案,對譯碼的各個組成部分作了分析,并在FP

2010-01-06 15:06:59 13

13 提出用Reed Solomon(RS)乘積碼作為外碼,卷積碼作為內(nèi)碼的級聯(lián)碼方案并且內(nèi)外碼間用Congruential 向量生成的交織圖案對RS 碼符號進行重排列。對此級聯(lián)碼采用的迭代譯碼基于成員碼的軟

2010-02-10 11:09:30 10

10 本文探討了無線通信中廣泛涉及的差錯控制問題,介紹了卷積碼的編譯碼原理。提出了一種卷積碼編碼,及其高速Viterbi譯碼的實現(xiàn)方案,對譯碼的各個組成部分作了分析,并在FPGA中實現(xiàn)

2010-07-21 17:20:04 22

22 對光碼分多址(OCDMA)的誤碼特性和卷積碼進行研究,根據(jù)兩者的特點提出了一種新的基于OCDMA多址干擾信道模型的卷積碼譯碼方法。針對這種新型卷積碼譯碼方法的抗誤碼性和譯

2010-08-26 16:40:22 17

17 針對固定碼長Turbo碼適應(yīng)性差的缺點,以LTE為應(yīng)用背景,提出了一種幀長可配置的Turbo編譯碼器的FPGA實現(xiàn)方案。該設(shè)計可以依據(jù)具體的信道環(huán)境和速率要求調(diào)節(jié)信息幀長,平衡譯碼性

2010-11-11 16:07:59 26

26 譯碼器

譯碼是編碼的逆過程,即將某個二進制翻譯成電路的某種狀態(tài)。實現(xiàn)譯碼操作的電路稱為譯碼器。

2008-09-27 12:59:06 14199

14199

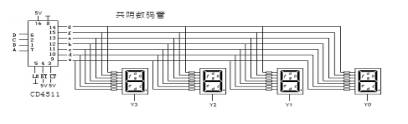

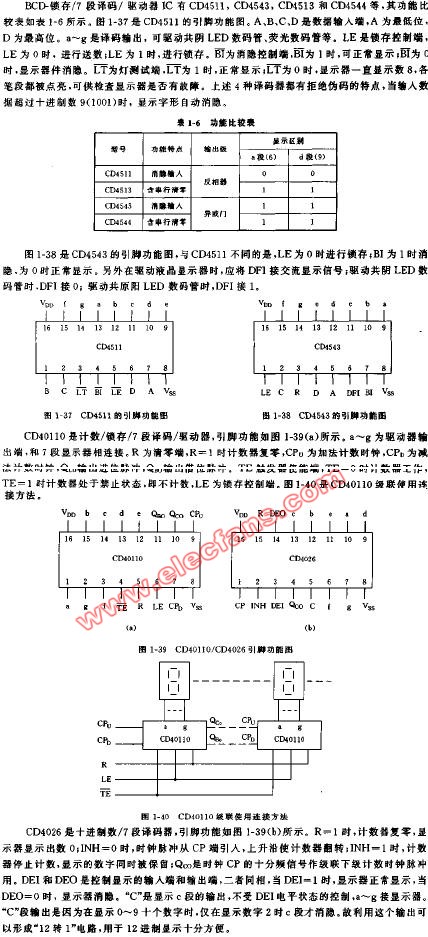

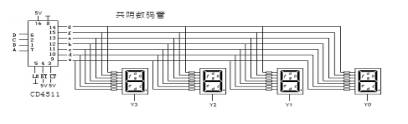

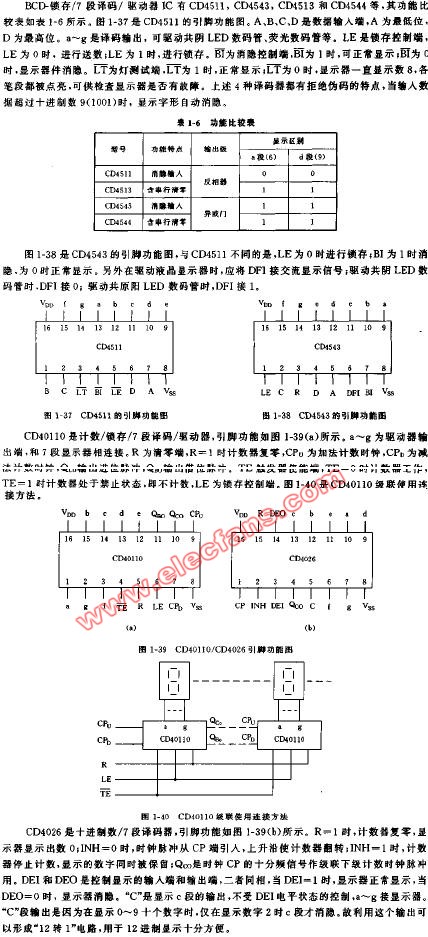

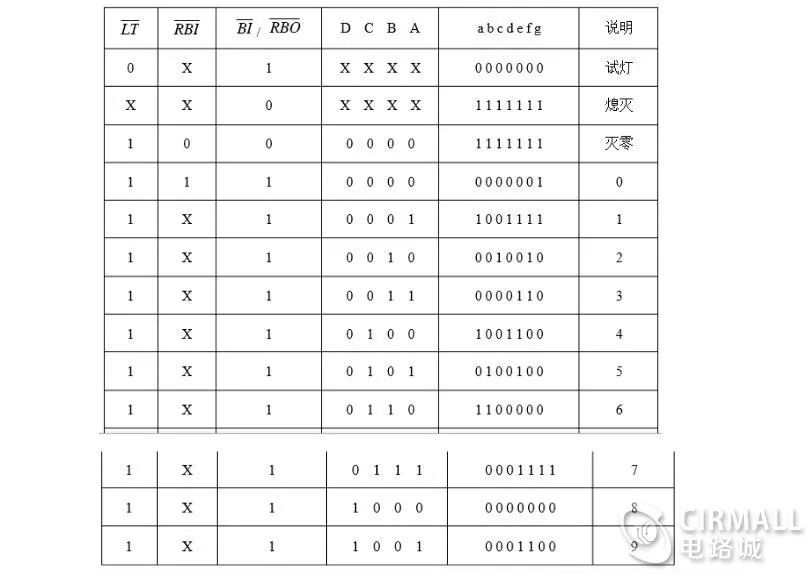

CD4511是一個用于驅(qū)動共陰極 LED (數(shù)碼管)顯示器的 BCD 碼—七段碼譯碼器,特點如下:

具有BCD轉(zhuǎn)換、消隱和鎖存控制

2008-09-27 13:18:12 78575

78575

數(shù)碼譯碼器的應(yīng)用:譯碼器課件ppt

2008-12-17 14:31:20 1215

1215

顯示譯碼器的應(yīng)用:

2008-12-17 14:35:06 1511

1511

譯碼器/數(shù)據(jù)分配器

一、譯碼器的定義及功能

譯碼是編碼的逆過程,它的功能是將具有特定含義的二進制碼進行辨別,并轉(zhuǎn)換成控制

2009-04-07 10:22:53 18412

18412

譯碼器的定義及功能

譯碼是編碼的逆過程,它的功能是將具有特定含義的二進制碼進行辨別,并轉(zhuǎn)換成控制信號,具有譯碼功能的邏輯電路稱為譯碼器

2009-04-07 10:23:42 20653

20653

集成電路譯碼器

1.74138集成譯碼器

上圖為常用的集成譯碼器74138,其功

2009-04-07 10:24:17 9766

9766

譯碼器,譯碼器是什么意思

譯碼器是組合邏輯電路的一個重要的器件,其可以分為:變量譯碼和顯示譯碼兩類。 變量譯碼一

2010-03-08 16:32:18 5784

5784 卷積碼/Viterbi譯碼,卷積碼/Viterbi譯碼是什么意思

卷積碼在一個二進制分組碼(n,k)當中,包含k個信息位,碼組長度為n,每個碼組的(

2010-03-18 14:09:21 2453

2453 卷積碼,卷積碼是什么意思

卷積碼在一個二進制分組碼(n,k)當中,包含k個信息位,碼組長度為n,每個碼組的(n-k)個校驗位僅與本碼組的k個信息

2010-03-19 16:46:24 2200

2200 卷積碼,什么是卷積碼

卷積碼在一個二進制分組碼(n,k)當中,包含k個信息位,碼組長度為n,每個碼組的(n-k)個校驗位僅與本碼組的k個信息位

2010-04-03 12:11:06 7611

7611 Turbo碼雖然具有優(yōu)異的譯碼性能,但是由于其譯碼復(fù)雜度高,譯碼延時大等問題,嚴重制約了Turbo碼在高速通信系統(tǒng)中的應(yīng)用。因此,如何設(shè)計一個簡單有效的譯碼器是目前Turb

2010-11-25 10:10:26 2375

2375

本文設(shè)計實現(xiàn)了一種支持WIMAX標準的碼長、碼率可配置LDPC碼譯碼器,通過設(shè)計一種基于串行工作模式的運算單元,實現(xiàn)了對該標準中所有碼率的支持

2011-06-08 09:52:17 2537

2537

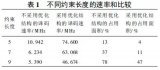

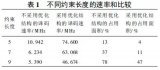

本文設(shè)計的譯碼器,利用Tail-biting卷積碼的循環(huán)特性,采用固定延遲的算法與維特比算法結(jié)合,在FPGA上實現(xiàn)和驗證,能達到135.78 MHz時鐘

2011-08-05 11:57:37 5423

5423

本文主要對卷積碼編碼和Viterbi譯碼進行MATLAB實現(xiàn),并在此基礎(chǔ)上分析移位寄存器對糾錯能力的影響。論文首先根據(jù)MATLAB的存儲特點及函數(shù)特征,主要介紹卷積編碼的原理,同時給出MA

2012-01-13 16:56:57 39

39 文中提出的卷積碼譯碼Matlab仿真方案,旨在用Viterbi譯碼實現(xiàn)對卷積碼譯碼的功能。仿真結(jié)果表明,維特比是一種良好的譯碼方式。

2012-03-22 17:21:11 58

58 本文介紹了 RS[ 255, 223 ]編譯碼器的 FPGA設(shè)計和基于線形反饋移位寄存器的編碼器設(shè)計 , 以及由伴隨式計算、關(guān)鍵方程求解、錢氏搜索、Forney算法等功能模塊組成的譯碼器。為了實現(xiàn)簡單

2012-05-22 10:43:40 45

45 介紹了符合CCSDS標準的RS(255,223)碼譯碼器的硬件實現(xiàn)結(jié)構(gòu)。譯碼器采用8位并行時域譯碼算法,主要包括了修正后的無逆BM迭代譯碼算法,錢搜索算法和Forney算法。采用了三級流水線結(jié)構(gòu)實現(xiàn)

2013-01-25 16:43:46 68

68 截短Reed_Solomon碼譯碼器的FPGA實現(xiàn)

2016-05-11 11:30:19 11

11 編碼與交織相結(jié)合的時頻編碼方案進行錯誤糾正[1]。在水聲通信中,糾錯編碼是不可或缺的技術(shù)之一。 目前通常采用的編碼方案有卷積碼、Turbo碼和LDPC碼等。后兩者具有接近香農(nóng)限的性質(zhì),在水聲OFDM系統(tǒng)中都表現(xiàn)出很好的糾錯特

2017-10-30 11:00:32 2

2 為了解決在RS譯碼中存在的譯碼過程復(fù)雜、譯碼速度慢和專用譯碼器價格高等問題,以RS(255,239)碼為例,采用了基于改進的無求逆運算的Berlekamp-Massey( BM)迭代算法。結(jié)合FP

2017-11-07 15:27:06 15

15 量化位數(shù)。然后基于該算法和這3個參數(shù)設(shè)計了一種全新的、高速部分并行的DSC譯碼器。該譯碼器最大限度地實現(xiàn)了譯碼效率、譯碼復(fù)雜度、FPGA資源利用率之間的平衡,并在Xilinx XC7VX485T芯片上實現(xiàn)了該譯碼器,其吞吐率可達197 Mb/s。

2017-11-16 12:59:01 3910

3910

該文通過對低密度校驗(LDPC)碼的編譯碼過程進行分析,提出了一種基于FPGA 的LDPC 碼編譯碼器聯(lián)合設(shè)計方法,該方法使編碼器和譯碼器共用同一校驗計算電路和復(fù)用相同的RAM 存儲塊,有效減少

2017-11-22 07:34:01 5141

5141

新一代移動通信系統(tǒng)目前主要采用多載波傳輸技術(shù), 基帶傳輸速率較3G 有很大提高, 一般要求業(yè)務(wù)速率能達到30 Mb/ s 以上。約束長度卷積碼以及Viterbi譯碼器由于其性能和實現(xiàn)的優(yōu)點, 在

2019-10-06 10:16:00 3521

3521

已全部加載完成

電子發(fā)燒友App

電子發(fā)燒友App

評論