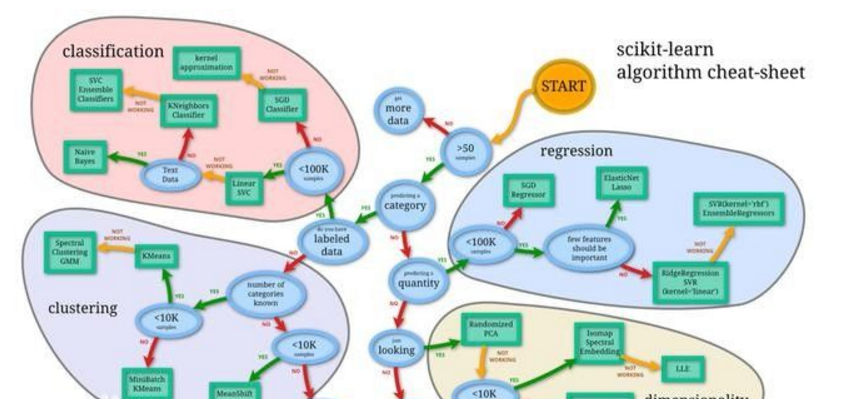

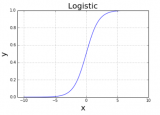

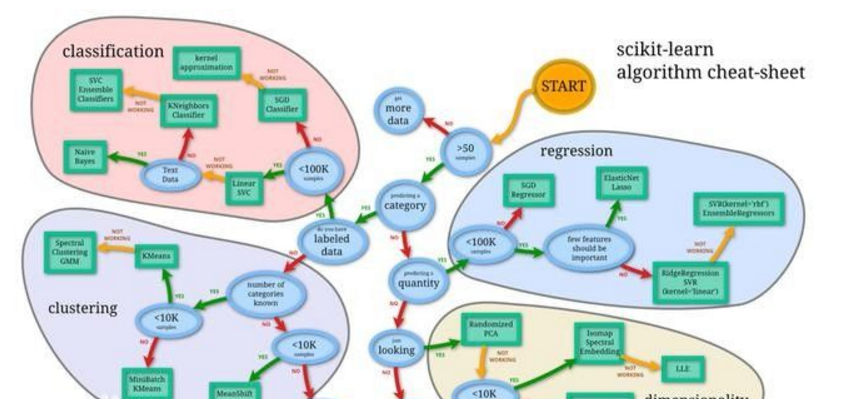

在這篇文章中,分享一些最常用的機(jī)器學(xué)習(xí)算法。

2017-10-14 14:24:00 9701

9701

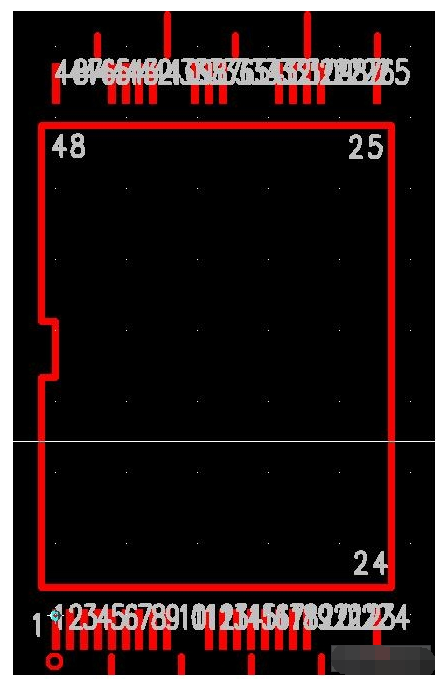

時(shí)序分析是FPGA設(shè)計(jì)中永恒的話題,也是FPGA開(kāi)發(fā)人員設(shè)計(jì)進(jìn)階的必由之路。慢慢來(lái),先介紹時(shí)序分析中的一些基本概念。

2022-10-21 09:28:58 4570

4570 本文調(diào)研了一些對(duì)OpenMP優(yōu)化的方式。

2022-11-22 09:36:01 1466

1466 分享一些EMC標(biāo)準(zhǔn)電路,可以收藏參考,主要是以下 32 種。

2023-07-06 09:22:20 1491

1491

高質(zhì)量的verilog代碼至少需要包含以下幾個(gè)要素:可讀性、功能、性能、標(biāo)準(zhǔn)化、穩(wěn)定性、可定位。

2023-07-18 10:09:07 1899

1899

Verilog阻塞和非阻塞原理分析在Verilog語(yǔ)言最難弄明白的結(jié)構(gòu)中“非阻塞賦值”要算一個(gè)。甚至是一些很有經(jīng)驗(yàn)的工程師也不完全明白“非阻塞賦值”在仿真器(符合IEEE標(biāo)準(zhǔn)的)里是怎樣被設(shè)定執(zhí)行

2009-11-23 12:02:57

可以掌握復(fù)雜數(shù)字系統(tǒng)的設(shè)計(jì)和驗(yàn)證方法。在中國(guó)大陸和***地區(qū)、美國(guó)和日本的IC設(shè)計(jì)公司中,無(wú)論做設(shè)計(jì)的和做驗(yàn)證工作的工程師們,近10年來(lái),選用Verilog語(yǔ)言設(shè)計(jì)數(shù)字系統(tǒng)的工程師日益增加。目前EDA

2012-02-02 14:30:15

ALTERA關(guān)于CCD的一些verilog實(shí)驗(yàn)程序

2023-09-26 08:03:28

一:基本Verilog中的變量有線網(wǎng)類型和寄存器類型。線網(wǎng)型變量綜合成wire,而寄存器可能綜合成WIRE,鎖存器和觸發(fā)器。二:verilog語(yǔ)句結(jié)構(gòu)到門級(jí)的映射1、連續(xù)性賦值:assign連續(xù)性

2012-02-24 10:37:21

本文討論了一些System Verilog問(wèn)題以及相關(guān)的SystemVerilog 語(yǔ)言參考手冊(cè)規(guī)范。正確理解這些規(guī)格將有助于System Verilog用戶避免意外的模擬結(jié)果。

2020-12-11 07:19:58

本文討論了一些System Verilog問(wèn)題以及相關(guān)的SystemVerilog 語(yǔ)言參考手冊(cè)規(guī)范。正確理解這些規(guī)格將有助于System Verilog用戶避免意外的模擬結(jié)果。

2020-12-24 07:07:04

在嵌入式系統(tǒng)的編程中,內(nèi)存操作是我們常用到的,但往往也是易錯(cuò)的地方,怎么避免呢,今天給大家分享一些相關(guān)的避坑指南。數(shù)據(jù)指針...

2021-12-17 07:18:55

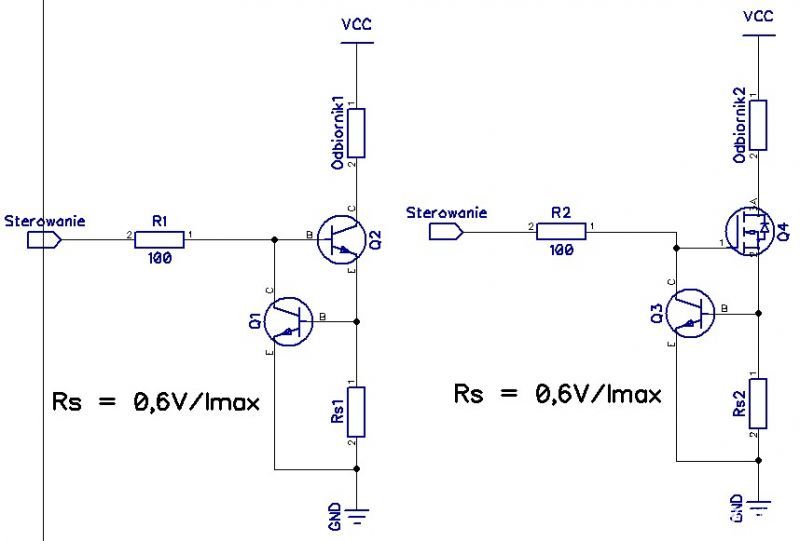

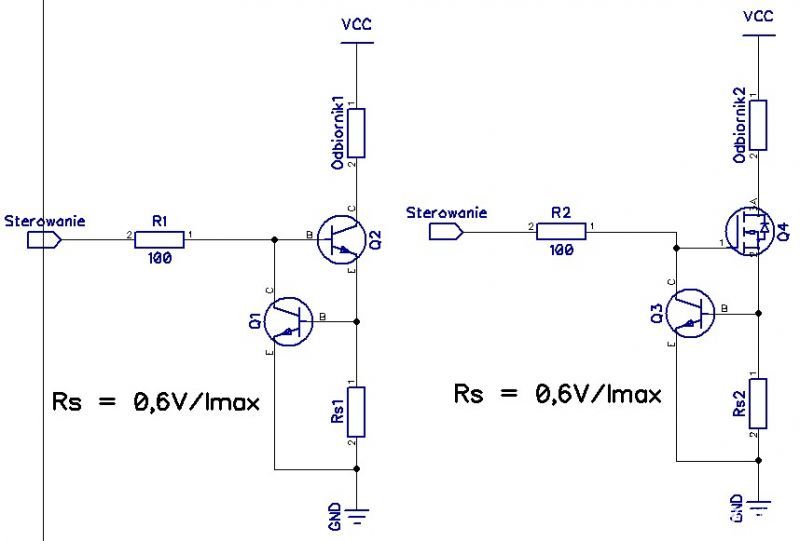

在并聯(lián)使用MOS存在一些問(wèn)題,那我們要怎樣做才能避免這些問(wèn)題?

首先,器件的一致性一定要好。

在功率MOSFET多管并聯(lián)時(shí),器件內(nèi)部參數(shù)的微小差異就會(huì)引起并聯(lián)各支路電流的不平衡而導(dǎo)致單管過(guò)流損壞。

其次是功率。如果功率高于25%,MOS發(fā)熱嚴(yán)重,性能會(huì)急劇下降,因此在設(shè)計(jì)時(shí)需要對(duì)MOS進(jìn)行降額使用。

2025-12-10 08:19:21

為了避免在一些用于測(cè)試 ESP8266 固件的串行終端和一些閃存編程工具之間切換,我制作了自己的小 win 程序,它將這兩個(gè)任務(wù)合并到一個(gè) exe 中。

如果 USB2UART 橋的 RTS

2023-05-24 07:39:04

請(qǐng)問(wèn)如果將蜂鳥(niǎo)的risc-v移植到其他的fpga中想實(shí)現(xiàn)一些外設(shè)功能有什么辦法?可以不用操作系統(tǒng)直接添加verilog代碼嗎?

2025-11-10 06:35:28

嗨,大家好!當(dāng)有一些無(wú)效數(shù)據(jù)時(shí),你知道是否有辦法避免在矩形圖上出現(xiàn)十字?謝謝! 以上來(lái)自于谷歌翻譯 以下為原文Hi everyone! Do you know if there is a way

2019-03-25 10:17:59

求大佬分享一些System Verilog的學(xué)習(xí)經(jīng)驗(yàn)

2021-06-21 06:29:54

圓點(diǎn)去掉了,綠色箭頭(調(diào)試)變?yōu)榘咨缓筮x擇continue,白色箭頭去掉,調(diào)試完成。以下是一些常用的調(diào)試命令:-------------------------------------轉(zhuǎn)張衛(wèi)國(guó)

2012-01-13 16:07:41

Verilog HDL的初學(xué)者問(wèn)一些相似的問(wèn)題,諸如如何實(shí)現(xiàn)除法、開(kāi)根號(hào),如何寫循環(huán)語(yǔ)句等等。在這個(gè)論壇上,也時(shí)常能看到一些網(wǎng)友提出這一類的問(wèn)題。對(duì)于這些問(wèn)題,首先要明確的是VHDL和Veriglog并非是針對(duì)

2019-03-27 07:00:00

首先我說(shuō)一下,這篇文章不是系統(tǒng)地講述某個(gè)電路設(shè)計(jì),而是為了記錄一些關(guān)于電路設(shè)計(jì)上的一些知識(shí),方便我查看。電源設(shè)計(jì)輸出端采用了常見(jiàn)的電容去耦方法,一大一小兩電容(相差兩個(gè)數(shù)量級(jí))。(目的:降低電源噪聲

2021-11-11 06:48:22

本文主要講述了實(shí)時(shí)多任務(wù)系統(tǒng)中的一些基本概念。

2009-04-22 16:17:36 15

15 隨著FPGA 技術(shù)和自動(dòng)設(shè)計(jì)工具的進(jìn)步,數(shù)字電子系統(tǒng)設(shè)計(jì)的方法正在發(fā)生變化。越來(lái)越多的工程師開(kāi)始使用硬件描述語(yǔ)言和高級(jí)綜合工具進(jìn)行設(shè)計(jì)。Verilog HDL 作為一種流行的硬件

2009-09-02 09:27:57 89

89 Verilog HDL 華為入門教程

本文主要介紹了Verilog HDL 語(yǔ)言的一些基本知識(shí),目的是使初學(xué)者能夠迅速掌握HDL設(shè)計(jì)方法,初步了解并掌握Verilog HDL語(yǔ)言的基本要素,能

2010-02-11 08:35:38 141

141 Verilog HDL入門教程(華為絕密資料)

本文主要介紹了Verilog HDL 語(yǔ)言的一些基本知識(shí),目的是使初學(xué)者能夠迅速掌握HDL設(shè)計(jì)方法,初步了解并掌握Verilog HDL語(yǔ)言的

2010-04-02 11:52:21 0

0

CAM 350一些基本操作

G

2007-01-25 11:26:08 2731

2731 如何處理實(shí)際布線中的一些理論沖突的問(wèn)題

基本上, 將模/數(shù)地分割隔離是對(duì)的。 要注意的是信號(hào)走線盡量

2009-03-20 13:54:25 720

720

關(guān)于中、高壓變頻器的一些知識(shí)

摘要:中、高壓變頻器主電路不像低壓變頻器那樣,至今還沒(méi)有統(tǒng)一的拓?fù)浣Y(jié)構(gòu),它們從功率

2009-07-08 10:53:59 2983

2983

Protel在線教程:SCH的一些高級(jí)設(shè)置和常用技巧

前面我們走馬觀花的對(duì)SCH做了一些操作,這回我們來(lái)看看SCH中的一些高級(jí)設(shè)置和操作技巧 1.看看如何對(duì)SCH的操作環(huán)境

2010-04-22 09:00:02 1573

1573

linux安裝的一些軟件,jdk和tomcat一類的。

2015-11-09 17:39:40 0

0 延續(xù)28335一些例子延續(xù)28335一些例子

2016-02-17 17:12:30 8

8 cadence畫板中遇到的一些問(wèn)題,在這里分享給大家,多多指教

2016-02-25 16:01:37 0

0 kali一些基礎(chǔ)安裝總結(jié),有興趣的同學(xué)可以參考下載看看啦。

2016-03-29 11:12:36 0

0 簡(jiǎn)單的Verilog ,不是很全面,但是基本的還是有的,里面只有一些 基本的元器件。

2016-05-18 14:53:57 0

0 本文主要介紹了Verilog HDL 語(yǔ)言的一些基本知識(shí),目的是使初學(xué)者能夠迅速掌握HDL設(shè)計(jì)方法,初步了解并掌握Verilog HDL語(yǔ)言的基本要素,能夠讀懂簡(jiǎn)單的設(shè)計(jì)代碼并能夠進(jìn)行一些簡(jiǎn)單設(shè)計(jì)的Verilog HDL建模。

2016-07-15 15:27:00 0

0 電子專業(yè)單片機(jī)相關(guān)知識(shí)學(xué)習(xí)教材資料——電路的一些基本概念

2016-08-22 16:18:03 0

0 本文檔詳細(xì)介紹分析了關(guān)于PID的一些常用知識(shí)

2016-08-29 14:22:42 2

2 電子專業(yè)單片機(jī)相關(guān)知識(shí)學(xué)習(xí)教材資料——電路的一些基本概念

2016-10-10 14:17:59 0

0 時(shí)序分析時(shí)FPGA設(shè)計(jì)中永恒的話題,也是FPGA開(kāi)發(fā)人員設(shè)計(jì)進(jìn)階的必由之路。慢慢來(lái),先介紹時(shí)序分析中的一些基本概念。

2017-02-11 19:08:29 4953

4953

一些電子公司的簡(jiǎn)稱

2022-07-10 14:21:26 20

20 Autium_designer的一些經(jīng)驗(yàn)

2017-02-28 21:16:42 0

0 一些制作1969的分享經(jīng)驗(yàn)

2017-03-04 18:25:42 38

38 PCB設(shè)計(jì)過(guò)程中的一些問(wèn)題和一些技巧分享 1、如何利用層次圖繪制電路原理圖? 答:層次原理是一種模塊化的設(shè)計(jì)方法,設(shè)計(jì)者可以將設(shè)計(jì)的系統(tǒng)劃分為多個(gè)子系統(tǒng),子系統(tǒng)又可以劃分為若干個(gè)功能模塊,功能模塊再

2017-09-07 20:08:33 17

17 VICOR模塊的一些基本應(yīng)用

2017-11-24 11:42:48 17

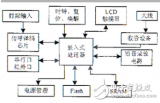

17 雖然沒(méi)有做過(guò)產(chǎn)業(yè)調(diào)查,但從我所見(jiàn)和所招聘人員,從事嵌入式行業(yè)的工程師,要么缺乏理論知識(shí),要么缺乏實(shí)踐經(jīng)驗(yàn)。很少兩者兼?zhèn)涞摹>科湓颍€是中國(guó)的大學(xué)教育的問(wèn)題。這里不探討這個(gè)問(wèn)題,避免口水戰(zhàn)。我想列出我實(shí)踐中的幾個(gè)例子。引起大家在嵌入式中做項(xiàng)目時(shí)對(duì)一些問(wèn)題的關(guān)注。

2018-01-05 11:31:12 4251

4251

在本教程中,我們會(huì)學(xué)習(xí)管理 docker 容器的一些命令。

2018-01-22 11:56:52 4733

4733 這是一篇八千字的長(zhǎng)文,是一些算法筆記的整理集合,希望能給你幫助。

2018-06-18 11:41:00 18273

18273 此文件時(shí)間的Verilog數(shù)字系統(tǒng)設(shè)計(jì)的一些案例和教程,適合初學(xué)者學(xué)習(xí)和參考。

2018-06-25 08:00:00 9

9 個(gè)人感受:這種做法可以從一開(kāi)始就避免一些bug的出現(xiàn),或更容易解決一些bug。構(gòu)造函數(shù)+Init()函數(shù)初始化的方式與只用構(gòu)造函數(shù)的方法相比,對(duì)計(jì)算機(jī)來(lái)說(shuō)他們是沒(méi)有區(qū)別的,但是人是會(huì)犯錯(cuò)的,這一條代碼規(guī)范在某種程度上避免了一些人為錯(cuò)誤,這個(gè)在開(kāi)發(fā)中特別重要。

2018-09-27 17:54:41 9966

9966 人都會(huì)犯錯(cuò),PCB設(shè)計(jì)工程師自然也不例外。與一般大眾的認(rèn)知相反,只要我們能從這些錯(cuò)誤中學(xué)到教訓(xùn),犯錯(cuò)也不是一件壞事。

2018-10-18 08:51:11 40992

40992 在這篇文章中,我將展示一些由我自己開(kāi)發(fā)或是我在文章、博客、論壇、Kaggle和其他一些地方發(fā)現(xiàn)的方法,看看它們是如何在沒(méi)有大數(shù)據(jù)的情況下讓深度學(xué)習(xí)更好地完成我的任務(wù)的。其中許多方法都基于計(jì)算機(jī)視覺(jué)中廣泛使用的最佳實(shí)踐。

2018-11-19 17:39:26 7371

7371

熟習(xí)一門硬件設(shè)想言語(yǔ)(VHDL或Verilog HDL),由于不論在哪種運(yùn)用范圍,HDL言語(yǔ)都是FPGA開(kāi)拓的根底。目前國(guó)際運(yùn)用Verilog HDL言語(yǔ)的開(kāi)拓職員較多一些,因而引薦讀者進(jìn)修Verilog HDL。正因如此,本書的實(shí)例都經(jīng)過(guò)Verilog HDL完成,并在附錄中給出其扼要的語(yǔ)法闡明。

2019-01-17 11:44:05 25107

25107

本文主要介紹了Verilog HDL 語(yǔ)言的一些基本知識(shí),目的是使初學(xué)者能夠迅速掌握HDL 設(shè)計(jì)方法,初步了解并掌握Verilog HDL語(yǔ)言的基本要素,能夠讀懂簡(jiǎn)單的設(shè)計(jì)代碼并能夠進(jìn)行一些簡(jiǎn)單設(shè)計(jì)的Verilog HDL建模。

2019-02-11 08:00:00 102

102 學(xué)習(xí)FPGA,先要有數(shù)電知識(shí),最好有點(diǎn)C語(yǔ)言,,學(xué)好硬件描述語(yǔ)言,verilog或者vhdl。在有這些基礎(chǔ)上,做一些小的模塊不斷積累。這里不再贅述。

2019-02-14 14:24:03 1056

1056 本文檔的主要內(nèi)容詳細(xì)介紹的是Verilog HDL語(yǔ)言組合邏輯設(shè)計(jì)方法以及QuartusII軟件的一些高級(jí)技巧。

2019-07-03 17:36:12 20

20 事實(shí)上,有一些電源技巧可以阻止終端電子產(chǎn)品遭遇問(wèn)題從一開(kāi)始就是惡劣的環(huán)境,即在PCB制造或PCBA制造過(guò)程中。本文將提供一些電源技巧,幫助電路板和組裝板在惡劣環(huán)境中更好地工作,主要從兩個(gè)方面來(lái)看:保形涂層和清潔。

2019-08-02 16:02:56 3892

3892 本文檔的主要內(nèi)容詳細(xì)介紹的是有關(guān)Verilog中的一些語(yǔ)法詳細(xì)資料說(shuō)明。

2019-07-25 17:08:33 2

2 不管是在生活還是工作中,每個(gè)人都會(huì)逐漸養(yǎng)成一些小習(xí)慣。壞習(xí)慣一旦形成就很難改正,所在在系統(tǒng)學(xué)習(xí) Linux 之前,給大家一些建議,刻意去培養(yǎng)一些好的習(xí)慣,對(duì)自己是很有利的。

2020-07-14 14:22:06 881

881 我們可以先理解樣板模塊中每一條語(yǔ)句的作用,然后對(duì)樣板模塊進(jìn)行綜合前和綜合后仿真,再獨(dú)立完成每一階段規(guī)定的練習(xí)。當(dāng)十個(gè)階段的練習(xí)做完后,便可以開(kāi)始設(shè)計(jì)一些簡(jiǎn)單的邏輯電路和系統(tǒng)。很快我們就能過(guò)渡

2020-10-10 08:00:00 1

1 本文檔的主要內(nèi)容詳細(xì)介紹的是電腦的一些硬件問(wèn)題講解。

2020-10-20 08:00:00 14

14 本文主要介紹了Verilog HDL 語(yǔ)言的一些基本知識(shí),目的是使初學(xué)者能夠迅速掌握HDL設(shè)計(jì)方法,初步了解并掌握Verilog HDL語(yǔ)言的基本要素,能夠讀懂簡(jiǎn)單的設(shè)計(jì)代碼并能夠進(jìn)行一些簡(jiǎn)單設(shè)計(jì)的語(yǔ)言的基本要素,能夠讀懂簡(jiǎn)單的設(shè)計(jì)代碼并能夠進(jìn)行一些簡(jiǎn)單設(shè)計(jì)的Verilog HDL建模。

2020-12-23 16:47:39 93

93 光端機(jī),就是光信號(hào)傳輸?shù)慕K端設(shè)備,我們?cè)谑褂玫倪^(guò)程中難免會(huì)碰到一些問(wèn)題,接下來(lái)杭州飛暢的小編為大家詳細(xì)列舉了光端機(jī)在使用過(guò)程中遇到的一些常見(jiàn)問(wèn)題以及對(duì)應(yīng)的解決方案,感興趣的朋友就一起來(lái)看看吧!(1)

2020-12-25 14:54:18 1579

1579 想你非常有必要嘗試一下。 我接觸Android開(kāi)發(fā)也有幾年了,前段時(shí)間公司大力推廣Flutter技術(shù),所以有幸嘗試了一下。本人一直信奉善于總結(jié)是不斷進(jìn)步的不二法寶,這樣你才能不斷的超越同行,不被裁員,所以在此準(zhǔn)備以切身體驗(yàn)提供一些快速掌握Flutter的一些技巧。 轉(zhuǎn)變

2021-02-12 11:46:00 2542

2542

系統(tǒng)的給大家列出機(jī)械設(shè)計(jì)中各個(gè)流程所用的一些軟件。

2021-03-15 10:50:36 3736

3736 感謝各位參加我們的 2021 年線上 I/O 直播大會(huì)!雖然沒(méi)能面對(duì)面交流,但我們?nèi)韵M衲甏舜位顒?dòng)的便利性更勝以往。在本文中,我們將總結(jié)主題演講中涉及的一些更新。您可以觀看下面的主題演講視頻,并在

2021-05-28 14:19:39 2248

2248 一些經(jīng)典的有源濾波電路圖下載。

2021-06-07 14:29:57 28

28 的完整 Verilog 代碼 。 在這個(gè)FPGA Verilog項(xiàng)目中,一些簡(jiǎn)單的處理操作都是在Verilog中實(shí)現(xiàn)的,比如反相、亮度控制和閾值操作。圖像處理操作由“parameter.v”文件選擇

2021-09-23 15:50:21 7240

7240 一些簡(jiǎn)單趣味小電子制作教程

2021-09-26 14:05:36 31

31 Vivado 仿真器支持混合語(yǔ)言項(xiàng)目文件及混合語(yǔ)言仿真。這有助于您在 VHDL 設(shè)計(jì)中包含 Verilog 模塊,反過(guò)來(lái)也是一樣。 本文主要介紹使用 Vivado 仿真器進(jìn)行混合語(yǔ)言仿真的一些要點(diǎn)

2021-10-28 16:24:49 3810

3810 PCB設(shè)計(jì)論壇中的 遵守/避免布線法則,使得PCB設(shè)計(jì)者在這些規(guī)則也許不適用的地方要么遵守,要么忽略他們。一些情況下,這未必造成電路板設(shè)

2021-11-01 10:33:52 3613

3613 大家好,我是51新手,學(xué)習(xí)完入門之后對(duì)51單片機(jī)的中斷進(jìn)行一些總結(jié)。有些像我一樣的新手學(xué)習(xí)完中斷之后對(duì)其中的一些寄存器模模糊糊,不知道他們的功能,在寫程序時(shí)也十分吃力,因此,我想對(duì)此寫一些個(gè)人的想法

2021-11-24 16:06:08 1

1 在單片機(jī)的開(kāi)發(fā)過(guò)程中,最常用的外設(shè)就是串口了,是用來(lái)進(jìn)行bug糾錯(cuò)、log輸出的常用工具,也是用來(lái)與外部通訊的常見(jiàn)協(xié)議之一。 但是在使用串口的過(guò)程中難免會(huì)遇到一些問(wèn)題,下面就我在工作遇到的一些

2021-12-24 18:51:32 2

2 單片機(jī)編程中的一些時(shí)序問(wèn)題本文的的delay原型:void delay(unsigned int t){ while(t--);//10us}今天在單片機(jī)編程時(shí)遇到了一些問(wèn)題:LCD1602的第二行

2022-01-17 12:30:50 1

1 “ 本文主要分享了在Verilog設(shè)計(jì)過(guò)程中一些經(jīng)驗(yàn)與知識(shí)點(diǎn),主要包括循環(huán)語(yǔ)句(forever、repeat、while和for)、運(yùn)算符。”

2022-03-15 11:41:58 6002

6002 “ 本文主要分享了在Verilog設(shè)計(jì)過(guò)程中一些經(jīng)驗(yàn)與知識(shí)點(diǎn),主要包括塊語(yǔ)句、阻塞賦值和非阻塞賦值 以及結(jié)構(gòu)說(shuō)明語(yǔ)句(initial, always, task, function)。”

2022-03-15 12:19:31 2954

2954 “ 本文主要分享了在Verilog設(shè)計(jì)過(guò)程中一些經(jīng)驗(yàn)與知識(shí)點(diǎn),主要包括Verilog仿真時(shí)常用的系統(tǒng)任務(wù)、雙向端口的使用(inout)、邊沿檢測(cè)”

2022-03-15 13:34:56 3146

3146 有時(shí)候我們?yōu)榱私y(tǒng)一管理會(huì)把一些變量放到 yml 配置文件中

2022-03-16 12:05:42 1851

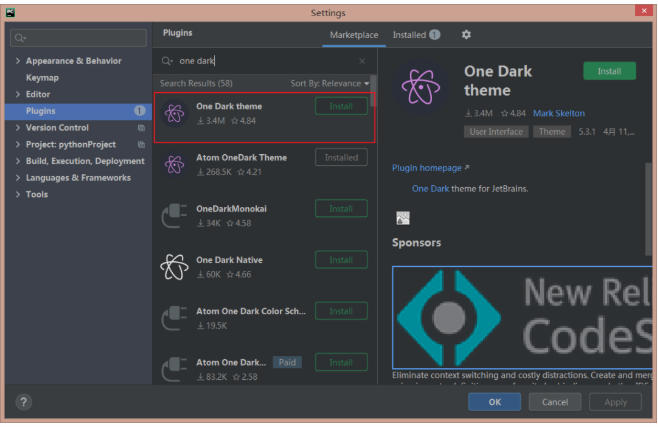

1851 首先聲明本人并非Keil黑,本期純吐槽下在使用Keil過(guò)程中的一些不順手的地方,也極有可能講的并不全面,不客觀,望見(jiàn)諒,輕拍,也歡迎評(píng)論區(qū)討論。

2022-05-26 10:53:42 1851

1851 FPGA各位和數(shù)字IC設(shè)計(jì)崗位面試時(shí)常常會(huì)問(wèn)下verilog的一些基本概念,做了下整理,面試時(shí)一定用得上!

2022-07-07 09:51:10 2192

2192 Verilog HDL 入門教程

2022-08-08 14:36:22 6

6 本文將為初學(xué)者提供一些實(shí)用的布局、提示和技巧,可以幫助您避免事故或解決各種問(wèn)題。該系列將不定期發(fā)布。

2022-08-09 16:56:08 2047

2047

PPT主要介紹了大功率IGBT模塊應(yīng)用中的一些技術(shù),包括參數(shù)解讀、器件選型、驅(qū)動(dòng)技術(shù)、保護(hù)方法以及失效分析等。

2022-09-05 11:36:39 3143

3143 今天再次看到這個(gè)問(wèn)題,我也有了一些新的理解和感觸,臨時(shí)回顧了一下 get 與 post 的請(qǐng)求的一些區(qū)別。

2022-09-07 10:00:11 1983

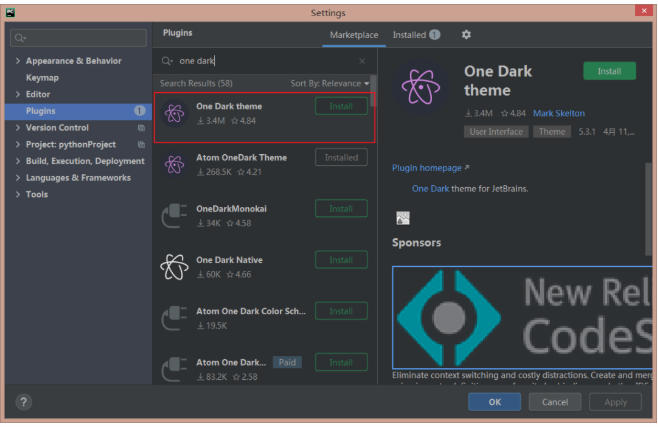

1983 在眾多Python的編輯器中,最為推薦的就是PyCharm,帶有一整套可以幫助用戶在使用Python語(yǔ)言開(kāi)發(fā)時(shí)提高效率的工具,比如調(diào)試、語(yǔ)法高亮、項(xiàng)目管理、代碼跳轉(zhuǎn)、智能提示等。此外PyCharm還提供了一些高級(jí)功能,以用于支持專業(yè)Web開(kāi)發(fā)。

2022-10-14 16:27:25 5364

5364

本文調(diào)研了一些對(duì)OpenMP進(jìn)行優(yōu)化的方法。

2022-10-18 09:44:08 2464

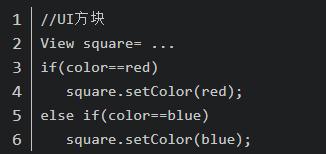

2464 寫代碼是給別人和多年后的自己看的。 關(guān)于Verilog代碼設(shè)計(jì)的一些風(fēng)格和方法之前也寫過(guò)一些Verilog有什么奇技淫巧?

2022-10-24 15:23:54 2309

2309 INCA的一些用法

2022-11-10 15:32:30 13970

13970 讀過(guò)上一篇文章“ARM NEON快速上手指南”之后,相信你已經(jīng)對(duì)ARM NEON編程有了基本的認(rèn)識(shí)。但在真正利用ARM NEON優(yōu)化程序性能時(shí),還有很多編程技巧和注意事項(xiàng)。本文將結(jié)合本人的一些開(kāi)發(fā)經(jīng)歷,介紹NEON編程中的一些常見(jiàn)優(yōu)化技巧,希望能對(duì)用戶在NEON實(shí)際開(kāi)發(fā)中有些借鑒意義。

2022-12-12 09:11:24 2903

2903 新技術(shù)星期二:邊緣計(jì)算可以解決一些計(jì)算問(wèn)題

2022-12-29 10:02:39 1316

1316 在Linux使用gcc編譯程序的時(shí)候,對(duì)于調(diào)試的語(yǔ)句還具有一些特殊的語(yǔ)法。

2023-06-01 09:03:22 505

505 RoHS是指限制在電子和電氣設(shè)備中使用有害物質(zhì)的指令,實(shí)施時(shí)按ROHS檢測(cè)標(biāo)準(zhǔn)執(zhí)行。但是,在實(shí)施的過(guò)程中,往往會(huì)出現(xiàn)很多誤區(qū)。今天就給大家詳細(xì)介紹一下ROHS檢測(cè)標(biāo)準(zhǔn)執(zhí)行中存在的誤區(qū)。現(xiàn)在,一些

2022-01-21 09:20:11 1953

1953

分享最近在學(xué)的數(shù)據(jù)采集的一些資料2

2023-08-21 10:36:30 2

2 在 Vim 編輯器中,有一些常用的指令可以幫助我們更高效地編輯文本。以下是一些在 gvim 中常用的指令

2023-10-10 15:47:06 3187

3187 由于一些板,尤其是U盤等面積很小的板,F(xiàn)LASH中只使用了為數(shù)不多的幾個(gè)PIN,為了可以讓其它PIN下面可以走線,增加GND網(wǎng)絡(luò)的面積,所以實(shí)際操作中要隱藏一些PIN。這就需要怎么操作呢!

2023-11-02 15:19:08 605

605

本文分享一些SystemVerilog的coding guideline。

2023-11-22 09:17:30 1391

1391

和執(zhí)行行為。雖然它們都可以用于設(shè)計(jì)和模擬電路行為,但它們?cè)谡Z(yǔ)義和用途上有一些重要的區(qū)別。 initial語(yǔ)句: initial語(yǔ)句通常用于初始化內(nèi)部變量和寄存器的值,并執(zhí)行仿真開(kāi)始時(shí)的初始操作。它只在仿真開(kāi)始時(shí)執(zhí)行一次,在設(shè)計(jì)中沒(méi)有持續(xù)的行為。 initial語(yǔ)句的基本形式是:

2024-02-22 16:09:27 4568

4568

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論