多年前,無(wú)線時(shí)代(Beamsky)發(fā)布了一篇文章關(guān)于DDR布線指導(dǎo)的一篇文章,當(dāng)時(shí)在網(wǎng)絡(luò)上很受歡迎,有很多同

2017-10-16 09:22:08 38670

38670

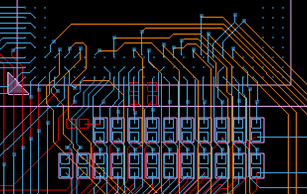

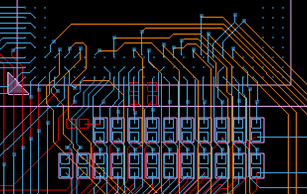

布線是PCB設(shè)計(jì)的重要組成部分,也是整個(gè)PCB設(shè)計(jì)中工作量最大和最耗時(shí)間的部分,工程師在進(jìn)行PCB布線工作時(shí),需要遵循一些基本的規(guī)則,如倒角規(guī)則、3W規(guī)則等。

2022-10-31 14:30:32 2107

2107 PCB設(shè)計(jì)布線(Layout)的好壞將直接影響到整個(gè)系統(tǒng)的性能,大多數(shù)高速的設(shè)計(jì)理論也要最終經(jīng)過(guò) Layout 得以實(shí)現(xiàn)并驗(yàn)證,由此可見(jiàn),布線在高速 PCB 設(shè)計(jì)中是至關(guān)重要的。下面將針對(duì)實(shí)際布線中可能遇到的一些情況,分析其合理性,并給出一些比較優(yōu)化的走線策略。

2016-07-18 14:07:10 48837

48837 28335未使用的一些GPIO口需要如何處理,如果現(xiàn)在已經(jīng)是懸空狀態(tài)的話,程序中如何配置,能夠讓外部可能引入的干擾最小?是配置成輸出口,然后輸出低嗎?

2020-06-04 15:44:53

有的,他們有著很理性的知識(shí),同時(shí)又帶著一些自我創(chuàng)作的情感去布線,布出來(lái)的線就頗為美觀有藝術(shù)感。 下面是一些好的布線技巧和要領(lǐng): 首先,先對(duì)做個(gè)基礎(chǔ)介紹,PCB的層數(shù)可以分為單層,雙層和多層的,單層現(xiàn)在

2018-09-18 15:55:57

本帖最后由 x3942832 于 2012-9-28 11:19 編輯

1. 如何處理實(shí)際布線中的一些理論沖突的問(wèn)題 問(wèn):在實(shí)際布線中,很多理論是相互沖突的;例如: 1。處理多個(gè)模/數(shù)地的接法

2012-09-28 11:15:18

以下問(wèn)題:

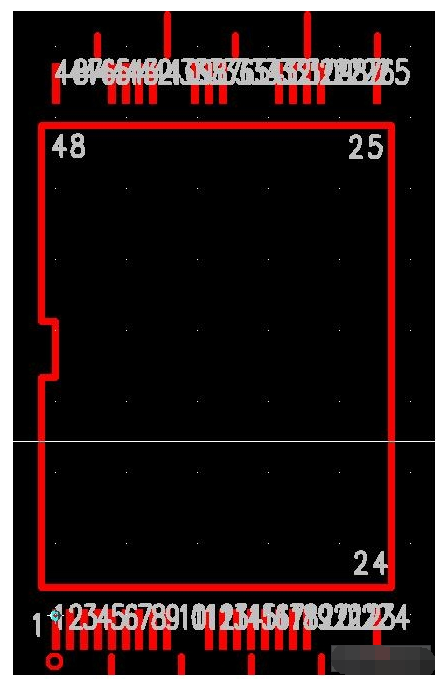

1)AD10200管腳1的作用是什么,在實(shí)際的電路使用中,應(yīng)該如何處理?

2)模擬信號(hào)輸入端是否為CMOS電路,A路、B路其中一路輸入懸空時(shí),懸空管腳如何正確的處理?

3)采樣時(shí)鐘

2023-12-22 06:15:58

你好,我公司正在用ADE7880做一個(gè)項(xiàng)目,遇到一些問(wèn)題。問(wèn)幾個(gè)基礎(chǔ)的問(wèn)題。希望能得到答復(fù)。謝謝! 1. 基波有效值寄存器只有一個(gè)電壓FVRMS和 FIRMS,如何讀三相每一項(xiàng)的基波值,是不是用

2018-12-18 09:10:01

問(wèn):在實(shí)際布線中,很多理論是相互沖突的;例如: 1。處理多個(gè)模/數(shù)地的接法:理論上是應(yīng)該相互隔離的,但在實(shí)際的小型化、高密度布線中,由于空間的局限或者絕對(duì)的隔離會(huì)導(dǎo)致小信號(hào)模擬地走線過(guò)長(zhǎng),很難

2019-07-18 08:17:32

有沒(méi)有辦法在智能插頭中處理去抖動(dòng)鍵?

我的意思是為了節(jié)省成本,添加 debounce 代碼更好,如果在硬件方面有一些想法會(huì)更好。

有人有一些與這種去抖動(dòng)相關(guān)的解決方案嗎?

或者有人曾經(jīng)應(yīng)用添加開(kāi)關(guān)并測(cè)量這個(gè)ESP8266如何處理去抖動(dòng)?

2024-07-08 08:23:17

I2C總線實(shí)際應(yīng)用中隱藏的一些問(wèn)題的探 I2C 如今已經(jīng)成為芯片間低速串行通信的事實(shí)標(biāo)準(zhǔn),被廣泛使用在消費(fèi)、控制類電子設(shè)備場(chǎng)合。本文就實(shí)際應(yīng)用中隱藏的一些簡(jiǎn)單問(wèn)題進(jìn)行討論。 [/hide]

2009-10-20 11:52:45

SI工程師給出的約束規(guī)則來(lái)完成布局布線的,這些也就是俗稱的“拉線工”。他們重復(fù)而機(jī)械的完成一塊塊PCB設(shè)計(jì),一段時(shí)間設(shè)計(jì)后,他們中的一些或許已經(jīng)有了這樣的一些經(jīng)驗(yàn):哪些要做等長(zhǎng),哪些要走粗、哪些要平行

2016-12-20 17:34:18

1、如何處理實(shí)際布線中的一些理論沖突的問(wèn)題問(wèn):在實(shí)際布線中,很多理論是相互沖突的;例如: 1。處理多個(gè)模/數(shù)地的接法:理論上是應(yīng)該相互隔離的,但在實(shí)際的小型化、高密度布線中,由于空間的局限或者絕對(duì)

2014-12-31 14:32:05

(signal integrity)及時(shí)間延遲(timing

delay)。

8、如何處理實(shí)際布線中的一些理論沖突的問(wèn)題

純分享貼,有需要可以直接下載附件獲取完整資料!

(如果內(nèi)容有幫助可以關(guān)注、點(diǎn)贊、評(píng)論支持一下哦~)

2025-05-21 17:21:41

、如何處理實(shí)際布線中的一些理論沖突的問(wèn)題1). 基本上, 將模/數(shù)地分割隔離是對(duì)的。 要注意的是信號(hào)走線盡量不要跨過(guò)有分割的地方(moat), 還有不要讓電源和信號(hào)的回流電流路徑(returning

2017-04-16 11:58:12

平行也是因?yàn)橐3植罘肿杩沟?b class="flag-6" style="color: red">一致性。若兩線忽遠(yuǎn)忽近, 差分阻抗就會(huì)不一致, 就會(huì)影響信號(hào)完整性(signal integrity)及時(shí)間延遲(timing delay)。8、如何處理實(shí)際布線中的一些

2014-08-27 10:24:12

實(shí)際布線中的一些理論沖突的問(wèn)題1. 基本上, 將模/數(shù)地分割隔離是對(duì)的。 要注意的是信號(hào)走線盡量不要跨過(guò)有分割的地方(moat), 還有不要讓電源和信號(hào)的回流電流路徑(returning

2012-08-05 19:33:41

忽遠(yuǎn)忽近, 差分阻抗就會(huì)不一致, 就會(huì)影響信號(hào)完整性(signal integrity)及時(shí)間延遲(timing delay)8、如何處理實(shí)際布線中的一些理論沖突的問(wèn)題1. 基本上, 將模/數(shù)地分割

2021-09-19 09:42:31

(signal integrity)及時(shí)間延遲(timing delay)。 8、如何處理實(shí)際布線中的一些理論沖突的問(wèn)題 1. 基本上, 將模/數(shù)地分割隔離是對(duì)的。 要注意的是信號(hào)走線盡量不要跨過(guò)有分割

2018-08-30 10:49:23

完整性(signal integrity)及時(shí)間延遲(timing delay)。8、如何處理實(shí)際布線中的一些理論沖突的問(wèn)題基本上, 將模/數(shù)地分割隔離是對(duì)的。 要注意的是信號(hào)走線盡量不要跨過(guò)有分割

2015-12-16 16:40:24

delay)。8、如何處理實(shí)際布線中的一些理論沖突的問(wèn)題1. 基本上, 將模/數(shù)地分割隔離是對(duì)的。 要注意的是信號(hào)走線盡量不要跨過(guò)有分割的地方(moat), 還有不要讓電源和信號(hào)的回流電流路徑

2017-07-07 13:03:12

忽遠(yuǎn)忽近, 差分阻抗就會(huì)不一致, 就會(huì)影響信號(hào)完整性(signal integrity)及時(shí)間延遲(timing delay)8、如何處理實(shí)際布線中的一些理論沖突的問(wèn)題1. 基本上, 將模/數(shù)地分割

2015-10-30 15:25:15

)。 8、如何處理實(shí)際布線中的一些理論沖突的問(wèn)題 1. 基本上, 將模/數(shù)地分割隔離是對(duì)的。 要注意的是信號(hào)走線盡量不要跨過(guò)有分割的地方(moat), 還有不要讓電源和信號(hào)的回流電流路徑

2015-01-09 11:14:05

1. 如何處理實(shí)際布線中的一些理論沖突的問(wèn)題 問(wèn):在實(shí)際布線中,很多理論是相互沖突的;例如: 1。處理多個(gè)模/數(shù)地的接法:理論上是應(yīng)該相互隔離的,但在實(shí)際的小型化、高密度布線中,由于空間的局限或者

2014-10-24 11:00:08

integrity)及時(shí)間延遲(timing delay)。8、如何處理實(shí)際布線中的一些理論沖突的問(wèn)題基本上, 將模/數(shù)地分割隔離是對(duì)的。 要注意的是信號(hào)走線盡量不要跨過(guò)有分割的地方(moat), 還有不要

2016-09-12 14:53:53

間延遲(timing delay)。8、如何處理實(shí)際布線中的一些理論沖突的問(wèn)題基本上, 將模/數(shù)地分割隔離是對(duì)的。 要注意的是信號(hào)走線盡量不要跨過(guò)有分割的地方(moat), 還有不要讓電源和信號(hào)的回流

2021-09-19 14:47:06

布線中的一些理論沖突的問(wèn)題1. 基本上, 將模/數(shù)地分割隔離是對(duì)的。要注意的是信號(hào)走線盡量不要跨過(guò)有分割的地方(moat), 還有不要讓電源和信號(hào)的回流電流路徑(returning current

2011-03-17 10:05:21

a、如何處理實(shí)際布線中的一些理論沖突的問(wèn)題 1. 基本上, 將模/數(shù)地分割隔離是對(duì)的。 要注意的是信號(hào)走線盡量不要跨過(guò)有分割的地方(moat), 還有不要讓電源和信號(hào)的回流電流路徑

2012-12-17 12:29:48

更新一下博客,最近有一些朋友問(wèn)我如何處理數(shù)組中數(shù)據(jù),順便發(fā)一下教程,代碼如下if(UartHandle->Instance == USART3)//stm32的串口

2022-02-21 07:09:59

遠(yuǎn)忽近, 差分阻抗就會(huì)不一致, 就會(huì)影響信號(hào)完整性(signal integrity)及時(shí)間延遲(timing delay)。 8、如何處理實(shí)際布線中的一些理論沖突的問(wèn)題 基本上, 將模/數(shù)地分割隔離

2018-09-12 20:53:55

忽遠(yuǎn)忽近, 差分阻抗就會(huì)不一致, 就會(huì)影響信號(hào)完整性(signal integrity)及時(shí)間延遲(timing delay)8、如何處理實(shí)際布線中的一些理論沖突的問(wèn)題1. 基本上, 將模/數(shù)地分割

2018-08-10 21:07:43

怎樣去處理PCB板中的電源、地線?布線中網(wǎng)絡(luò)系統(tǒng)的作用是什么?

2021-04-25 09:07:37

(signal integrity)及時(shí)間延遲(timing delay)。 8、如何處理實(shí)際布線中的一些理論沖突的問(wèn)題 基本上, 將模/數(shù)地分割隔離是對(duì)的。 要注意的是信號(hào)走線盡量不要跨過(guò)有分割的地方

2019-09-06 18:54:23

1.如何處理實(shí)際布線中的一些理論沖突的問(wèn)題 問(wèn):在實(shí)際布線中,很多理論是相互沖突的;例如:1。處理多個(gè)模/數(shù)地的接法:理論上是應(yīng)該相互隔離的,但在實(shí)際的小型化、高密度布線中,由于空間的局限或者絕對(duì)

2014-11-06 16:22:00

如何處理實(shí)際布線中的一些理論沖突的問(wèn)題 基本上, 將模/數(shù)

2009-03-20 13:54:18

在我的設(shè)計(jì)

中,有

一些未使用的引腳。

一些是IO,

一些是僅輸入引腳。我將IO保持為開(kāi)放但我很困惑如

何處理僅輸入引腳。

一般的做法是將它們連接到GND,但我覺(jué)得連接到gnd時(shí)功耗更大。善意的建議我適當(dāng)?shù)拇鸢?/div>

2019-06-11 08:34:02

親愛(ài)的大家,我正在做一個(gè)關(guān)于一些bisic信號(hào)處理的項(xiàng)目。它描述如下,信號(hào)由PmodMic采樣,然后數(shù)字化信號(hào)被發(fā)送到我們定制的濾波器模塊,然后濾波后的信號(hào)被發(fā)送到ARM進(jìn)行進(jìn)一步處理,顯示等。我

2020-03-12 10:29:25

致, 就會(huì)影響信號(hào)完整性(signal integrity)及時(shí)間延遲(timing delay)。 8、如何處理實(shí)際布線中的一些理論沖突的問(wèn)題 基本上, 將模/數(shù)地分割隔離是對(duì)的。 要注意的是信號(hào)走

2018-09-19 16:21:03

頗為頭疼。下面是PCB布線的一些常用規(guī)則,無(wú)論你是小白還是已入行的工程師,都應(yīng)該掌握。 PCB布線常用規(guī)則 1、走線的方向控制規(guī)則 輸入和輸出端的導(dǎo)線應(yīng)盡量避免相鄰平行。在 PCB 布線時(shí),相鄰

2023-04-18 15:04:04

是保留地層的完整性。3、大面積導(dǎo)體中連接腿的處理在大面積的接地(電)中,常用元器件的腿與其連接,對(duì)連接腿的處理需要進(jìn)行綜合的考慮,就電氣性能而言,元件腿的焊盤與銅面滿接為好,但對(duì)元件的焊接裝配就存在一些

2018-05-07 08:20:06

致, 就會(huì)影響信號(hào)完整性(signal integrity)及時(shí)間延遲(timing delay)。8、如何處理實(shí)際布線中的一些理論沖突的問(wèn)題1. 基本上, 將模/數(shù)地分割隔離是對(duì)的。 要注意的是信號(hào)走線

2013-11-07 15:25:01

有的,他們有著很理性的知識(shí),同時(shí)又帶著一些自我創(chuàng)作的情感去布線,布出來(lái)的線就頗為美觀有藝術(shù)感。 下面是一些好的布線技巧和要領(lǐng): 首先,先對(duì)做個(gè)基礎(chǔ)介紹,PCB的層數(shù)可以分為單層,雙層和多層的,單層現(xiàn)在

2018-09-18 15:42:39

有的,他們有著很理性的知識(shí),同時(shí)又帶著一些自我創(chuàng)作的情感去布線,布出來(lái)的線就頗為美觀有藝術(shù)感。下面是一些好的布線技巧和要領(lǐng):首先,先對(duì)做個(gè)基礎(chǔ)介紹,PCB的層數(shù)可以分為單層,雙層和多層的,單層現(xiàn)在

2017-03-27 13:32:46

有的,他們有著很理性的知識(shí),同時(shí)又帶著一些自我創(chuàng)作的情感去布線,布出來(lái)的線就頗為美觀有藝術(shù)感。下面是一些好的布線技巧和要領(lǐng):首先,先對(duì)做個(gè)基礎(chǔ)介紹,PCB的層數(shù)可以分為單層,雙層和多層的,單層現(xiàn)在

2016-11-04 10:42:42

delay)。8、如何處理實(shí)際布線中的一些理論沖突的問(wèn)題基本上, 將模/數(shù)地分割隔離是對(duì)的。 要注意的是信號(hào)走線盡量不要跨過(guò)有分割的地方(moat), 還有不要讓電源和信號(hào)的回流電流路徑

2019-04-11 08:00:00

)及時(shí)間延遲(timingdelay)。 8、如何處理實(shí)際布線中的一些理論沖突的問(wèn)題 1. 基本上, 將模/數(shù)地分割隔離是對(duì)的。要注意的是信號(hào)走線盡量不要跨過(guò)有分割的地方(moat), 還有不要讓電源

2018-11-27 10:00:59

有沒(méi)有高手可以解決下這種問(wèn)題,規(guī)則設(shè)置器件,但是不知道怎么設(shè)置布線不布線不沖突,一布線就沖突了

2019-09-30 05:36:21

距會(huì)影響到差分阻抗的值, 此值是設(shè)計(jì)差分對(duì)的重要參數(shù)。需要平行也是因?yàn)橐3植罘肿杩沟?b class="flag-6" style="color: red">一致性。若兩線忽遠(yuǎn)忽近, 差分阻抗就會(huì)不一致, 就會(huì)影響信號(hào)完整性及時(shí)間延遲。8.如何處理實(shí)際布線中的一些理論沖突

2018-08-14 15:41:11

(signal integrity)及時(shí)間延遲(timing delay)。 8、如何處理實(shí)際布線中的一些理論沖突的問(wèn)題? 基本上, 將模/數(shù)地分割隔離是對(duì)的。 要注意的是信號(hào)走線盡量不要跨過(guò)有分割的地方

2018-09-20 10:36:56

delay)。7、如何處理實(shí)際布線中的一些理論沖突的問(wèn)題(1)基本上, 將模/數(shù)地分割隔離是對(duì)的。要注意的是信號(hào)走線盡量不要跨分割,(2)晶振要有穩(wěn)定的振蕩信號(hào), 一定要將晶振和芯片盡可能靠近,間距

2019-11-16 07:00:00

, 差分阻抗就會(huì)不一致, 就會(huì)影響信號(hào)完整性(signal integrity)及時(shí)間延遲(timing delay)。 8、如何處理實(shí)際布線中的一些理論沖突的問(wèn)題 基本上, 將模/數(shù)地分割隔離

2018-09-19 16:13:19

integrity)及時(shí)間延遲(timing delay)。8、如何處理實(shí)際布線中的一些理論沖突的問(wèn)題晶振是模擬的正反饋振蕩電路, 要有穩(wěn)定的振蕩信號(hào), 必須滿足loop gain 與 phase

2017-09-13 22:09:15

)。 8、如何處理實(shí)際布線中的一些理論沖突的問(wèn)題? 基本上,將模/數(shù)地分割隔離是對(duì)的。要注意的是信號(hào)走線盡量不要跨過(guò)有分割的地方(moat),還有不要讓電源和信號(hào)的回流電流路徑(returning

2018-09-21 16:26:48

是因?yàn)檫@間距會(huì)影響到差分阻抗的值, 此值是設(shè)計(jì)差分對(duì)的重要參數(shù)。需要平行也是因?yàn)橐3植罘肿杩沟?b class="flag-6" style="color: red">一致性。若兩線忽遠(yuǎn)忽近, 差分阻抗就會(huì)不一致, 就會(huì)影響信號(hào)完整性及時(shí)間延遲。8.如何處理實(shí)際布線中的一些

2019-09-28 08:00:00

間延遲(timing delay)。8、如何處理實(shí)際布線中的一些理論沖突的問(wèn)題基本上, 將模/數(shù)地分割隔離是對(duì)的。 要注意的是信號(hào)走線盡量不要跨過(guò)有分割的地方(moat), 還有不要讓電源和信號(hào)的回流

2017-01-20 10:29:29

應(yīng)用距離幾何理論與解析方法,研究了一些單形體積之間的關(guān)系,建立了關(guān)于單形體積的一些新的不等式,作為其特例,獲得垂足單形體積的一個(gè)不等式和單形的其他一些不等式.

2008-11-20 11:55:52 14

14 針對(duì)D-S證據(jù)理論的沖突證據(jù)融合問(wèn)題進(jìn)行了研究,通過(guò)對(duì)證據(jù)進(jìn)行沖突檢驗(yàn)及修正彌補(bǔ)了D-S證據(jù)理論在處理沖突證據(jù)時(shí)的不足。采用了加性策略對(duì)事件進(jìn)行排序的方法,找出證據(jù)

2008-12-14 10:59:00 11

11 本文主要講述了實(shí)時(shí)多任務(wù)系統(tǒng)中的一些基本概念。

2009-04-22 16:17:36 15

15 1、如何處理實(shí)際布線中的一些理論沖突的問(wèn)題 問(wèn):在實(shí)際布線中

2006-04-16 21:59:29 477

477 處理原理圖的一些技巧

最近在畫一個(gè)原理圖,把一些比較好的經(jīng)驗(yàn)分享一下,比較普通的就不提了。1.把每個(gè)功能模塊分離開(kāi)來(lái),

2009-11-21 13:56:40 801

801 本內(nèi)容匯總了近30個(gè)PCB布線知識(shí)面試題是PCB工程師必備的知識(shí)點(diǎn)總結(jié),也是面試者需要的知識(shí)。如何處理實(shí)際布線中的一些理論沖突的問(wèn)題,在高速設(shè)計(jì)中,如何解決信號(hào)的完整性問(wèn)題

2011-11-24 10:00:51 0

0 cadence畫板中遇到的一些問(wèn)題,在這里分享給大家,多多指教

2016-02-25 16:01:37 0

0 的是研究人員與工程師們的存在和工作,我說(shuō)的是深度學(xué)習(xí)。 你也許會(huì)認(rèn)為我的聲明有些夸張,但深度學(xué)習(xí)的出現(xiàn)確實(shí)引出了我們必須解決的幾個(gè)關(guān)鍵問(wèn)題。在本文中,我希望揭露這一新興領(lǐng)域引發(fā)的沖突,這與圖像處理領(lǐng)域的研究者們

2017-10-09 10:56:48 0

0 高速信號(hào)布線的時(shí)候,需要用到傳輸線理論,布線過(guò)程中,有些方法和傳統(tǒng)的一般信號(hào)布線也有所不同,下面大致給出了一些高頻信號(hào)線的布線技巧。

2017-12-22 14:12:09 30945

30945 介于軟件AD繪制PCB時(shí),考慮到的一些繪制技巧

在剛剛啟動(dòng)Altium Designer的PCB畫圖時(shí),PCB編輯器區(qū)內(nèi)成百上千根同一顏色的飛線像蜘蛛網(wǎng)一樣,亂成一團(tuán)麻,看不清第一個(gè)布線網(wǎng)絡(luò)的飛線

2018-05-30 15:22:00 0

0 參數(shù)。需要平行也是因?yàn)橐3植罘肿杩沟?b class="flag-6" style="color: red">一致性。若兩線忽遠(yuǎn)忽近, 差分阻抗就會(huì)不一致, 就會(huì)影響信號(hào)完整性(signal integrity)及時(shí)間延遲(timing delay)。8、如何處理實(shí)際布線中

2018-09-20 18:18:30 987

987 保持差分阻抗的一致性。若兩線忽遠(yuǎn)忽近, 差分阻抗就會(huì)不一致, 就會(huì)影響信號(hào)完整性(signal integrity)及時(shí)間延遲(timing delay)。

8、如何處理實(shí)際布線中的一些理論沖突

2018-09-20 18:18:34 666

666 問(wèn):在實(shí)際布線中,很多理論是相互沖突的;例如: 1。處理多個(gè)模/數(shù)地的接法:理論上是應(yīng)該相互隔離的,但在實(shí)際的小型化、高密度布線中,由于空間的局限或者絕對(duì)的隔離會(huì)導(dǎo)致小信號(hào)模擬地走線過(guò)長(zhǎng),很難

2019-05-28 14:56:54 656

656 區(qū)塊鏈技術(shù)下的商業(yè)模式所呈現(xiàn)的現(xiàn)實(shí)情形與技術(shù)條件,對(duì)一些傳統(tǒng)經(jīng)濟(jì)學(xué)理論形成一定沖擊。

2019-07-11 11:52:57 769

769 在PCB設(shè)計(jì)中,布線是完成產(chǎn)品設(shè)計(jì)的重要步驟,PCB走線的好壞直接影響整個(gè)系統(tǒng)的性能,布線在高速PCB設(shè)計(jì)中是至關(guān)重要的。

2019-09-05 16:13:09 1273

1273 1、如何處理實(shí)際布線中的一些理論沖突的問(wèn)題

問(wèn):在實(shí)際布線中,很多理論是相互沖突的;例如: 1。處理多個(gè)模/數(shù)地的接法:理論上是應(yīng)該相互隔離的,但在實(shí)際的小型化、高密度布線中,由于空間的局限或者

2019-09-23 08:00:00 0

0 是至關(guān)重要的。下面將針對(duì)實(shí)際布線中可能遇到的一些情況,分析其合理性,并給出一些比較優(yōu)化的走線策略。主要從直角走線,差分走線,蛇形線等三個(gè)方面來(lái)闡述。

2020-10-14 10:43:00 6

6 公共廣播系統(tǒng)目前是一個(gè)各行各業(yè)都會(huì)有需求的系統(tǒng),酒店、商場(chǎng)、公園、景點(diǎn)等場(chǎng)所都會(huì)用到。現(xiàn)實(shí)使用中,我們會(huì)發(fā)現(xiàn)有的廣播系統(tǒng)是電聲悅耳、自然流暢,但是有一些則帶有些噪音、嘯叫。面對(duì)這種情況,我們?cè)撊?b class="flag-6" style="color: red">何處理呢?

2021-01-09 10:21:45 7687

7687 在生活中,你可能接觸過(guò)各種各樣的電子產(chǎn)品,那么你可能并不知道它的一些組成部分,比如它可能含有的開(kāi)關(guān)電源,那么接下來(lái)讓小編帶領(lǐng)大家一起學(xué)習(xí)開(kāi)關(guān)電源布局以及印制板布線的一些原則。

2021-03-17 19:12:04 27

27 PCB設(shè)計(jì)論壇中的 遵守/避免布線法則,使得PCB設(shè)計(jì)者在這些規(guī)則也許不適用的地方要么遵守,要么忽略他們。一些情況下,這未必造成電路板設(shè)

2021-11-01 10:33:52 3613

3613 物聯(lián)網(wǎng) (IoT) 極大地影響了從醫(yī)療保健到農(nóng)業(yè)的各個(gè)行業(yè)。它也在改變?nèi)藗冊(cè)诮ㄖさ厣献鍪碌姆绞健R韵率俏锫?lián)網(wǎng)在建筑中的一些實(shí)際應(yīng)用,它們應(yīng)該讓人們思考將技術(shù)引入工作流程的新方法。

2022-07-15 15:15:04 4007

4007 PPT主要介紹了大功率IGBT模塊應(yīng)用中的一些技術(shù),包括參數(shù)解讀、器件選型、驅(qū)動(dòng)技術(shù)、保護(hù)方法以及失效分析等。

2022-09-05 11:36:39 3146

3146 讀過(guò)上一篇文章“ARM NEON快速上手指南”之后,相信你已經(jīng)對(duì)ARM NEON編程有了基本的認(rèn)識(shí)。但在真正利用ARM NEON優(yōu)化程序性能時(shí),還有很多編程技巧和注意事項(xiàng)。本文將結(jié)合本人的一些開(kāi)發(fā)經(jīng)歷,介紹NEON編程中的一些常見(jiàn)優(yōu)化技巧,希望能對(duì)用戶在NEON實(shí)際開(kāi)發(fā)中有些借鑒意義。

2022-12-12 09:11:24 2903

2903 不過(guò),差分對(duì)布線可能沒(méi)那么容易,因?yàn)樗鼈儽仨氉裱囟ǖ囊?guī)則,這樣才能確保信號(hào)的性能。這些規(guī)則決定了一些細(xì)節(jié),如差分對(duì)的走線寬度和間距,以及許多其他方面,如導(dǎo)線如何在電路板上一起布線。

2022-12-30 14:09:12 7440

7440 在過(guò)去幾年從事多個(gè)計(jì)算機(jī)視覺(jué)和深度學(xué)習(xí)項(xiàng)目之后,我在這個(gè)博客中收集了關(guān)于如何處理圖像數(shù)據(jù)的想法。對(duì)數(shù)據(jù)進(jìn)行預(yù)處理基本上要比直接將其輸入深度學(xué)習(xí)模型更好。有時(shí),甚至可能不需要深度學(xué)習(xí)模型,經(jīng)過(guò)一些處理后一個(gè)簡(jiǎn)單的分類器可能就足夠了。

2023-04-26 11:57:12 1208

1208

在實(shí)際項(xiàng)目開(kāi)發(fā)中,除了程序代碼外,還需要一些靜態(tài)資源,比如公司logo,背景圖,css樣式文件,js文件等等

2023-06-02 11:02:29 1644

1644

本文介紹了一些基本的電容檢測(cè)電路配置,并討論了如何處理低頻和高頻噪聲。讓我們看一下這個(gè)簡(jiǎn)短的視頻,并首先回顧一些關(guān)于電容式傳感器的基本知識(shí)。

2023-06-30 09:25:45 2726

2726

本文將探討在相同的ESA中,在何處以及如何使用TTD和PS分層方法可以幫助消除一些相控陣設(shè)計(jì)挑戰(zhàn)。

2023-07-10 15:03:57 1604

1604

。但是有時(shí)候,輸入端中的某些端口不需要使用,那么應(yīng)該如何處理呢? 首先,我們需要了解 TTL 芯片和非門芯片的內(nèi)部結(jié)構(gòu)和工作原理。TTL 芯片是由一些晶體管和電阻器組成的。它的輸入端接收高電平(1)或低電平(0)的電信號(hào),而輸出端會(huì)產(chǎn)生一個(gè)高電平或低電平的電信號(hào)。非門芯片只有一個(gè)輸

2023-09-17 15:42:15 8030

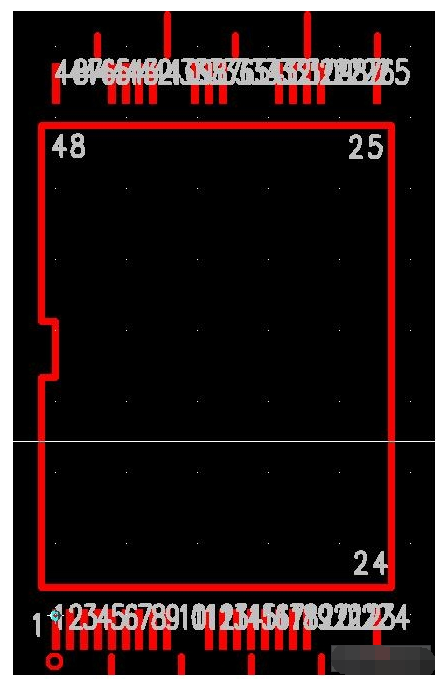

8030 由于一些板,尤其是U盤等面積很小的板,F(xiàn)LASH中只使用了為數(shù)不多的幾個(gè)PIN,為了可以讓其它PIN下面可以走線,增加GND網(wǎng)絡(luò)的面積,所以實(shí)際操作中要隱藏一些PIN。這就需要怎么操作呢!

2023-11-02 15:19:08 605

605

公共廣播系統(tǒng)目前是一個(gè)各行各業(yè)都會(huì)有需求的系統(tǒng),酒店、商場(chǎng)、公園、景點(diǎn)等場(chǎng)所都會(huì)用到。現(xiàn)實(shí)使用中,我們會(huì)發(fā)現(xiàn)有的廣播系統(tǒng)是電聲悅耳、自然流暢,但是有一些則帶有些噪音、嘯叫。面對(duì)這種情況,我們?cè)撊?b class="flag-6" style="color: red">何處理呢。

2023-11-08 09:41:21 3400

3400

在布局、布線中如何處理才能保證50M以上信號(hào)的穩(wěn)定性? 布局和布線是確保電子設(shè)備的信號(hào)穩(wěn)定性的關(guān)鍵步驟。在保證50M以上信號(hào)穩(wěn)定性的前提下,以下是一些布局和布線的最佳實(shí)踐,能夠幫助你處理電子設(shè)備

2023-11-24 14:51:05 1225

1225 在SMT貼片加工廠家的SMT貼片表面貼裝流程中,最重要的一個(gè)環(huán)節(jié)就是表面貼片封裝技術(shù)的過(guò)程,而在這個(gè)過(guò)程中,有時(shí)會(huì)在貼片加工的生產(chǎn)中遇到一些加工缺陷,比如錫膏缺陷,那么如何處理這些SMT貼片加工中

2024-03-22 17:30:34 1048

1048

在SMT貼片加工中,會(huì)出現(xiàn)一些加工缺陷和不良,錫膏缺陷就是其中之一,但可以通過(guò)一些方法來(lái)避免,那么我們應(yīng)該怎么做呢?以下是深圳佳金源錫膏廠家的簡(jiǎn)要描述:一、SMT錫膏中如何處理錫膏缺陷:SMT

2024-09-03 16:03:00 804

804

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論