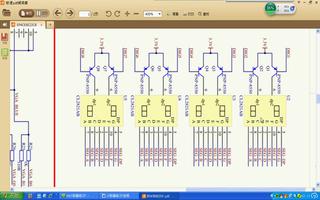

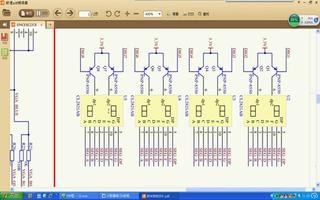

原文鏈接:熬夜到了1點(diǎn)了,終于寫出了1602的時(shí)鐘計(jì)數(shù)器代碼。為什么是時(shí)鐘計(jì)數(shù)器呢?因?yàn)槲疫€沒來得及做校準(zhǔn)時(shí)間,所以只能稱之為時(shí)鐘計(jì)數(shù)器,不能成為電子鐘。網(wǎng)上很少用人公開這一類代碼,一搜FPGA? 1602,都是寫一個(gè)靜態(tài)的顯示,在實(shí)際應(yīng)用中,是沒有用的,因此這個(gè)簡單的例子,給大家拋磚引玉了!上代碼: Qii 9.0編譯過,21EDA 開發(fā)板測試OKmodule LCD??(??rst,??key1,??clk,??rw,??rs,??en,??data?);?input clk,rst,key1;?output rs,en,rw;?output [7:0] data;??reg rs,en_sel;?reg [7:0] data;?reg [7:0] shi,fen,miao;?reg [31:0]count,count1;??//LCD CLK 分頻計(jì)數(shù)器?reg lcd_clk;?reg [7:0] one_1,one_2,one_3,one_4,one_5,one_6,one_7,one_8,one_9,one_10,one_11,one_12,one_13,one_14,one_15,one_16;?reg [7:0] two_1,two_2,two_3,two_4,two_5,two_6,two_7,two_8,two_9,two_10,two_11,two_12,two_13,two_14,two_15,two_16;?reg [7:0] next,xianshi,two;?parameter?state0 ?=8'h00,???? //設(shè)置8位格式,2行,5*7? ??8'h38;?????state1 ?=8'h01,??//整體顯示,關(guān)光標(biāo),不閃爍 ?8'h0C??? 閃爍 8'h0e????state2 ?=8'h02,??//設(shè)定輸入方式,增量不移位?8'h06????state3 ?=8'h03,??//清除顯示?????8'h01????state4 ?=8'h04,??//顯示第一行的指令??80H????state5 ?=8'h05,??//顯示第二行的指令??80H+40H????????scan?=8'h06,??????nul??=8'h07;???parameter?data0 ?=8'h10,?? //2行,共32個(gè)數(shù)據(jù)????data1 ?=8'h11,????data2 ?=8'h12,????data3 ?=8'h13,????data4 ?=8'h14,????data5 ?=8'h15,????data6 ?=8'h16,????data7 ?=8'h17,????data8 ?=8'h18,????data9 ?=8'h19,????data10 ?=8'h20,????data11 ?=8'h21,????data12 ?=8'h22,????data13 ?=8'h23,????data14 ?=8'h24,????data15 ?=8'h25,????data16 ?=8'h26,????data17?=8'h27,????data18?=8'h28,????data19?=8'h29,????data20?=8'h30,????data21 ?=8'h31,????data22 ?=8'h32,????data23 ?=8'h33,????data24 ?=8'h34,????data25 ?=8'h35,????data26 ?=8'h36,????data27 ?=8'h37,????data28 ?=8'h38,????data29 ?=8'h39,????data30 ?=8'h40,????data31 ?=8'h41;?initial?????????? //初始值?begin???//第一行顯示?TEL:13868160569???one_1<="T"; one_2<="E"; one_3<="L"; one_4<=":"; one_5<="1"; one_6<="3"; one_7<="8"; one_8<="6";????one_9<="8";one_10<="1";one_11<="6";one_12<="0";one_13<="5";one_14<="6";one_15<="9";one_16<=" ";???//第二行顯示 Clock:00-00-00???two_1<="C"; two_2<="l"; two_3<="o"; two_4<="c"; two_5<="k"; two_6<=":"; two_7<=" "; two_8<=" ";????two_9<="-";two_10<=" ";two_11<=" ";two_12<="-";two_13<=" ";two_14<=" ";two_15<=" ";two_16<=" ";???????shi<=0;fen<=0;miao<=0;?end?????always @(posedge clk )???//獲得LCD時(shí)鐘?begin??count<=count+1;??if(count==250000)??begin???count<=0;???lcd_clk<=~lcd_clk;??end?end?always @(posedge clk or negedge rst?)???//時(shí)鐘計(jì)數(shù)器?begin??if(!rst)??begin???shi<=0;fen<=0;miao<=0;???count1<=0;??end??else??begin???en_sel<=1;??????two_7<=?(shi/10)+8'b00110000;???two_8<=?(shi%10)+8'b00110000;???two_10<=(fen/10)+8'b00110000;???two_11<=(fen%10)+8'b00110000;???two_13<=(miao/10)+8'b00110000;???two_14<=(miao%10)+8'b00110000;??????count1<=count1+1'b1;???if(count1==49999999)??? // 時(shí)鐘計(jì)數(shù)???begin????count1<=0;????miao<=miao+1;????if(miao==59)????begin?????miao<=0;?????fen<=fen+1;?????if(fen==59)?????begin??????fen<=0;??????shi<=shi+1;??????if(shi==23)??????begin???????shi<=0;??????end?????end????end???end??end????end??always @(posedge lcd_clk? )?begin???case(next)????state0 :?????begin rs<=0; data<=8'h38; next<=state1; end?????? //配置液晶????state1 :?????begin rs<=0; data<=8'h0e; next<=state2; end????state2 :?????begin rs<=0; data<=8'h06; next<=state3; end????state3 :?????begin rs<=0; data<=8'h01; next<=state4; end??????????????state4 :?????begin rs<=0; data<=8'h80; next<=data0; end?//顯示第一行????data0 :?????begin rs<=1; data<=one_1; next<=data1 ; end????data1 :?????begin rs<=1; data<=one_2; next<=data2 ; end????data2 :?????begin rs<=1; data<=one_3; next<=data3 ; end????data3 :?????begin rs<=1; data<=one_4; next<=data4 ; end????data4 :?????begin rs<=1; data<=one_5; next<=data5 ; end????data5 :?????begin rs<=1; data<=one_6; next<=data6 ; end????data6 :?????begin rs<=1; data<=one_7; next<=data7 ; end????data7 :?????begin rs<=1; data<=one_8; next<=data8 ; end????data8 :?????begin rs<=1; data<=one_9; next<=data9 ; end????data9 :?????begin rs<=1; data<=one_10; next<=data10 ; end????data10 :?????begin rs<=1; data<=one_11; next<=data11 ; end????data11 :?????begin rs<=1; data<=one_12; next<=data12 ; end????data12 :?????begin rs<=1; data<=one_13; next<=data13 ; end????data13 :?????begin rs<=1; data<=one_14; next<=data14 ; end????data14 :?????begin rs<=1; data<=one_15; next<=data15 ; end????data15 :?????begin rs<=1; data<=one_16; next<=state5 ; end??????????state5:????????begin rs<=0;data<=8'hC0; next<=data16; end //顯示第二行????data16 :?????begin rs<=1; data<=two_1; next<=data17 ; end????data17 :?????begin rs<=1; data<=two_2; next<=data18 ; end????data18 :?????begin rs<=1; data<=two_3; next<=data19 ; end????data19 :?????begin rs<=1; data<=two_4; next<=data20 ; end????data20 :?????begin rs<=1; data<=two_5; next<=data21 ; end????data21 :?????begin rs<=1; data<=two_6; next<=data22 ; end????data22 :?????begin rs<=1; data<=two_7; next<=data23 ; end????data23 :?????begin rs<=1; data<=two_8; next<=data24 ; end????data24 :?????begin rs<=1; data<=two_9; next<=data25 ; end????data25 :?????begin rs<=1; data<=two_10; next<=data26 ; end????data26 :?????begin rs<=1; data<=two_11; next<=data27 ; end????data27 :?????begin rs<=1; data<=two_12; next<=data28 ; end????data28 :?????begin rs<=1; data<=two_13; next<=data29 ; end????data29 :?????begin rs<=1; data<=two_14; next<=data30 ; end????data30 :?????begin rs<=1; data<=two_15; next<=data31 ; end????data31 :?????begin rs<=1; data<=two_16; next<=scan ; end?????????scan?:???//交替更新第一行和第二行數(shù)據(jù)??????????begin??????next<=state4;?????end????default:?? next<=state0;????endcase?end?assign en=lcd_clk && en_sel;?assign rw=0;endmodule

FPGA verilog實(shí)現(xiàn)的1602時(shí)鐘計(jì)數(shù)器

- FPGA(632043)

- 1602時(shí)鐘計(jì)數(shù)器(796)

相關(guān)推薦

熱點(diǎn)推薦

計(jì)數(shù)器應(yīng)用實(shí)例

計(jì)數(shù)器應(yīng)用實(shí)例

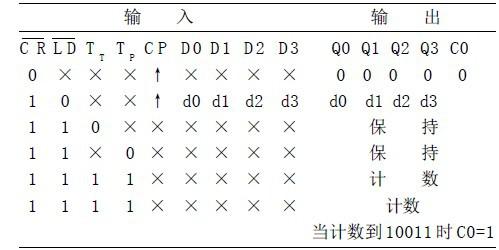

除了計(jì)數(shù)功能外,計(jì)數(shù)器產(chǎn)品還有一些附加功能,如異步復(fù)位、預(yù)置數(shù)(注意,有同步預(yù)置數(shù)和異步預(yù)置數(shù)兩種。前者受時(shí)鐘脈沖控制,后者不受時(shí)鐘

2010-05-27 09:37:55 6778

6778

6778

6778

基于FPGA和單片機(jī)的多功能計(jì)數(shù)器設(shè)計(jì)

本文設(shè)計(jì)了一種以超低功耗單片機(jī)MSP430F149為控制器,以高速的FPGA(現(xiàn)場可編程門陣列)實(shí)現(xiàn)等精度測量正弦信號的頻率、周期和相位差的多功能計(jì)數(shù)器。在設(shè)計(jì)中依據(jù)等精度計(jì)數(shù)原理,應(yīng)

2012-07-16 16:02:09 5979

5979

5979

5979

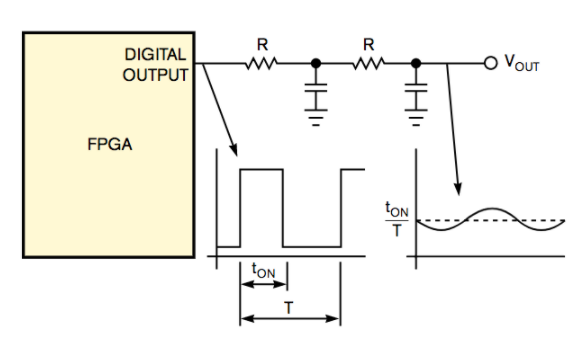

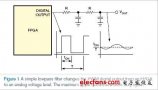

如何通過交換位提高FPGA-PWM計(jì)數(shù)器性能

?)。 圖1?一個(gè)簡單的低通濾波器將FPGA的PWM數(shù)字輸出更改為模擬電壓電平。最大紋波出現(xiàn)在占空比為50%的情況下。 假設(shè)Enable為高電平,則計(jì)數(shù)器在每個(gè)時(shí)鐘周期遞增計(jì)數(shù),PWM輸出的頻率為時(shí)鐘頻率除以2個(gè)計(jì)數(shù)位。您可以使用啟用將其連接到預(yù)分頻器來降低輸

2021-05-13 16:22:44 5315

5315

5315

5315

計(jì)數(shù)器電路設(shè)計(jì)中分頻電路的作用解析

假設(shè)時(shí)鐘分頻是N,則設(shè)置一個(gè)計(jì)數(shù)器,計(jì)數(shù)長度是N(即從0計(jì)數(shù)到N-1),然后在計(jì)數(shù)器為計(jì)數(shù)到(N-1)/2的時(shí)候,翻轉(zhuǎn)一下分頻時(shí)鐘信號。

2020-11-06 13:59:47 11462

11462

11462

11462

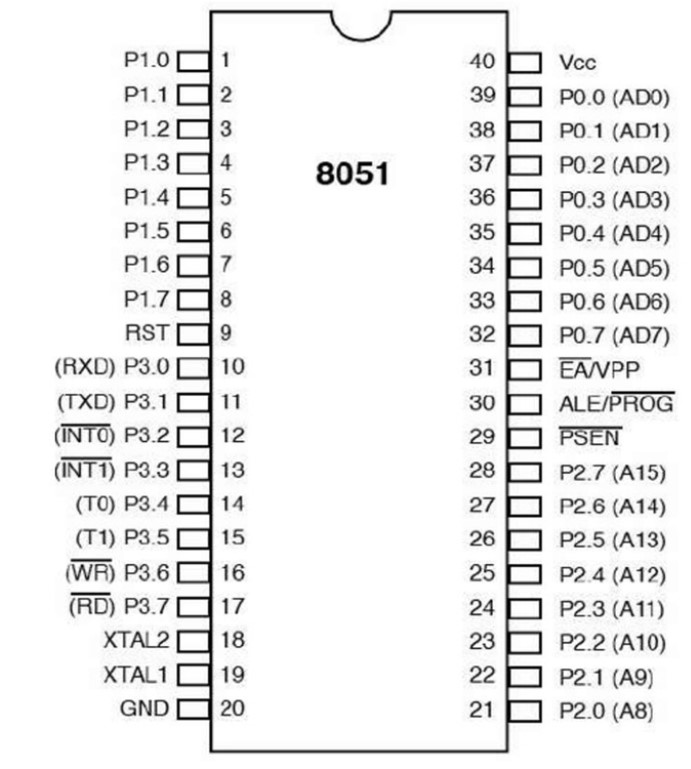

8051單片機(jī)的定時(shí)器/計(jì)數(shù)器

定時(shí)器/計(jì)數(shù)器是一種計(jì)數(shù)裝置,若對內(nèi)部時(shí)鐘脈沖計(jì)數(shù),可視為定時(shí)器;若對外部時(shí)鐘脈沖計(jì)數(shù),可視為計(jì)數(shù)器。

2022-11-22 17:15:09 8109

8109

8109

8109

如何利用Verilog HDL在FPGA上實(shí)現(xiàn)SRAM的讀寫測試

本篇將詳細(xì)介紹如何利用Verilog HDL在FPGA上實(shí)現(xiàn)SRAM的讀寫測試。SRAM是一種非易失性存儲(chǔ)器,具有高速讀取和寫入的特點(diǎn)。在FPGA中實(shí)現(xiàn)SRAM讀寫測試,包括設(shè)計(jì)SRAM接口模塊

2025-10-22 17:21:38 4118

4118

4118

4118

FPGA verilog語言學(xué)習(xí) 加法器

我是剛開始學(xué)FPGA,現(xiàn)在對其verilog語言還不是很懂。下面題目:設(shè)計(jì)一個(gè)十進(jìn)制的加法計(jì)數(shù)器,功能包含復(fù)位信號,置位信號,每個(gè)時(shí)鐘的正跳變沿計(jì)數(shù)器加一。計(jì)數(shù)0-99即可。請幫忙給個(gè)參考的程序。

2012-05-11 23:03:24

FPGA提高篇——禁止使用分頻時(shí)鐘、計(jì)數(shù)器時(shí)鐘

,分享給大家吧。——高手應(yīng)該是這樣做時(shí)鐘信號的。禁止用計(jì)數(shù)器分頻后的信號做其它模塊的時(shí)鐘,而要用改成時(shí)鐘使能的方式。否則這種時(shí)鐘滿天飛的方式對設(shè)計(jì)的可靠性極為不利,也大大增加了靜態(tài)時(shí)序分析的復(fù)雜性。時(shí)鐘

2018-08-08 11:13:26

Verilog 電子時(shí)鐘實(shí)現(xiàn)

在Verilog中實(shí)現(xiàn)一個(gè)簡單的電子時(shí)鐘,你可以使用一個(gè)計(jì)數(shù)器來周期性地遞增一個(gè)計(jì)數(shù)值,然后根據(jù)這個(gè)計(jì)數(shù)值來顯示時(shí)鐘的不同時(shí)刻。以下是一個(gè)簡單的例子:

module clock_display

2024-03-26 07:48:53

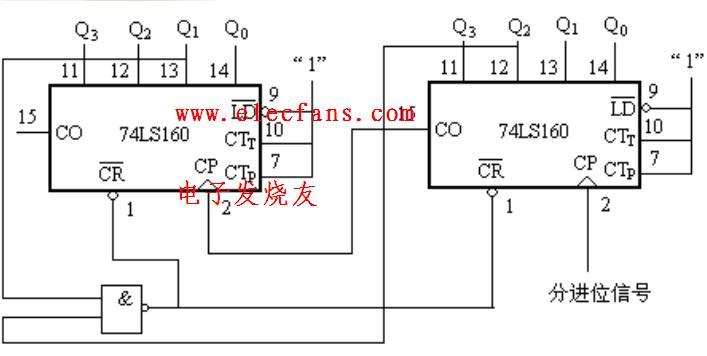

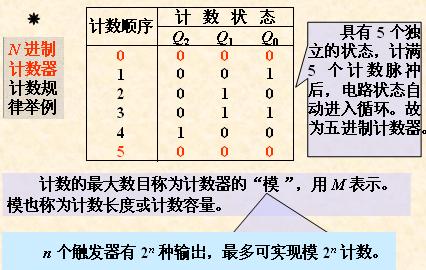

N進(jìn)制計(jì)數(shù)器的實(shí)現(xiàn)

N進(jìn)制計(jì)數(shù)器的實(shí)現(xiàn) 一、用集成計(jì)數(shù)器可以實(shí)現(xiàn)任意進(jìn)制的計(jì)數(shù)器二、集成計(jì)數(shù)器控制功能的歸類三、集成計(jì)數(shù)器的級聯(lián)擴(kuò)展四、復(fù)位法組成任意進(jìn)制加法計(jì)數(shù)器五、置位法組成任意進(jìn)制加法計(jì)數(shù)器六

2008-07-05 13:41:26

【FPGA】UART的計(jì)數(shù)器模塊的實(shí)現(xiàn)方式

計(jì)數(shù)器模塊的功能是可控地在輸入時(shí)鐘驅(qū)動(dòng)下進(jìn)行計(jì)數(shù),當(dāng)?shù)竭_(dá)計(jì)數(shù)上閾時(shí)給 UART 內(nèi)核一個(gè)提示信號。在不同的工作狀態(tài)下,計(jì)數(shù)器模塊的輸入時(shí)鐘是不同的。UART 在數(shù)據(jù)發(fā)送之前需要進(jìn)行數(shù)據(jù)加載(即將串行

2018-10-23 10:02:16

【verilog每日一練】計(jì)數(shù)器計(jì)時(shí)

已知外部輸入時(shí)鐘信號clk為50MHz,請用verilog實(shí)現(xiàn)計(jì)數(shù)器的計(jì)時(shí)1秒鐘,每間隔1秒輸出一個(gè)clk時(shí)鐘周期的脈沖信號flag,參考波形如下:

2023-08-17 09:13:59

【連載視頻教程(五)】小梅哥FPGA設(shè)計(jì)思想與驗(yàn)證方法視頻教程之BCD碼計(jì)數(shù)器設(shè)計(jì)驗(yàn)證

講解數(shù)字系統(tǒng),尤其是時(shí)鐘系統(tǒng)中非常常見的一個(gè)模塊——BCD碼計(jì)數(shù)器的設(shè)計(jì)實(shí)現(xiàn)與驗(yàn)證,講解Verilog基礎(chǔ)語法,了解BCD碼技術(shù)器與普通二進(jìn)制計(jì)數(shù)器的區(qū)別。BCD碼計(jì)數(shù)器經(jīng)常用在需要十進(jìn)制計(jì)數(shù),十進(jìn)制

2015-09-23 12:39:23

關(guān)于FPGA在仿真軟件中計(jì)數(shù)器提前計(jì)數(shù)的問題

FPGA的人來說,非常之實(shí)用。但是,部分工程師在做仿真時(shí),有時(shí)候會(huì)出現(xiàn)違反這一原則的奇怪現(xiàn)象。例如下面這個(gè)案例。關(guān)于在仿真軟件中,為什么計(jì)數(shù)器的判定會(huì)在不滿足加一條件的時(shí)候進(jìn)行加一操作(如下圖所示

2020-04-24 14:54:53

關(guān)于計(jì)數(shù)器的疑問

最近在看《現(xiàn)代操作系統(tǒng)》,他提到了時(shí)鐘維持實(shí)際時(shí)間,在每個(gè)時(shí)鐘滴答將計(jì)數(shù)器加1即可實(shí)現(xiàn)。但要注意位溢出(32位計(jì)數(shù)器),可以通過以下方法解決:使用64位計(jì)數(shù)器:缺點(diǎn)是這種方法使得計(jì)數(shù)器加一操作的代價(jià)很高,1s內(nèi)維護(hù)很多次計(jì)數(shù)器。我不太懂紅色字體的意思

2018-05-04 11:36:41

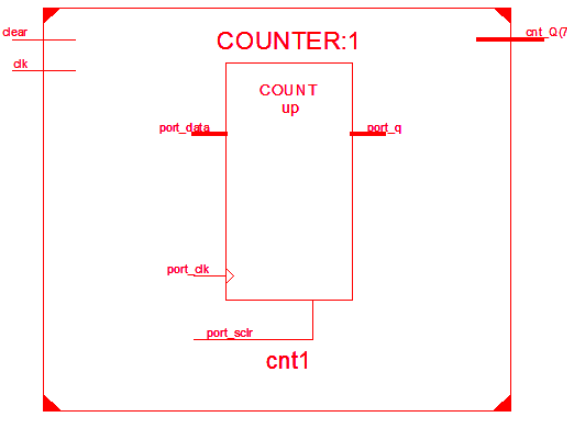

在FPGA中設(shè)計(jì)實(shí)現(xiàn)24進(jìn)制加法計(jì)數(shù)器的設(shè)計(jì)

1、實(shí)現(xiàn)一個(gè)24進(jìn)制加法計(jì)數(shù)器的設(shè)計(jì)本實(shí)驗(yàn)設(shè)計(jì)實(shí)現(xiàn)一個(gè)24進(jìn)制的加法計(jì)數(shù)器,它由晶體振蕩器、分頻器、計(jì)數(shù)器和數(shù)碼管顯示器組成,圖6.1是該加法計(jì)數(shù)器的示意圖。晶體振蕩器產(chǎn)生穩(wěn)定的50MHz的脈沖信號

2022-07-05 15:14:27

在FPGA開發(fā)板上實(shí)現(xiàn)一個(gè)電子秒表的計(jì)數(shù)器模塊設(shè)計(jì)

1、設(shè)計(jì)一個(gè)電子秒表的計(jì)數(shù)器模塊在上一例中,使用了FPGA開發(fā)板上的撥碼開關(guān)控制四位數(shù)碼管進(jìn)行動(dòng)態(tài)顯示,在本例中,我們將數(shù)碼管作為一個(gè)整體IP,然后用一個(gè)計(jì)數(shù)器驅(qū)動(dòng)它實(shí)現(xiàn)一個(gè)電子秒表的功能。根據(jù)這一

2022-07-29 14:57:01

基于verilog的數(shù)字時(shí)鐘程序

基于verilog的數(shù)字時(shí)鐘程序,時(shí)鐘芯片基礎(chǔ)——60進(jìn)制計(jì)數(shù)器設(shè)計(jì)目的讓nexys 4板上的7段碼LED顯示時(shí)鐘信息,其中包括時(shí)鐘的小時(shí),分鐘,秒鐘部分,且能夠實(shí)現(xiàn)時(shí)鐘的停止計(jì)時(shí)信號,手動(dòng)調(diào)整小時(shí)

2021-07-22 07:37:01

如何利用MCS-51單片機(jī)實(shí)現(xiàn)定時(shí)器/計(jì)數(shù)器的時(shí)鐘設(shè)計(jì)?

如何利用MCS-51單片機(jī)實(shí)現(xiàn)定時(shí)器/計(jì)數(shù)器的時(shí)鐘設(shè)計(jì)?

2021-10-20 07:17:45

如何在FPGA中實(shí)現(xiàn)實(shí)時(shí)時(shí)鐘或時(shí)間和日期計(jì)數(shù)器

嗨,我是Xilinx FPGA的新手。我該如何在FPGA中實(shí)現(xiàn)實(shí)時(shí)時(shí)鐘或時(shí)間和日期計(jì)數(shù)器?Xilinx是否為Artix 7提供任何RTC核心或IP?非常感謝您的建議。

2020-05-22 12:41:35

小程序大道理---計(jì)數(shù)器與行波時(shí)鐘(轉(zhuǎn))

之前寫過一篇關(guān)于 “加法器” 的博文,研究了加法器的底層電路,本來想要研究一下“行波時(shí)鐘”,由于涉及到計(jì)數(shù)器,那么就先看看 “計(jì)數(shù)器” 在FPGA中綜合后是什么樣的 ?然后再看“行波時(shí)鐘”的情況

2014-03-24 17:27:51

怎么實(shí)現(xiàn)兩個(gè)32位計(jì)數(shù)器計(jì)數(shù)速率高達(dá)3GHz

中實(shí)現(xiàn)每個(gè)計(jì)數(shù)器的剩余28位。然后將外部4位引入FPGA,并且兩個(gè)32位計(jì)數(shù)器將由加法器求和,然后主機(jī)處理器可以讀取結(jié)果。雖然外部4位仍然會(huì)在FPGA的頻率過高時(shí)切換,但在對計(jì)數(shù)器求和之前,時(shí)鐘將停止

2019-04-19 13:34:34

怎么實(shí)現(xiàn)基于單片機(jī)和FPGA的多功能計(jì)數(shù)器的設(shè)計(jì)?

怎么實(shí)現(xiàn)基于單片機(jī)和FPGA的多功能計(jì)數(shù)器的設(shè)計(jì)?

2021-05-14 06:57:15

怎樣采用外部時(shí)鐘計(jì)數(shù)器的方式來實(shí)現(xiàn)捕獲信號的頻率呢

怎樣采用外部時(shí)鐘計(jì)數(shù)器的方式來實(shí)現(xiàn)捕獲信號的頻率呢?其實(shí)現(xiàn)步驟是怎樣的?

2021-11-24 07:43:12

定時(shí)器/計(jì)數(shù)器基礎(chǔ)

15-1.實(shí)現(xiàn)定時(shí)的方法15-2.定時(shí)器/計(jì)數(shù)器的結(jié)構(gòu)和工作原理 15-3.定時(shí)器/計(jì)數(shù)器的控制15-4.定時(shí)器/計(jì)數(shù)器的工作方式 15-5.定時(shí)器/計(jì)數(shù)器應(yīng)用 軟件定時(shí)軟件延時(shí)不占用硬

2009-03-23 12:17:51 48

48

48

481602液晶的6位計(jì)數(shù)器程序

;******************************;1602液晶6位計(jì)數(shù)器:本程序調(diào)試通過 *;************************************;* 硬件:此程序

2010-04-21 22:44:19 57

57

57

57計(jì)數(shù)器的級連使用

計(jì)數(shù)器的級連使用

一個(gè)十進(jìn)制計(jì)數(shù)器只能顯示0~9十個(gè)數(shù),為了擴(kuò)大計(jì)數(shù)器范圍,常用多個(gè)十進(jìn)制計(jì)數(shù)器級連使用。

2007-11-22 12:53:25 4240

4240

4240

4240

60進(jìn)制計(jì)數(shù)器

60進(jìn)制計(jì)數(shù)器,由于24進(jìn)制、60進(jìn)制計(jì)數(shù)器均由集成計(jì)數(shù)器級聯(lián)構(gòu)成,且都包含有基本的

2008-06-30 00:00:41 16804

16804

16804

16804

24進(jìn)制計(jì)數(shù)器

計(jì)數(shù)器級聯(lián)時(shí)的時(shí)鐘構(gòu)成方式可以采用同步時(shí)鐘,也可以采用異

2008-06-30 00:03:32 11945

11945

11945

11945

100進(jìn)制計(jì)數(shù)器

100進(jìn)制計(jì)數(shù)器

異步級聯(lián)法組成的100進(jìn)制計(jì)數(shù)器

定義集成計(jì)數(shù)器的高低位,1#芯片為低位(相當(dāng)

2008-07-05 14:25:17 7066

7066

7066

7066

計(jì)數(shù)器測試

實(shí)驗(yàn) 計(jì)數(shù)器測試

一、 實(shí)驗(yàn)?zāi)康?、 學(xué)習(xí)8031內(nèi)部定時(shí)∕計(jì)數(shù)器的使用方法。2、 學(xué)習(xí)計(jì)數(shù)器各種工作方

2009-05-16 02:08:09 1998

1998

1998

1998計(jì)數(shù)器

計(jì)數(shù)器

計(jì)數(shù)器的作用與分類

計(jì)數(shù)器(Counter)用于計(jì)算輸入脈沖個(gè)數(shù),還常用于分頻、定時(shí)等。

2009-09-30 18:30:15 1919

1919

1919

1919

環(huán)形計(jì)數(shù)器和扭環(huán)形計(jì)數(shù)器

環(huán)形計(jì)數(shù)器和扭環(huán)形計(jì)數(shù)器

移位寄存器也可以構(gòu)成計(jì)數(shù)器,稱為移位型計(jì)數(shù)器。它有兩種結(jié)構(gòu):環(huán)形計(jì)數(shù)器和扭環(huán)形計(jì)數(shù)器。

2010-01-12 14:07:46 10310

10310

10310

10310什么是二進(jìn)制計(jì)數(shù)器,二進(jìn)制計(jì)數(shù)器原理是什么?

什么是二進(jìn)制計(jì)數(shù)器,二進(jìn)制計(jì)數(shù)器原理是什么?

計(jì)數(shù)器是數(shù)字系統(tǒng)中用得較多的基本邏輯器件。它不僅能記錄輸入時(shí)鐘脈沖的個(gè)數(shù),還可以實(shí)現(xiàn)

2010-03-08 13:16:34 31861

31861

31861

31861計(jì)數(shù)器,計(jì)數(shù)器的工作原理是什么?

計(jì)數(shù)器,計(jì)數(shù)器的工作原理是什么?

在數(shù)字系統(tǒng)中使用最多的時(shí)序電路是計(jì)數(shù)器。計(jì)數(shù)器不僅能用于對時(shí)鐘脈沖進(jìn)行計(jì)數(shù)還可以用于分頻、定時(shí),產(chǎn)生

2010-03-08 13:50:14 62401

62401

62401

62401計(jì)數(shù)器的定義和分類

計(jì)數(shù)器的定義和分類

計(jì)數(shù)器定義在數(shù)字電路中,計(jì)數(shù)器屬于時(shí)序電路,它主要由具有記憶功能的觸發(fā)器構(gòu)成。計(jì)數(shù)器不僅僅

2010-03-08 17:37:35 14836

14836

14836

14836C181 2-10進(jìn)制可預(yù)置可逆計(jì)數(shù)器的應(yīng)用線路圖

C181是雙時(shí)鐘2-10進(jìn)制可預(yù)置可逆計(jì)數(shù)器.所謂雙時(shí)鐘是指計(jì)數(shù)器的加法計(jì)數(shù)時(shí)鐘和減法計(jì)數(shù)時(shí)鐘各有它自身的輸入

2010-10-19 15:16:06 1021

1021

1021

1021

基于FPGA的PWM計(jì)數(shù)器改進(jìn)設(shè)計(jì)

簡單改變FPGA計(jì)數(shù)器規(guī)格使作為DAC功能PWM計(jì)數(shù)器的紋波降低。

2012-04-06 11:11:57 2240

2240

2240

2240

基于Multisim的計(jì)數(shù)器設(shè)計(jì)仿真

計(jì)數(shù)器是常用的時(shí)序邏輯電路器件,文中介紹了以四位同步二進(jìn)制集成計(jì)數(shù)器74LS161和異步二-五-十模值計(jì)數(shù)器74LS290為主要芯片,設(shè)計(jì)實(shí)現(xiàn)了任意模值計(jì)數(shù)器電路,并用Multisim軟件進(jìn)行了

2013-07-26 11:38:41 134

134

134

134計(jì)數(shù)器

計(jì)數(shù)器是用來累計(jì)和寄存輸入脈沖個(gè)數(shù)得時(shí)序邏輯部件,是數(shù)字系統(tǒng)中用途最廣泛的基本部件。計(jì)數(shù)器不僅能用于時(shí)鐘脈沖的計(jì)數(shù),還可以用于分頻,定時(shí),產(chǎn)生節(jié)拍脈沖及進(jìn)位數(shù)字運(yùn)算等,是數(shù)字系統(tǒng)、計(jì)算機(jī)系統(tǒng)必不可缺少的部件。

2016-05-05 17:40:59 0

0

0

0集成計(jì)數(shù)器實(shí)現(xiàn)N進(jìn)制計(jì)數(shù)

集成計(jì)數(shù)器實(shí)現(xiàn)N進(jìn)制計(jì)數(shù)集成計(jì)數(shù)器實(shí)現(xiàn)N進(jìn)制計(jì)數(shù)集成計(jì)數(shù)器實(shí)現(xiàn)N進(jìn)制計(jì)數(shù)

2016-06-08 14:28:43 0

0

0

0用Verilog實(shí)現(xiàn)基于FPGA的通用分頻器的設(shè)計(jì)

用 Verilog實(shí)現(xiàn)基于FPGA 的通用分頻器的設(shè)計(jì)時(shí)鐘分頻包括奇數(shù)和偶數(shù)分頻

2016-07-14 11:32:47 46

46

46

46基于Proteus的任意進(jìn)制計(jì)數(shù)器設(shè)計(jì)與仿真

提出一種基于Proteus 軟件的任意進(jìn)制計(jì)數(shù)器的設(shè)計(jì)。以74LS163 集成計(jì)數(shù)器為基礎(chǔ),用置數(shù)法設(shè)計(jì)了兩種48 進(jìn)制計(jì)數(shù)器,采用Proteus 軟件對計(jì)數(shù)器進(jìn)行仿真。結(jié)果表明,Proteus 軟件具有實(shí)現(xiàn)48 進(jìn)制計(jì)數(shù)器的功能。仿真圖像清晰,能快速準(zhǔn)確地驗(yàn)證設(shè)計(jì)結(jié)果。

2016-07-29 18:53:03 0

0

0

0計(jì)數(shù)器的控制及應(yīng)用

計(jì)數(shù)是一種最簡單基本的運(yùn)算,計(jì)數(shù)器就是實(shí)現(xiàn)這種運(yùn)算的邏輯電路,計(jì)數(shù)器在數(shù)字系統(tǒng)中主要是對脈沖的個(gè)數(shù)進(jìn)行計(jì)數(shù),以實(shí)現(xiàn)測量、計(jì)數(shù)和控制的功能,同時(shí)兼有分頻功能,計(jì)數(shù)器是由基本的計(jì)數(shù)單元和一些控制門所組成

2017-09-25 10:13:37 8

8

8

824進(jìn)制計(jì)數(shù)器的設(shè)計(jì)

集成計(jì)數(shù)器常見的是多位二進(jìn)制計(jì)數(shù)器及十進(jìn)制計(jì)數(shù)器,當(dāng)需要實(shí)現(xiàn)其它進(jìn)制計(jì)數(shù)器時(shí),通常利用現(xiàn)有的集成計(jì)數(shù)器進(jìn)行適當(dāng)?shù)倪B接而構(gòu)成。對于當(dāng)設(shè)計(jì)要求沒有限定計(jì)數(shù)器的狀態(tài)編碼時(shí)電路設(shè)計(jì)的靈活性問題已有文獻(xiàn)進(jìn)行

2017-11-09 16:36:16 81

81

81

81機(jī)械計(jì)數(shù)器結(jié)構(gòu)及原理圖

計(jì)數(shù)是一種最簡單基本的運(yùn)算,計(jì)數(shù)器就是實(shí)現(xiàn)這種運(yùn)算的邏輯電路,計(jì)數(shù)器在數(shù)字系統(tǒng)中主要是對脈沖的個(gè)數(shù)進(jìn)行計(jì)數(shù),以實(shí)現(xiàn)測量、計(jì)數(shù)和控制的功能,同時(shí)兼有分頻功能,計(jì)數(shù)器是由基本的計(jì)數(shù)單元和一些控制門所組成

2018-02-24 15:31:08 50912

50912

50912

50912一個(gè)連環(huán)無敵面試題--計(jì)數(shù)器

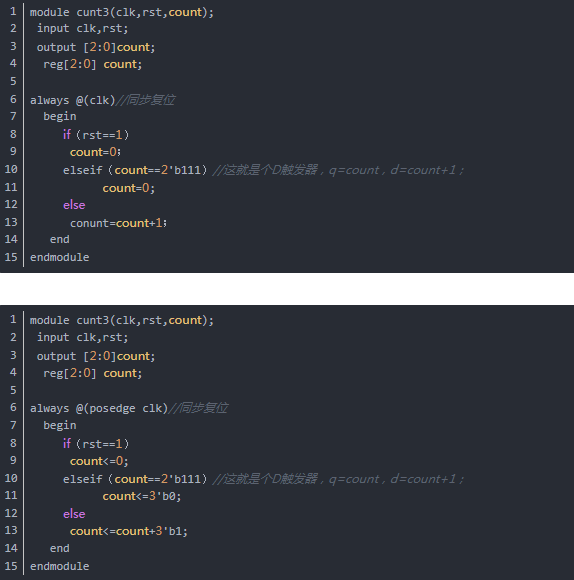

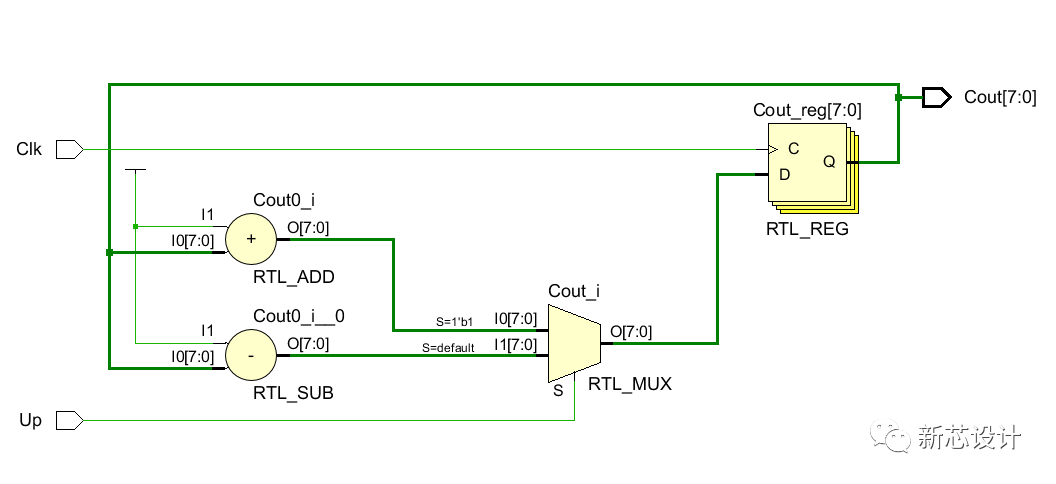

問題1:如何用Verilog實(shí)現(xiàn)這個(gè)計(jì)數(shù)器?針對上述功能的計(jì)數(shù)器,應(yīng)該如何用Verilog實(shí)現(xiàn)?

2018-05-16 15:16:13 6857

6857

6857

6857

采用FPGA DIYK開發(fā)板控制模為60的計(jì)數(shù)器數(shù)碼管動(dòng)態(tài)顯示

FPGA diy作業(yè)實(shí)現(xiàn)模為60的計(jì)數(shù)器數(shù)碼管動(dòng)態(tài)顯示。

2018-06-20 11:59:00 4802

4802

4802

4802采用中規(guī)模集成計(jì)數(shù)器進(jìn)行任意進(jìn)制計(jì)數(shù)器設(shè)計(jì)的解決方案

計(jì)數(shù)器是數(shù)字邏輯系統(tǒng)中的基本部件, 它是數(shù)字系統(tǒng)中用得最多的時(shí)序邏輯電路,其主要功能就是用計(jì)數(shù)器的不同狀態(tài)來記憶輸入脈沖的個(gè)數(shù)。除此以外還具有定時(shí)、分頻、運(yùn)算等邏輯功能。 計(jì)數(shù)器不僅能用于對時(shí)鐘脈沖的計(jì)數(shù), 還可使用于定時(shí)、分頻、產(chǎn)生節(jié)拍脈沖以及進(jìn)行數(shù)字運(yùn)算等。只要是稍微復(fù)雜一些的

2019-05-30 08:24:00 18218

18218

18218

18218

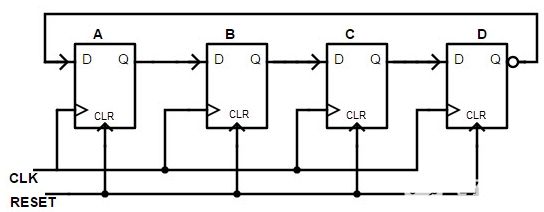

基于FPGA的同步復(fù)位的3位計(jì)數(shù)器設(shè)計(jì)

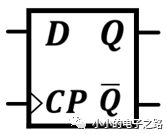

分析:首先,我們可以看到有哪些信號。復(fù)位rst 、計(jì)數(shù)器3位的、時(shí)鐘信號。(用到2路選擇器。復(fù)位和不復(fù)位)

其次,怎樣實(shí)現(xiàn),一個(gè)時(shí)鐘過來,記一次數(shù)就是加一次,保存(用到D觸發(fā)器),滿之后為0;

2019-02-01 07:08:00 2860

2860

2860

2860

計(jì)數(shù)器原理

計(jì)數(shù)是一種最簡單基本的運(yùn)算,計(jì)數(shù)器就是實(shí)現(xiàn)這種運(yùn)算的邏輯電路,計(jì)數(shù)器在數(shù)字系統(tǒng)中主要是對脈沖的個(gè)數(shù)進(jìn)行計(jì)數(shù),以實(shí)現(xiàn)測量、計(jì)數(shù)和控制的功能,同時(shí)兼有分頻功能,計(jì)數(shù)器是由基本的計(jì)數(shù)單元和一些控制門所組成

2019-01-24 14:35:40 66784

66784

66784

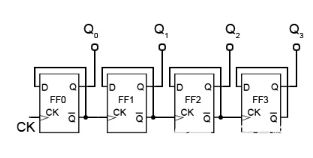

66784異步計(jì)數(shù)器真值表

異步計(jì)數(shù)器使用串聯(lián)連接在一起的觸發(fā)器,使輸入時(shí)鐘脈沖看起來通過計(jì)數(shù)器紋波。

2019-06-23 10:39:41 21588

21588

21588

21588

4位同步計(jì)數(shù)器

同步計(jì)數(shù)器之所以被稱為是因?yàn)?b class="flag-6" style="color: red">計(jì)數(shù)器內(nèi)所有單個(gè)觸發(fā)器的時(shí)鐘輸入都由同一時(shí)鐘信號同時(shí)同時(shí)計(jì)時(shí)。

2019-06-23 10:16:39 27682

27682

27682

27682

MOD計(jì)數(shù)器和時(shí)序圖

計(jì)數(shù)器的工作是通過每個(gè)時(shí)鐘脈沖將計(jì)數(shù)器的內(nèi)容提前一個(gè)計(jì)數(shù)來計(jì)數(shù)。當(dāng)被時(shí)鐘輸入激活時(shí)推進(jìn)其數(shù)字或狀態(tài)序列的計(jì)數(shù)器被稱為以“遞增計(jì)數(shù)”模式操作。同樣,當(dāng)被時(shí)鐘輸入激活時(shí)減少其數(shù)字或狀態(tài)序列的計(jì)數(shù)器被稱為以“倒計(jì)數(shù)”模式操作。在UP和DOWN模式下工作的計(jì)數(shù)器稱為雙向計(jì)數(shù)器。

2019-06-23 07:47:00 16636

16636

16636

16636

在寫Verilog時(shí)用到的簡單的計(jì)數(shù)器模塊和功能模塊的程序免費(fèi)下載

本文檔的主要內(nèi)容詳細(xì)介紹的是在寫Verilog時(shí)用到的簡單的計(jì)數(shù)器模塊和功能模塊的程序免費(fèi)下載。

2019-08-30 08:00:00 11

11

11

11使用單片機(jī)實(shí)現(xiàn)LCD1602脈沖計(jì)數(shù)器的程序和仿真電路圖免費(fèi)下載

本文檔的主要內(nèi)容詳細(xì)介紹的是使用單片機(jī)實(shí)現(xiàn)LCD1602脈沖計(jì)數(shù)器的程序和仿真電路圖免費(fèi)下載。

2020-10-09 08:00:00 13

13

13

13FPGA基礎(chǔ)應(yīng)用計(jì)數(shù)器的實(shí)例詳細(xì)說明

該計(jì)數(shù)器從0 計(jì)數(shù)到4294967295,然后回滾到0 并重新開始計(jì)數(shù)。它只需要FPGA 上一點(diǎn)點(diǎn)的資源就可以迅速完成計(jì)數(shù),這都多虧了FPGA 中隱藏的進(jìn)位鏈。讓我們來看這種計(jì)數(shù)器的幾種變體。

2020-12-11 17:26:55 12

12

12

12什么是計(jì)數(shù)器芯片?

什么是計(jì)數(shù)器芯片? 一般來說,計(jì)數(shù)器芯片就是用來實(shí)現(xiàn)計(jì)數(shù)這種最基礎(chǔ)運(yùn)算的邏輯電路,計(jì)數(shù)器在數(shù)字系統(tǒng)中主要是對脈沖的個(gè)數(shù)進(jìn)行計(jì)數(shù),以實(shí)現(xiàn)測量、計(jì)數(shù)和控制的功能,同時(shí)兼有分頻功能,計(jì)數(shù)器是由基本的計(jì)數(shù)

2021-07-13 14:09:37 15825

15825

15825

15825基于單片機(jī)定時(shí)器/計(jì)數(shù)器的時(shí)鐘設(shè)計(jì)及計(jì)數(shù)設(shè)計(jì)

基于單片機(jī)定時(shí)器/計(jì)數(shù)器的時(shí)鐘設(shè)計(jì)以及計(jì)數(shù)設(shè)計(jì)第一部分 前言第二部分 定時(shí)器/計(jì)數(shù)器的原理MCS-51定時(shí)器/計(jì)數(shù)器的結(jié)構(gòu)定時(shí)器/計(jì)數(shù)器相關(guān)特殊功能寄存器定時(shí)器/計(jì)數(shù)器工作方式第三部分 定時(shí)器

2021-11-05 09:06:00 51

51

51

5151單片機(jī)定時(shí)器/計(jì)數(shù)器

CPU的參與。3、51單片機(jī)中的 定時(shí)器/計(jì)數(shù)器 是根據(jù) 機(jī)器內(nèi)部的時(shí)鐘 或者是 外部的脈沖信號 對寄存器中的數(shù)據(jù)加1。4、有了 定時(shí)器/計(jì)數(shù)器 之后,可以增加單片機(jī)的效率,一些簡單的重復(fù)加1的工作可以交給 定時(shí)器/計(jì)數(shù)器 處理。并且定時(shí)器還可以實(shí)現(xiàn)精

2021-11-20 20:06:10 47

47

47

47(二):定時(shí)器和計(jì)數(shù)器的區(qū)別;時(shí)鐘和晶振的區(qū)別、RTC實(shí)時(shí)時(shí)鐘;MPU、MCU、SOC區(qū)別;電源符號:VCC、VDD、VSS、VEE、VPP、VBAT

硬件的區(qū)別定時(shí)器和計(jì)數(shù)器的區(qū)別時(shí)鐘和晶振的區(qū)別定時(shí)器和計(jì)數(shù)器的區(qū)別定時(shí)器實(shí)際上也是計(jì)數(shù)器,工作在計(jì)數(shù)方式下,只是計(jì)數(shù)的是固定周期的脈沖,由于脈沖周期固定,由計(jì)數(shù)值可以計(jì)算時(shí)間,有定時(shí)功能。定時(shí)和計(jì)數(shù)

2022-01-11 11:58:38 3

3

3

3Verilog實(shí)現(xiàn)計(jì)數(shù)器在某個(gè)區(qū)間內(nèi)循環(huán)計(jì)數(shù),遞增遞減

用Verilog語言,活用計(jì)數(shù)器功能。

2022-04-07 17:33:24 6335

6335

6335

6335

Johnson約翰遜計(jì)數(shù)器Verilog實(shí)現(xiàn)

扭環(huán)形計(jì)數(shù)器,約翰遜計(jì)數(shù)器,每次狀態(tài)變化時(shí)僅有一個(gè)觸發(fā)器發(fā)生翻轉(zhuǎn),譯碼不存在競爭冒險(xiǎn),在n(n≥3)位計(jì)數(shù)器中,使用2n個(gè)狀態(tài),有2^n-2n個(gè)狀態(tài)未使用;

2022-06-15 09:27:57 3575

3575

3575

3575異步計(jì)數(shù)器的主要類型

異步計(jì)數(shù)器是那些輸出不受時(shí)鐘信號影響的計(jì)數(shù)器。由于異步計(jì)數(shù)器中的觸發(fā)器提供有不同的時(shí)鐘信號,因此在產(chǎn)生輸出時(shí)可能會(huì)有延遲。設(shè)計(jì)異步計(jì)數(shù)器所需的邏輯門數(shù)量非常少,所以它們的設(shè)計(jì)很簡單。異步計(jì)數(shù)器的另一個(gè)名稱是“波紋計(jì)數(shù)器”。

2022-10-11 17:16:44 7304

7304

7304

7304

環(huán)形計(jì)數(shù)器的種類、工作原理及應(yīng)用特性

環(huán)形計(jì)數(shù)器是使用移位寄存器構(gòu)成的時(shí)序邏輯電路。根據(jù)時(shí)鐘脈沖,相同的數(shù)據(jù)在計(jì)數(shù)器中循環(huán)。

2022-10-31 15:50:19 23784

23784

23784

23784

FPGA上的十六進(jìn)制計(jì)數(shù)器

電子發(fā)燒友網(wǎng)站提供《FPGA上的十六進(jìn)制計(jì)數(shù)器.zip》資料免費(fèi)下載

2022-11-23 10:47:06 10

10

10

10基于FPGA的十進(jìn)制計(jì)數(shù)器

本方案是一個(gè)基于 FPGA ?的十進(jìn)制計(jì)數(shù)器。共陽極 7 段顯示器上的 0 到 9 十進(jìn)制計(jì)數(shù)器,硬件在 Xilinx Spartan 6 FPGA 板上實(shí)現(xiàn)。

2022-12-20 14:52:25 4

4

4

4同步計(jì)數(shù)器和異步計(jì)數(shù)器是什么 同步計(jì)數(shù)器和異步計(jì)數(shù)器的主要區(qū)別?

在數(shù)字電子產(chǎn)品中,計(jì)數(shù)器是由一系列觸發(fā)器組成的時(shí)序邏輯電路。顧名思義,計(jì)數(shù)器用于計(jì)算輸入在負(fù)或正邊沿轉(zhuǎn)換中出現(xiàn)的次數(shù)。根據(jù)觸發(fā)觸發(fā)器的方式,計(jì)數(shù)器可以分為兩類:同步計(jì)數(shù)器和異步計(jì)數(shù)器。了解這兩種計(jì)數(shù)器的工作原理以及它們之間的區(qū)別。

2023-03-25 17:31:07 29524

29524

29524

29524

PLC計(jì)數(shù)器例子之3個(gè)計(jì)數(shù)器構(gòu)成的24小時(shí)時(shí)鐘

控制要求 利用 3 個(gè)計(jì)數(shù)器配合 1s 時(shí)鐘脈沖標(biāo)志 M1013,構(gòu)成一個(gè)標(biāo)準(zhǔn) 24 小時(shí)時(shí)鐘。 元件說明 控制程序 程序說明

2023-04-17 15:43:31 0

0

0

0在Verilog HDL中使用分頻器的8位計(jì)數(shù)器的設(shè)計(jì)

電子發(fā)燒友網(wǎng)站提供《在Verilog HDL中使用分頻器的8位計(jì)數(shù)器的設(shè)計(jì).zip》資料免費(fèi)下載

2023-06-15 10:14:44 0

0

0

0計(jì)數(shù)器電路原理解析

在學(xué)習(xí)嵌入式系統(tǒng)的過程中,定時(shí)器有關(guān)內(nèi)容的學(xué)習(xí)是必不可少的一個(gè)環(huán)節(jié)。定時(shí)器定時(shí)功能的實(shí)現(xiàn),最主要的還是靠其內(nèi)部的計(jì)數(shù)器。那么,計(jì)數(shù)器是如何實(shí)現(xiàn)計(jì)數(shù)功能的呢?接下來就來簡單介紹一下計(jì)數(shù)器的實(shí)現(xiàn)電路。

2023-09-25 14:18:48 4521

4521

4521

4521

基于Verilog的經(jīng)典數(shù)字電路設(shè)計(jì)—計(jì)數(shù)器

在數(shù)字系統(tǒng)中,使用得最多的時(shí)序電路差不多就是計(jì)數(shù)器了。計(jì)數(shù)器不僅能夠用于對時(shí)鐘脈沖計(jì)數(shù),還可以用于分頻、定時(shí)、產(chǎn)生節(jié)拍脈沖、產(chǎn)生脈沖序列以及進(jìn)行數(shù)字運(yùn)算等等。

2023-10-09 17:48:34 2631

2631

2631

2631

同步計(jì)數(shù)器和異步計(jì)數(shù)器的區(qū)別主要在哪里

同步計(jì)數(shù)器和異步計(jì)數(shù)器的區(qū)別詳解 同步計(jì)數(shù)器和異步計(jì)數(shù)器是數(shù)字電路中兩種常見的計(jì)數(shù)器類型,它們在實(shí)現(xiàn)方式和功能上存在明顯的區(qū)別。本文將詳細(xì)介紹同步計(jì)數(shù)器和異步計(jì)數(shù)器的區(qū)別,包括其工作原理、特點(diǎn)

2023-12-13 14:54:24 15772

15772

15772

157724017計(jì)數(shù)器的工作原理

中,我們將詳細(xì)介紹4017計(jì)數(shù)器的工作原理。 4017計(jì)數(shù)器的內(nèi)部結(jié)構(gòu)非常復(fù)雜,但核心的原理相對簡單。它包含一個(gè)時(shí)鐘輸入引腳(CLK),一個(gè)復(fù)位輸入引腳(RESET),以及10個(gè)輸出引腳(Q0-Q9)。時(shí)鐘輸入引腳接收來自外部時(shí)鐘源的時(shí)鐘信號,當(dāng)時(shí)鐘信

2023-12-15 09:24:28 6718

6718

6718

6718同步計(jì)數(shù)器和異步計(jì)數(shù)器各有什么特點(diǎn)

同步計(jì)數(shù)器和異步計(jì)數(shù)器是兩種常見的數(shù)據(jù)結(jié)構(gòu),它們都用于控制對共享資源的訪問。它們的主要作用是實(shí)現(xiàn)多個(gè)線程之間的同步和并發(fā)控制。盡管它們都被用于同步的目的,但它們有很多不同的特點(diǎn)和用例。 同步計(jì)數(shù)器

2023-12-15 10:49:43 3177

3177

3177

3177計(jì)數(shù)器怎么用 計(jì)數(shù)器的作用有哪些

計(jì)數(shù)器是一種被廣泛應(yīng)用于各個(gè)領(lǐng)域的實(shí)用工具,在我們的日常生活中隨處可見。無論是進(jìn)行時(shí)間統(tǒng)計(jì),協(xié)助工作任務(wù)的完成,還是用于科學(xué)研究和編程技術(shù),在各個(gè)領(lǐng)域都起到了重要的作用。本文將詳細(xì)介紹計(jì)數(shù)器

2024-02-03 10:04:14 9281

9281

9281

9281同步計(jì)數(shù)器和異步計(jì)數(shù)器的區(qū)別

在數(shù)字電子領(lǐng)域中,計(jì)數(shù)器是一種用于統(tǒng)計(jì)脈沖信號數(shù)量的重要設(shè)備。其中,同步計(jì)數(shù)器和異步計(jì)數(shù)器是兩種不同類型的計(jì)數(shù)器,它們在工作原理、特性以及應(yīng)用場景等方面存在著顯著的區(qū)別。本文將詳細(xì)探討這兩種計(jì)數(shù)器的區(qū)別,以便讀者能夠更深入地理解它們的工作原理和應(yīng)用場景。

2024-05-24 14:36:12 7834

7834

7834

7834計(jì)數(shù)器同步和異步怎么判斷

字系統(tǒng)中有著廣泛的應(yīng)用,如定時(shí)器、頻率計(jì)、脈沖計(jì)數(shù)器等。 二、同步計(jì)數(shù)器 1. 同步計(jì)數(shù)器的概念 同步計(jì)數(shù)器是一種所有觸發(fā)器的時(shí)鐘輸入端都連接在一起的計(jì)數(shù)器。在同步計(jì)數(shù)器中,所有的觸發(fā)器在同一個(gè)時(shí)鐘脈沖下同時(shí)更新狀態(tài)

2024-07-23 11:14:02 3322

3322

3322

3322 電子發(fā)燒友App

電子發(fā)燒友App

評論