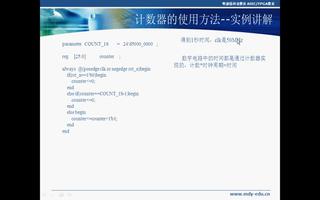

在數字電子技術中應用的最多的時序邏輯電路。計數器不僅能用于對時鐘脈沖計數,還可以用于分頻、定時、產生節拍脈沖和脈沖序列以及進行數字運算等。但是并無法顯示計算結果,一般都是要通過外接LCD或LED屏才能顯示。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

FPGA

+關注

關注

1662文章

22469瀏覽量

638153 -

計數器

+關注

關注

32文章

2319瀏覽量

98418 -

數字電子

+關注

關注

6文章

107瀏覽量

21919

發布評論請先 登錄

相關推薦

熱點推薦

定時器之計數器應用

之計數器應用。概述計數器是對外來脈沖信號計數,對來自于外部引腳P3.4(T0),P3.5(T1),P1.1(T2)的外部信號計數。在設置計數器

發表于 02-21 11:06

?2321次閱讀

單片機的定時器和計數器的詳細資料說明

本文檔的主要內容詳細介紹的是單片機的定時器和計數器的詳細資料說明包括了:1.51定時/計數器簡介,2.使用51定時/計數器步驟,3.51定時/計數器

發表于 05-21 08:00

?1次下載

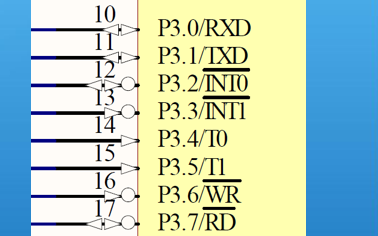

FPGA基礎應用計數器的實例詳細說明

該計數器從0 計數到4294967295,然后回滾到0 并重新開始計數。它只需要FPGA 上一點點的資源就可以迅速完成計數,這都多虧了

發表于 12-11 17:26

?12次下載

基于FPGA的十進制計數器

本方案是一個基于 FPGA ?的十進制計數器。共陽極 7 段顯示器上的 0 到 9 十進制計數器,硬件在 Xilinx Spartan 6

發表于 12-20 14:52

?4次下載

FPGA之計數器的練習(6)

FPGA之計數器的練習(6)

評論