有時候在復雜系統設計的時候會用遇到讓“計數器在某個區間內來回不停遞增遞減”的問題。

話不多說,我們直接上代碼。

以0-10的循環計數為例。

工具:Modelsim, VScode

1.準備工作

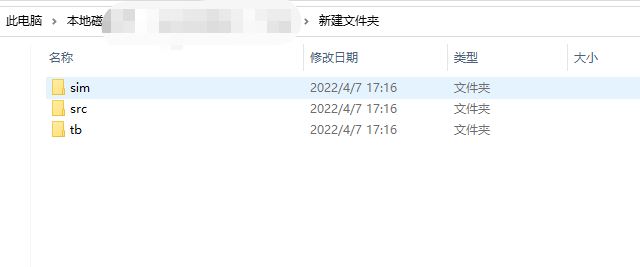

首先在電腦上新建三個文件夾,SRC、TB以及SIM,用來放置源代碼、仿真文件以及仿真工程文件。

一定不要怕麻煩,特別是新手一定要注意代碼的分類工作!良好的分類能夠大大的提高工作效率。

剛接觸代碼量小,幾十行代碼一個文件就搞定了。但是隨著從業時間的增加,工作復雜度的提升,代碼的難度也會隨之提升,如果不做好分類管理,面對幾十個源代碼,十幾個仿真文件……崩潰是必然的。

請注意:一定不能有中文路徑!!

這樣是錯誤的

這樣是錯誤的

應該這樣修改

應該這樣修改2.工程建立

- 在src文件中添加一個.v文件,名字自擬,最好能夠體現出文件的特性。

module test (

input sys_clk,

input rst_n,

);

reg flag;

reg [7:0] adc_data;

always @(posedge sys_clk or negedge rst_n) begin

if (~rst_n)

flag <= 1'd0;

else

case (flag)

1'd0:

if (adc_data == 8'd9) // -1

flag <= 1'd1;

else

flag <= 1'd0;

1'd1:

if (adc_data == 8'd1) // +1

flag <= 1'd0;

else

flag <= 1'd1;

default: flag <= flag;

endcase

end

always @(posedge sys_clk or negedge rst_n) begin

if (~rst_n) begin

adc_data <= 8'd0;

end

else if (flag == 1'd0)

adc_data <= adc_data + 8'd1;

else if (flag == 1'd1)

adc_data <= adc_data - 8'd1;

else

adc_data <= adc_data;

end

endmodule

- 在tb文件夾中新建文件,給出仿真所需要的激勵。我們此次所需的只有時鐘和復位。時鐘設置為50Mhz,復位1000ns。

`timescale 1 ns /1 ps

module tb_test;

reg sys_clk;

reg rst_n;

test u_tb_test(

.sys_clk (sys_clk),

.rst_n (rst_n)

);

initial begin

sys_clk = 0;

rst_n = 0;

#1000;

rst_n = 1;

#20000;

end

always #10 sys_clk = ~ sys_clk;

endmodule

- 在sim文件夾中新建一個Modelsim仿真工程,添加src,tb中的文件,此過程不再展示。

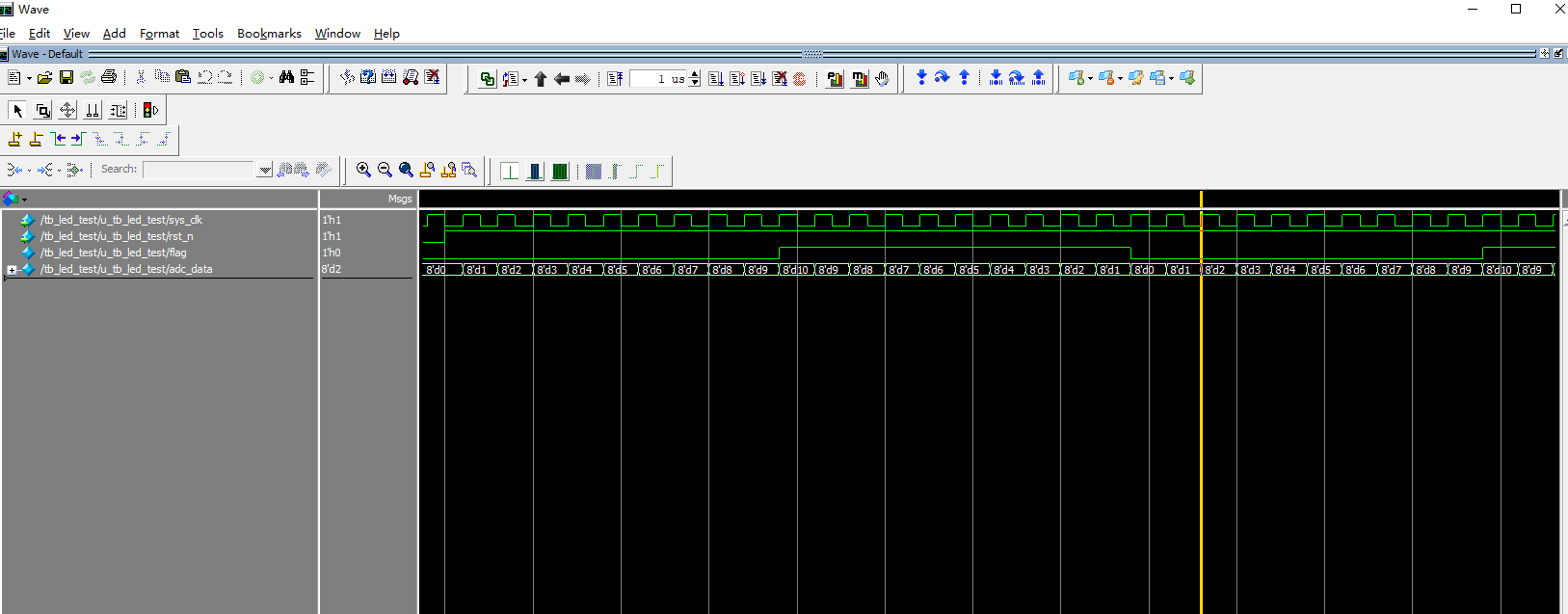

3.仿真驗證

仿真1us,觀察波形。實現了0-10直接的循環計數,設計成功。

審核編輯:符乾江

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

FPGA

+關注

關注

1660文章

22412瀏覽量

636356 -

仿真分析

+關注

關注

3文章

115瀏覽量

34194

發布評論請先 登錄

相關推薦

熱點推薦

MAXIM ICM7225:4 又 1/2 位計數器/解碼器/驅動器的技術剖析

MAXIM ICM7224/7225:4 又 1/2 位計數器/解碼器/驅動器的技術剖析 作為電子工程師,在設計各類計數、頻率測量及顯示電路

MAXIM ICM7224:高速4.5位計數器、解碼器與驅動器的卓越之選

MAXIM ICM7224/7225:高速4.5位計數器、解碼器與驅動器的卓越之選 一、引言 在電子設計領域,計數器、解碼

探索Maxim ICM7217:4位(LED)可預設上下計數器的卓越性能

探索Maxim ICM7217:4位(LED)可預設上下計數器的卓越性能 在電子設計領域,計數器是一種常見且重要的元件,廣泛應用于各種計時、計數和頻率測量等場景。今天,我們將深入探討M

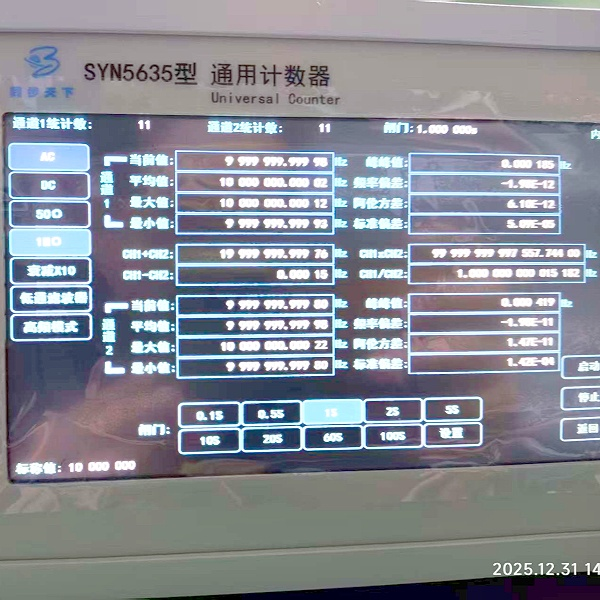

數字頻率計數器在計量檢測中的重要性 頻率計數器 高精度通用計數器

SYN5635型數字頻率計數器是計量檢測領域的核心基礎儀器,其核心價值在于提供高精度頻率與時間基準、保障量值統一、支撐全鏈路質量控制與合規溯源,是電子、通信、航天等領域測量可靠性的關鍵保障。 一

頻率計數器/定時器 時間間隔計數器的應用領域和范圍的深度解析 頻率計數器模塊

在精密電子測量、科研實驗、工業控制等領域,時間間隔的精準測量是保障系統性能與數據可靠性的關鍵環節。 SYN5620A時間間隔計數器模塊 作為一款集成化、高性能的測量單元,憑借其高精度、寬量程、高

如何利用Verilog HDL在FPGA上實現SRAM的讀寫測試

本篇將詳細介紹如何利用Verilog HDL在FPGA上實現SRAM的讀寫測試。SRAM是一種非易失性存儲器,具有高速讀取和寫入的特點。在F

雷擊計數器的種類和綜合選型部署解決方案

一、雷擊計數器的定義與作用 雷擊計數器(Lightning Counter,又稱雷電計數器、雷擊記錄儀)是安裝在避雷針、接閃桿、SPD(浪涌保護器)或下引線回路中,用于記錄雷擊或浪涌事

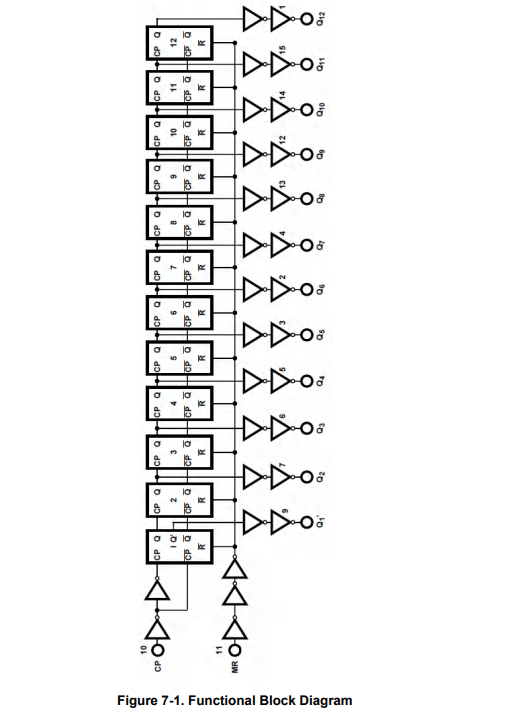

Texas Instruments CD74HC4040/CD74HCT4040 12級二進制計數器數據手冊

Texas Instruments CD74HC4040/CD74HCT4040 12級二進制計數器是控制器觸發器的高速計數器級。在每個輸入

雷電(雷擊)計數器的原理、作用及行業應用解決方案

安全事故。雷電(雷擊)計數器作為防雷系統中的重要組成部分,扮演著“記錄雷擊事件、輔助安全運維”的關鍵角色,已經成為智能防雷系統中不可或缺的一環。 二、雷電(雷擊)計數器的原理 1. 工作原理 雷電計數器主要依靠電磁

MCU定時器/計數器

RISC-V核低功耗MCU通過靈活的定時器架構、低功耗模式適配及硬件級中斷優化,在工業控制、智能家居等場景中實現高精度計時與能耗控制的協同設計,滿足復雜任務調度與實時響應的雙重需求?。 一、?硬件

Verilog實現計數器在某個區間內循環計數,遞增遞減

Verilog實現計數器在某個區間內循環計數,遞增遞減

評論