提出一種基于FPGA技術的多路數字量采集模塊,利用FPGA的I/O端口數多且可編程設置的特點,配以VHDL編寫的 FPGA內部邏輯,實現采集多路數字量信號。

2015-05-15 12:09:29 4721

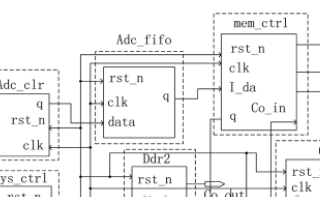

4721 為了實現激光-水聲淺海地形遙感探測中水聲信號的實時解調與處理,本文提出了一種基于FPGA的激光多普勒測振計信號采集與處理系統的設計方案。以Cyclone Ⅱ系列FPGA為核心控制模塊,結合

2013-10-29 10:10:02 3059

3059

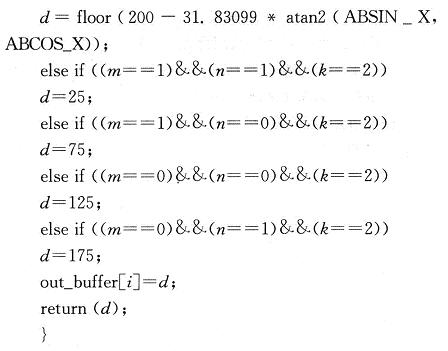

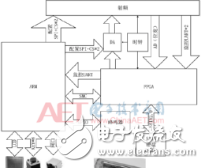

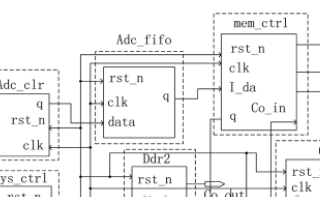

本文以FPGA作為核心處理器,提出了一種基于FPGA多路機載冗余圖像處理系統的設計方案。##整個系統顯示的分辨率為1600×1200@60 Hz,信號位為真彩色24b,則一幀圖像所需需要存儲的容量C≈47 Mb。##讀寫操作交替進行仿真圖如圖5所示。圖5中包含了兩個寫入操作,一個讀取操作。

2014-01-07 10:28:32 3905

3905

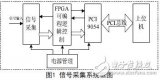

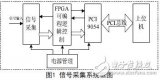

為解決現場測試系統中微弱信號的高速實時采集處理和及時可靠存儲的問題,本文提出了基于PCI總線的數據采集電路的設計方案,該方案將模擬信號通過高速A/D芯片有效采樣,在FPGA的控制下將數據上傳到PC機

2014-01-24 09:45:29 4027

4027

高通道密度數據采集系統用于醫療成像、工業過程控制、自動測試設備和40G/100G光通信系統可將眾多傳感器的信號多路復用至少量ADC,隨后依序轉換每一通道。 ##多路復用數據采集信號鏈##多路復用數據采集系統布局考慮因素

2014-09-16 18:31:24 6243

6243

隨著現代檢測技術和科技水平的高速發展,信號采集技術的應用范圍越來越廣泛[1]。與此同時,對信號采集系統的采集精度、采樣率以及便攜性等設計需求提出了更高的要求。現場可編程門陣列(FPGA)具有邏輯門

2020-01-26 16:58:00 2987

2987

多片FPGA之間的互連,經常提到多路復用的概念,也經常提到TDM的概念,正確理解多路復用在多片FPGA原型驗證系統中的機理,尤其是時序機制,對于我們正確看待和理解多片FPGA原型系統的性能有很好的促進作用。下圖是一個使用多路復用器后接采樣FF的多路復用解決方案的示例。

2023-06-06 10:04:35 2286

2286

比較器將網線傳輸過來的差分信號轉為單端信號,該信號時鐘頻率為100M,電平標準能滿足FPGA的輸入電平標準,波形質量尚可。單端信號直接連接到FPGA,現在如果想用FPGA直接采集,應該怎么處理呢,是當作異步信號直接打拍嗎,過采樣的話時鐘頻率不夠。時鐘恢復目前來不及實現。

2020-03-07 16:01:37

本人想做一個陣列接收模塊,初步想法是FPGA+adc芯片,采集16Khz左右正弦信號,得到其相位與幅度信息。如果要做64路,adc采用并行ad,這樣需要的IO口會很多,但如果不用一片fpga就不能同時采集信號。想問一下有沒有什么好的解決方案呢?求大佬關注一下!!!謝謝!!!

2019-03-06 19:01:51

光柵作為精密測量的一種工具,由于他本身具有的優點,已在精密儀器、坐標測量、精確定位、高精度精密加工等領域得到了廣泛的應用。光柵測量技術是以光柵相對移動所形成的莫爾條紋信號為基礎的,對此信號進行一系列

2020-08-05 06:24:21

我自己做了一個光柵編碼器,主要有四個信號,我想對這四個信號進行檢測,然后傳到電腦上顯示波形和各個數據,來驗證編碼器的精度等信息。3個電機轉子相對于定子的位置信號,和1個速度信號,就是4個脈沖信號,我

2013-04-21 17:40:13

該文檔為基于FPGA的多路模擬數據采集接口設計講解文檔,介紹一種基于 8,RQ 的多路模擬數據采集接口的設計方案。該方案使用Max1281 作為模數轉換芯片,在 APA150 FPGA 中設計和實現了相關的接口控制、配置和數據存儲模塊;給出了系統設計框圖、FPGA開發要點和仿真波形。

2018-09-21 14:37:00

DM8168可以采集多路DVI信號嗎?如何實現呢?

2018-05-28 04:14:39

本帖最后由 qujian112 于 2016-1-20 15:31 編輯

GPS軌跡和氣壓傳感器等多路數據同步采集與存儲實現方案簡易說明1. 網絡組成示意圖:2.項目名稱:GPS軌跡和氣

2016-01-20 15:29:49

NI數據采集卡可以采集光柵尺輸出的脈沖信號嗎?如果能實現,該怎么設置DAQ助手呢,是用模擬量還是數字量呢?

2012-12-10 16:10:53

本帖最后由 依然Dirk 于 2015-1-21 15:40 編輯

Proteus + C51多路信號采集器

2015-01-21 15:29:45

可行后續需采購大量板用于實物的制作。項目描述:多路10mV左右微信號分別采集放大后傳送至單片機,單片機分別對每個IO口的信號進行分析計算,統計當前IO口脈沖信號的寬度、頻率,持續的時間長短,結果保存到數組分別用于與電腦通訊及顯示在TFT顯示屏上,支持斷電記憶。

2015-07-06 17:22:25

FPGA的多路數據采集分析儀 3、計劃第一周:安裝環境,熟悉開發環境第二周:架構設計,編寫方案,第三-四周:編制Verilog程序第五周:串口圖像顯示第六-七周:整體聯調,完成設計4、預計成果1、Verilog采集程序和電壓觸發程序2、Verilog串口程序3、顯示終端和電壓采集觸發等功能實現。

2019-06-24 14:25:05

申請理由:項目描述:項目名稱:基于FPGA的多路實時運動數據采集器項目描述:結合ARM內核單片機的易操作性與FPGA的高速、并行運算的特點,設計一款快速、多路、實時運動數據采集器。一共包含14路信號

2016-08-15 17:13:19

你好:

我想問一下,我要使用FPGA實現對AD7768芯片產生的多路AD數據進行采集,除了設置MODE,FORMATE之類的以外,我只使用一片AD7768,是否需要使用START信號

2023-12-11 07:24:57

一般的50線的角度光柵傳感器,輸出信號是A相和B相,90度相位差的方波信號。可以使用FPGA對輸出信號使用時鐘脈沖細分技術進行20細分嗎?想盡量使電路簡化,因此就不考慮模擬電路的方法了。此外再將

2013-06-04 14:59:24

最近在做畢業設計,關于ADE7755的集中電能測量系統,采樣部分出現了問題,ADE7755只能采集一路電壓和電流信號,請問怎么把多路的電流信號送入ADE7755呢,單片機用的89C52,看門狗用

2013-05-05 12:12:26

小弟最近學了下adc芯片,想問下如果想采集很多路信號(比如上百上千)該怎么辦,不可能用很多adc芯片吧,是不是還有些其他輔助的芯片或者協議啥的。或者就說想采集上百上千路信號,有沒有什么比較好的方案?

2017-11-19 21:26:32

在FPGA上實現時鐘信號的多路同步輸出該怎么做呢?好像要用到FPGA內部的PLL,將時鐘信號分成多路輸送到其他板塊,求高手解答該怎么做輸入時鐘由一個50M的晶振提供

2023-03-21 14:51:29

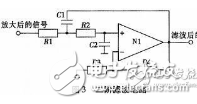

切換命令后,FPGA通過通道切換子模塊,實現對外圍芯片的控制,完成多路不同通道的管理和切換。2.4 ADC信號采集模塊ADC信號采集模塊由電壓采集和信號調理子模塊組成。電壓采集子模塊選用ADI公司

2021-07-12 08:30:00

【作者】:韋雄波;艾武;閆光亞;陳冰;【來源】:《湖北工業大學學報》2010年01期【摘要】:利用FPGA的高速運算能力,建立一個數據采集處理模塊,該模塊的任務是采集光柵尺輸入信號,對采集到的信號

2010-04-24 09:07:07

的信號量特別多時(特別是各種信號量、狀態量),僅僅靠用普通MCU的資源就往往難以完成任務。電子論壇所提出的一種基于FPGA的模擬量、數字量采集與處理系統,利用FPGA的I/O端口多,并且可以自由編程支配

2011-08-23 10:15:34

在石油地震勘探中,地震儀通過地震檢波器采集信號。地震檢波器是為了接收和記錄地震波而設計的一種精密的機械、電子組合裝置,是地震勘探數據采集中的重要環節,其性能好壞直接影響地震記錄質量和地震資料的解釋

2019-10-14 08:03:53

在石油地震勘探中,地震儀通過地震檢波器采集信號。地震檢波器是為了接收和記錄地震波而設計的一種精密的機械、電子組合裝置,是地震勘探數據采集中的重要環節,其性能好壞直接影響地震記錄質量和地震資料的解釋

2019-08-08 08:21:56

在石油地震勘探中,地震儀通過地震檢波器采集信號。地震檢波器是為了接收和記錄地震波而設計的一種精密的機械、電子組合裝置,是地震勘探數據采集中的重要環節,其性能好壞直接影響地震記錄質量和地震資料的解釋

2019-08-30 07:56:45

在石油地震勘探中,地震儀通過地震檢波器采集信號。地震檢波器是為了接收和記錄地震波而設計的一種精密的機械、電子組合裝置,是地震勘探數據采集中的重要環節,其性能好壞直接影響地震記錄質量和地震資料的解釋

2019-08-08 08:30:00

在石油地震勘探中,地震儀通過地震檢波器采集信號。地震檢波器是為了接收和記錄地震波而設計的一種精密的機械、電子組合裝置,是地震勘探數據采集中的重要環節,其性能好壞直接影響地震記錄質量和地震資料的解釋

2019-09-05 06:25:12

AD7606調試筆記:采集多路不正常,少采集幾路就正常了文章目錄AD7606調試筆記:采集多路不正常,少采集幾路就正常了問題描述:查錯方案:處理速度不夠時序不對解決辦法延時轉換完成讀取是否影響?結論

2022-01-07 07:37:04

求一種多路模擬數字采集與處理系統的設計方案

2021-04-28 07:04:52

本文針對遙測應用,以大容量FPGA器件為核心,實現了電源獨立的不同頻率、不同波形的多路模擬量信號源。

2021-04-30 06:12:38

請教各位大大:我最近做FPGA采集100MHz的信號,另一路同步觸發。但觸發信號上升沿在40ns左右,最后導致信號波形左右晃動。請問在FPGA中如何處理可以準確采集到觸發信號,排除左右晃動的情況?

2013-03-06 00:22:42

可以將算法通過FPGA實現。通過FPGA的實時信號處理,數據率可以大大減小。方案4:在采集卡旁邊增加一塊PCIE板,上面FPGA具有磁盤控制功能,能在機箱上連接8-16塊SSD盤,實時存儲速度大于

2016-08-15 14:59:39

小弟現在要采集多路4-20mA的電流信號,查資料看的 多路模擬開關的輸入端好像都是要求電壓信號,所以想問下前輩們,有沒有選擇電流信號的多路模擬開關?還是只能把電流信號轉為電壓信號?

2019-02-27 02:48:03

輸入為多路開關量的數據如何采集?

輸入為多路開關量的數據(如0或1)如何采集,怎樣轉化為電壓或電流信號?

2024-05-10 08:22:12

針對遙感系統的工作環境特點、待處理信號的頻譜特征以及系統信噪比等要求,綜合比較多種信號采集系統方案的優缺點,本文提出了一種基于FPGA的激光多普勒測振計信號采集與處理系統的設計方案,該方案可以實現光

2019-06-24 07:16:30

根據電力監控系統的要求,提出一種基于FPGA技術的多路交流信號采集與處理系統的設計方法。分析整個系統的結構,并討論FPGA內部硬件資源的劃分和軟件的設計方案,以及各個功能

2009-05-16 14:47:58 27

27 本文介紹了一種利用軟件定時器在AT87C51 單片機上實現多路信號異步采集的實用技術。詳細描述了采集系統的硬件結構、軟件流程和通訊機制。關鍵字:單片機軟件定時器異步信

2009-06-09 08:51:00 40

40 數據采集系統是整個地震勘探物理模擬實驗系統的關鍵環節。文章介紹運用FPGA 芯片控制,實現對高速模擬地震信號的數據采集技術,以及USB.2.0 接口總線軟硬件的實現技術。該系統

2009-07-08 16:30:52 21

21 本文介紹了一種基于FPGA 的高速多路數據采集系統的設計方案,描述了系統的主要組成及FPGA 的實現方法。在硬件上FPGA 采用ACEX1K100 器件,用于實現A/D 轉換器的控制電路、多路

2009-12-19 16:02:33 50

50 波長信號的解調是實現光纖光柵傳感網絡的關鍵,基于現有的光纖光柵傳感器解調方法,提出一種基于FPGA的雙匹配光纖光柵解調方法,此系統是一種高速率、高精度、低成本

2010-11-22 16:05:14 37

37

針對測控系統中監測信號較多的情況,提出了一種基于FPGA的多路數字信號采集模塊設計。采集數字信號的高低狀態和測量其中一路信號的頻率,并采集脈沖信號的脈寬

2010-12-16 15:38:49 36

36 FPGA的多路可控脈沖延遲系統設計

采用數字方法和模擬方法設計了一種最大分辨率為0.15 ns級的多路脈沖延遲系統,可以實現對連續脈沖信號的高分辨

2009-03-29 15:09:48 2975

2975

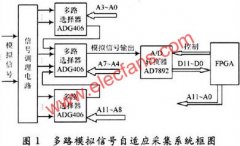

摘要:提出一種基于FPGA技術的多路模擬量、數字量采集與處理系統的設計方案,分析整個系統的結構,并討論FPGA內部硬件資源的劃分和軟件的設計方案等。本設計

2009-06-20 15:05:11 1956

1956 基于DSP與FPGA的光柵地震檢波器的信號處理

0 引 言

在石油地震勘探中,地震儀通過地震檢波器采集信號。地震檢波器是為了接收和記錄地

2010-01-20 11:26:15 1094

1094

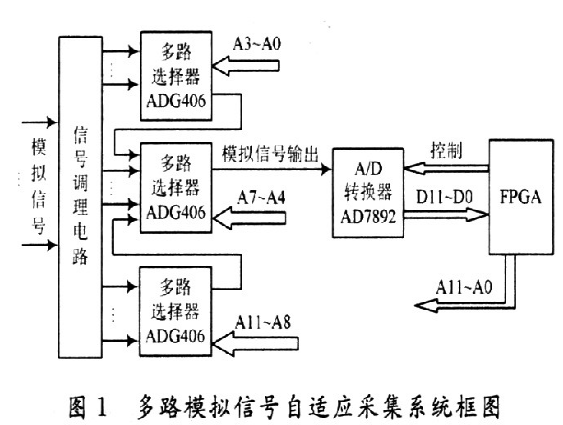

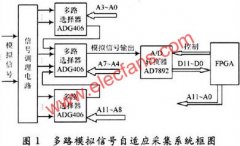

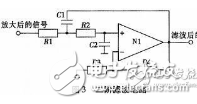

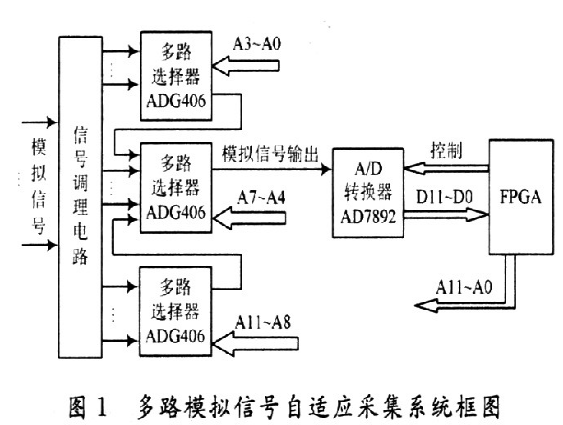

本文提供的方式有效地解決了這個問題,既簡化了前端信號調理電路的復雜度,又充分利用了A/D轉換器的輸入電壓動態范圍和量化位數優勢,實現了對多路模擬信號的自適應采集,對其他信號采集系統也具有一定的借鑒意義。

2011-01-14 23:27:55 1991

1991

在航空、航天領域中的一些應用于慣性測試的精密離心機,其轉速信號通常是由分體式光柵測量系統輸出的光柵信號經過具有細分、辨向、整形功能的電子系統后而得到的。

2011-05-26 10:58:46 1152

1152

研究了能夠同時對多路 光電編碼器 脈沖信號進行細分、計數以及傳輸的數據采集處理系統。提出了以高度集成的FPGA芯片為核心的設計方式,實現6路光電編碼器信號的同步實時處理。坐

2011-08-18 16:33:15 92

92 本課題基于關節臂式坐標測量機的研制需要,研究了 光柵傳感器 輸出信號的特點和FPGA開發技術,以FPGA為載體,設計了一個基于FPGA的多路光柵數據采集系統。 本文主要介紹了光柵傳感

2011-08-18 16:34:55 78

78 本文提出的基于FPGA的空間電場信號采集系統應用于探空火箭有效載荷——箭載電場儀探頭后端信號采集與處理部分,也可以為地面電場儀處理電場信號提供服務。該方案解決了電場信號

2012-12-27 11:39:42 4313

4313 介紹了一種基于FPGA的圓光柵編碼器數據采集系統的設計方法。通過分析圓光柵的實際工作情況,將系統分為三大模塊,詳細闡述了濾波模塊實現消除高頻信號干擾,計數模塊實現四倍頻

2013-09-25 16:10:54 28

28 于FPGA的高速多路數據采集系統的設計。

2016-05-10 13:45:28 41

41 基于FPGA高速數據采集的解決方案,下來看看

2016-05-11 09:46:01 13

13 多路同步數字調相信號源一般采用單片機和多片專用DDS芯片配合實現。該技術同步實現復雜,成本高。給出了一種基于FPGA的多路同步信號源的設計方法,通過VHDL語言硬件編程實現了基于單片FPGA

2016-05-27 13:47:49 9190

9190

基于51單片的的多路信號采集,包括仿真和源程序

2017-01-07 15:53:30 66

66 基于FPGA的多路數據實時采集與傳輸系統_馮希辰

2017-01-08 10:30:29 3

3 上一篇寫了基于Xilinx FPGA的通用信號發生器的案例,反響比較好,很多朋友和我探討相關的技術,其中就涉及到信號的采集,為了使該文更有血有肉,我在寫一篇基于Xilinx FPGA的通用信號采集器,望能形成呼應,以解答大家的疑問。

2017-02-11 03:11:37 2134

2134

光柵計量技術在工業計量領域得到了飛速發展,其中光柵傳感器在線位移和角位移測量中得到廣泛應用。對光柵信號進行處理有很多方法,如傳統電路、 單片機或者現場可編程門陣列(FPGA)等。隨著電子技術

2017-08-30 18:10:14 5

5 基于STM32的多路電壓采集研究

2017-09-28 11:26:08 95

95 基于PCIE通信總線的FPGA開發板與多路AD采集卡設計并實現了滿足系統要求的數據采集平臺。首先簡要介紹了該采集平臺的結構及PCIE通信鏈路的搭建,然后設計實現了一種數據連續存儲的方法,最后通過實驗驗證了該方法的可行性及采集平臺的整體性能。

2017-11-15 14:21:02 12246

12246

設計了一種基于ARM與FPGA的便攜式GNSS導航信號采集回放系統。該系統可采集復雜情況下的導航衛星信號,并且增益可控,為導航接收機測試提供了特定的信號源。系統將導航衛星信號經射頻電路轉換為數字中頻信號

2017-11-16 13:44:42 2463

2463

針對機械設備運行中的振動監控,設計振動信號采集系統,提出了一種基于FPGA的振動信號采集系統的設計方案。重點闡述了系統硬件結構組成、信號調理電路和數據采集模塊的設計,同時對A/D采樣的控制邏輯進行了討論。經試驗驗證表明,該系統可達到采樣率10 K每秒、采集精度16位,能夠滿足實時性和精度要求。

2017-11-17 11:04:38 8468

8468

在振動信號采集和處理系統設計中,信號的處理時間與可靠性決定著系統應用的可行性。本文設計了一種基于FPGA的振動信號采集處理系統,該系統通過振動信號采集電路、抗混疊濾波電路、AD采樣電路將電荷信號轉化

2017-11-18 05:26:02 4815

4815

基于運放的信號發生器精度低且穩定性和可調節性差,而基于DDS的信號發生器則成本高、電路復雜。為此提出了基于FPGA+PWM的多路信號發生器設計方法。該方法硬件上無需DAC與多路模擬開關,由FPGA產生調制輸出波形信號所需的PWM脈沖波,經二階低通濾波和放大電路后即可得到所需波形信號。

2017-11-18 09:42:01 7556

7556

DM9000A 完成網絡接口設計,在FPGA 內部實現了對光柵傳感信號質心解調算法的程序設計和以太網接口控制程序的設計,FPGA具有多通道高速同步解算的能力,在對F-P濾波器500Hz的掃描速率下,很好地實現了光纖光柵波長的同步實時解算。

2017-11-18 12:04:50 3798

3798

的效果,依據該原理,可以實現圖像的采集及在VGA顯示屏上顯示的實現。利用FPGA產生VGA時序信號和發送圖像信息,并將其作為圖像信號采集系統,將大大減小圖像開發的難度和投入。

2017-11-18 12:42:02 2597

2597 近年來,雷達在軍用和民用領域都獲得了巨大的發展。雷達信號處理系統是雷達的關鍵模塊,對雷達定位精度起著決定性作用。FPGA 以其眾多的優點,在雷達信號處理系統中被廣泛使用。本文探究FPGA 在雷達信號

2017-11-22 07:25:02 5151

5151

為打破實際應用過程時信號采集電路中人為參與的局限,以嵌入式系統作為數據采集的應用平臺,提出了一種基于STM32與FPGA相結合的武器裝備信號采集電路設計方案.研究了PPI顯示器信號采集電路的信息采集

2018-01-31 15:31:20 5

5 了前端信號調理電路的復雜度,又充分利用了A/D轉換器的輸入電壓動態范圍和量化位數優勢,實現了對多路模擬信號的自適應采集,對其他信號采集系統也具有一定的借鑒意義。

2018-08-21 09:20:00 2604

2604

本系統采用基于FPGA的DMA技術高速緩存多路并行數據,通過數據重組將數據有序發送給處理系統,用于數據的顯示與分析。系統采用了嵌入式技術,達到了便攜效果,從而更好地適應設備的工作環境。并行數字信號

2019-04-22 08:25:00 7127

7127

介紹了一種基于FPGA的多路同步、實時數據采集新方案,著重對其硬件結構和控制邏輯進行了闡述,并從工程實踐方面給出了電路的實現原則。該方案控制方式靈活可變、具有一定的擴展性和通用性,已被成功地應用于雙模信息融合系統的設計中,實現了對雷達導引頭的多信號實時同步采集。

2018-10-12 16:14:59 17

17 介紹了一種基于FPGA的高速多路數據采集系統的設計方案,描述了系統的主要組成及FPGA的實現方法,并用v∞L語言設計的狀態杌在Qmr嚙Ⅱ開發軟件中進行仿真。該系統在通用數據采集系統的基礎上,增加數

2018-10-12 16:15:09 14

14 為了實現對58路模擬信號進行不同頻率的采集,設計了一種以現場可編程門陣列(FPGA)為核心的多路模擬信號采集模塊。該模塊采用FPGA芯片XC2S30作為系統的核心控制器件來實現對A/D轉換器的控制

2018-10-12 16:15:21 24

24 結合數據采集系統在航天遙感中的應用“介紹了一種基于FPGA 的多路數據采集系統”給出了硬件原理框圖“并對系統進行了分解”而后討論了影響系統性能的因素實際應用證明“采用該方法設計的系統能有效地完成多路同步高速數據采集任務

2018-10-16 16:18:45 18

18 介紹一~種基于FPGA的多路模擬數據采集接口的設計方案。該方案使用Max1281作為模數轉換芯片,在APA150 FPGA中設計和實現了相關的接口控制、配置和數據存儲模塊;給出了系統設計框圖、FPGA開發要點和仿真波形。

2018-10-16 16:18:00 18

18 本文提出了一種實現信號采集方案,介紹了由ARM 處理器S3C2410 和EP2C8 FPGA 組成的高速信號采集系統的系統設計,并著重介紹前端硬件的設計,并就ARM 處理器和FPGA 的互聯設計進行探討。利用FPGA 硬件控制A/D 轉換,達到了較好的效果,實現了信號的采集與存儲。

2018-11-02 15:46:01 12

12 數字圖像處理技術廣泛地應用在信息處理領域,如何高效、靈活地將現實世界圖像數字化是信息處理的關鍵技術之一。本文基于FPGA技術設計了一個高速多路視頻數據采集系統。基于Altera Cyclone II

2019-02-11 09:39:26 2549

2549

設計了一種基于 TI DSP TMS320C6713B 和ALtera Cyclone 系列FPGA 的數據采集模塊,使用FPGA 做多路串行AD 器件的信號采集控制和數據緩沖,同時利用DSP

2019-03-05 16:30:29 17

17 提出了一種基于FPGA+ARM的多路視頻采集系統的設計與實現方法。該視頻采集系統不僅能對多路快速變化的視頻信號進行采集和處理,而且能應用為系統信號發生設備.系統采用FPGA為核心高速時序邏輯控制

2019-11-19 15:51:42 21

21 設計了一套高速線陣CCD信號采集系統,采用FPGA+DSP的數字處理方案,能滿足光信號的實時識別和處理,可用于研究靜態和動態小粒子的光散射彩虹特性。

2019-11-21 17:32:39 27

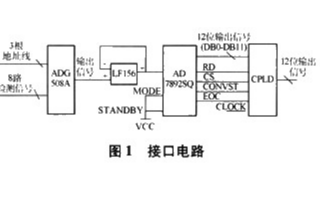

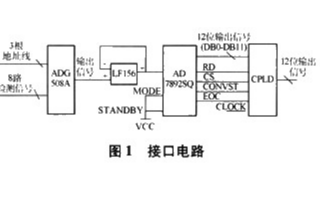

27 本系統以AD7892SQ和CPLD(復雜可編程邏輯器件)為核心設計了一個多路信號采集電路,包括模擬多路復用、集成放大、A/D轉換,CPLD控制等。采用硬件描述語言Verilog HDL編程,通過采用CPLD使數據采集的實時性得到提高。

2020-03-03 17:21:43 1958

1958

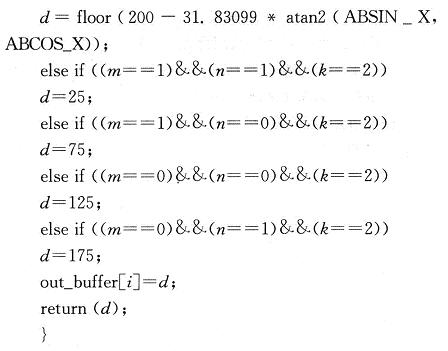

主要介紹基于FPGA實現多路模擬信號自適應采集系統的設計。該系統主要包括軟件和硬件兩部分:硬件主要采用FPGA芯片,AD7982—1,ADG406和運放AD824來搭建硬件平臺;軟件包括FPGA程序

2021-02-02 15:52:34 5

5 為滿足對旋翼槳葉表面多測點靈敏氣壓傳感器信號的高速、并行、高精度數據采集,同時具備程控增益放大、抗混疊濾波等功能,設計了一種以FPCA作為核心控制單元的便攜式多路高精度前置采集系統。待測信號先由信號

2021-06-01 09:40:47 7

7 該模塊支持4路高達5MHz的差分光柵尺信號采集,采用的是標準的Modbus RTU通訊協議,可以自動換算出實際的長度值,工程值。測量精度高,可以兼容各種差分的光柵尺,磁柵尺,以及編碼器。

2022-12-16 16:05:44 1464

1464

摘要:波長信號的解調是實現光纖光柵傳感網絡的關鍵,基于現有的光纖光柵傳感器解調方法,提出一種基于FPGA的雙匹配光纖光柵解調方法,此系統是一種高速率、高精度、低成本的解調系統,并且通過引入雙匹配光柵

2023-01-31 15:05:14 1

1 文章介紹了光柵尺是如何工作的,并用數據采集卡采集了光柵尺的位移信息。

2025-08-15 18:02:53 1429

1429

電子發燒友App

電子發燒友App

評論