算法建模 - 基于Verilog HDL濾波器的設計

本文導航

- 第 1 頁:基于Verilog HDL濾波器的設計

- 第 2 頁:頂層設計

- 第 3 頁:算法建模

- 濾波器(185088)

- 自動化設計(10769)

相關推薦

熱點推薦

基于matlab FPGA verilog的FIR濾波器設計

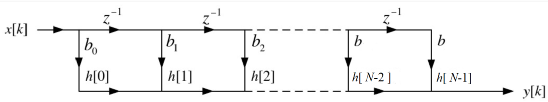

本例程實現8階濾波器,9個系數,由于系數的對稱性,h(0)=h(8),h1(1)=h(7),h(2)=h(6),h(3)=h(5),h(4)為中間單獨一個系數。根據公式: 實現框圖: 推導出當系數N

2018-06-08 09:41:47 12946

12946

12946

12946

Verilog HDL入門教程(全集)

的具體控制和運行。Verilog HDL語言不僅定義了語法,而且對每個語法結構都定義了清晰的模擬、仿真語義。因此,用這種語言編寫的模型能夠使用 Ve r i l o g仿真器進行驗證。語言從C編程語言

2020-11-30 19:03:38

Verilog HDL的基本語法

Verilog HDL是一種用于數字邏輯電路設計的語言。用Verilog HDL描述的電路設計就是該電路的Verilog HDL模型。Verilog HDL既是一種行為描述的語言也是一種結構描述

2019-09-06 09:14:16

FPGA設計中 Verilog HDL實現基本的圖像濾波處理仿真

今天給大俠帶來FPGA設計中用Verilog HDL實現基本的圖像濾波處理仿真,話不多說,上貨。

1、用matlab代碼,準備好把圖片轉化成Vivado Simulator識別的格式,即每行一

2024-05-20 16:44:47

【FPGA學習】Verilog HDL有哪些特點

Verilog HDL 的特點Verilog HDL 語言不僅定義了語法,而且對每個語法結構都定義了清晰的模擬、仿真語義。使用這種語言編寫的模型可以方便地使用 Verilog 仿真器進行驗證

2018-09-18 09:33:31

單級CIC濾波器Verilog設計

本文將詳細介紹使用Verilog HDL設計單級CIC濾波器的方法。CIC濾波器多速率信號處理系統中最主要的還是濾波器的設計:抽取和內插后不能產生頻譜混疊、占用資源少、運算速度快。上一篇介紹了多速率

2020-09-28 09:36:54

基于matlab FPGA verilog的FIR濾波器設計

今天和大俠簡單聊一聊基于matlab FPGA verilog的FIR濾波器設計,話不多說,上貨。

本次設計實現8階濾波器,9個系數,由于系數的對稱性,h(0)=h(8),h1(1)=h(7

2024-07-04 20:11:05

并行FIR濾波器Verilog設計

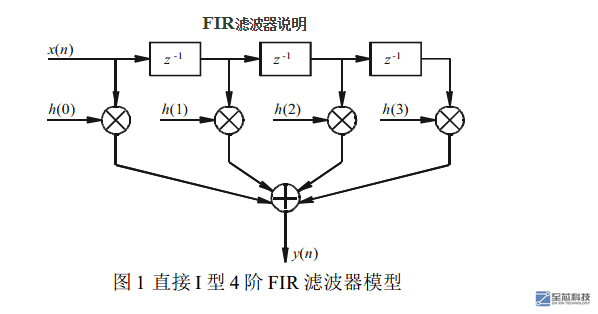

本文將簡單介紹FIR濾波器的原理,詳細介紹使用Verilog HDL設計并行FIR濾波器的流程和方法。接下來幾篇會介紹串行結構FIR的Verilog設計、使用Quartus和Vivado的IP核

2020-09-25 17:44:38

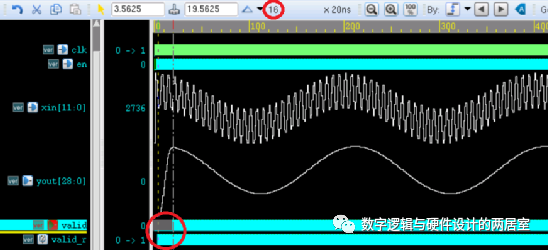

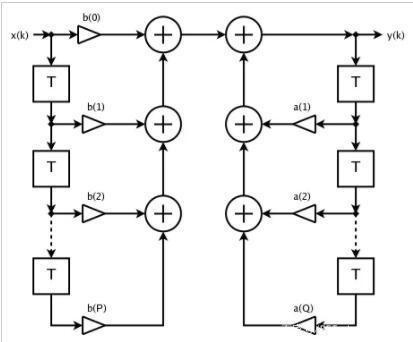

數字濾波器-IIR濾波器原理介紹&Verilog HDL設計

本文將簡單介紹另一種數字濾波器——IIR濾波器的原理,詳細介紹使用Verilog HDL設計直接型IIR濾波器的方法。數字濾波器數字濾波器從實現結構上劃分,有FIR和IIR兩種。FIR的特點是:線性

2020-09-27 09:22:58

X-HDL v3.2.55 VHDL/Verilog語言翻譯器

X-HDL:軟件簡介—SoftWare Description: X-HDL v3.2.55 VHDL/Verilog語言翻譯器

一款VHDL/Verilog語言翻譯器。可實現VHDL和Verilog語言的相互智能化轉化。這分別是windows、linux、solaris版本。

2006-03-25 12:00:47 357

357

357

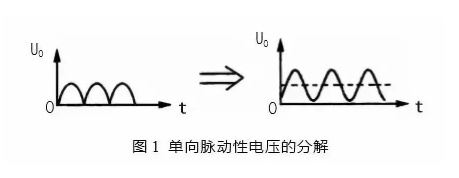

357基于Verilog-HDL的軸承振動噪聲電壓峰值檢測

介紹模擬峰值電壓的檢測方式,敘述基于Verilog-HDL 與高速A/D轉換器相結合所實現的數字式快速軸承噪聲檢測方法, 給出相關的Verilog-HDL 主模塊部分。

2009-04-16 10:53:02 22

22

22

22Verilog HDL綜合實用教程

Verilog HDL 綜合實用教程第1章 基礎知識第2章 從Verilog結構到邏輯門第3章 建模示例第4章 模型的優化第5章 驗證附錄A 可綜合的語言結構附錄B 通用庫

2009-07-20 11:21:13 86

86

86

86基于Verilog HDL語言的FPGA設計

采用 Verilog HDL 語言在Altera 公司的FPGA 芯片上實現了RISC_CPU 的關鍵部件狀態控制器的設計,以及在與其它各種數字邏輯設計方法的比較下,顯示出使用Verilog HDL語言的優越性.關鍵詞

2009-08-21 10:50:05 69

69

69

69Verilog-HDL實踐與應用系統設計

Verilog-HDL實踐與應用系統設計本書從實用的角度介紹了硬件描述語言Verilog-HDL。通過動手實踐,體驗Verilog-HDL的語法結構、功能等內涵。在前五章,以簡單的實例列舉了Verilog-HDL的用法;

2009-11-14 22:57:40 147

147

147

147Verilog hdl教程實例

Verilog hdl教程實例

【例 3.2】4 位計數器module count4(out,reset,clk);output[3:0] out;input reset,clk;reg[3:0

2010-02-09 09:41:01 54

54

54

54Verilog HDL華為入門教程

Verilog HDL 華為入門教程

本文主要介紹了Verilog HDL 語言的一些基本知識,目的是使初學者能夠迅速掌握HDL設計方法,初步了解并掌握Verilog HDL語言的基本要素,能

2010-02-11 08:35:38 141

141

141

141Verilog HDL入門教程(華為絕密資料)

Verilog HDL入門教程(華為絕密資料)

本文主要介紹了Verilog HDL 語言的一些基本知識,目的是使初學者能夠迅速掌握HDL設計方法,初步了解并掌握Verilog HDL語言的

2010-04-02 11:52:21 0

0

0

0什么是Verilog HDL?

什么是Verilog HDL?

Verilog HDL是一種硬件描述語言,用于從算法級、門級到開關級的多種抽象設計層次的數字系統建模。被建模的數字系統

2009-01-18 14:53:26 4541

4541

4541

4541

Verilog HDL語言在FPGA/CPLD開發中的應用

摘 要:通過設計實例詳細介紹了用Verilog HDL語言開發FPGA/CPLD的方法,并通過與其他各種輸入方式的比較,顯示出使用Verilog HDL語言的優越性。

2009-06-20 11:51:28 2331

2331

2331

2331

基于Verilog-HDL的軸承振動噪聲電壓峰值檢測

摘要:介紹模擬峰值電壓的檢測方式,敘述基于Verilog-HDL與高速A/D轉換器相結合所實現的數字式快速軸承噪聲檢測方法,給出相關的Verilog-HDL主模塊部分。

2009-06-20 15:14:00 1216

1216

1216

1216

Verilog HDL程序基本結構與程序入門

Verilog HDL程序基本結構與程序入門

Verilog HDL程序基本結構

Verilog HDL是一種用于數字邏輯電路設計的語言。用Verilog HDL描述的

2010-02-08 11:43:30 2564

2564

2564

2564Verilog HDL語言實現時序邏輯電路

Verilog HDL語言實現時序邏輯電路

在Verilog HDL語言中,時序邏輯電路使用always語句塊來實現。例如,實現一個帶有異步復位信號的D觸發器

2010-02-08 11:46:43 5099

5099

5099

5099VHDL和Verilog HDL語言對比

VHDL和Verilog HDL語言對比

Verilog HDL和VHDL都是用于邏輯設計的硬件描述語言,并且都已成為IEEE標準。VHDL是在1987年成為IEEE標準,Verilog HDL

2010-02-09 09:01:17 10864

10864

10864

10864濾波器,濾波器電路,濾波器原理

濾波器,濾波器電路,濾波器原理

一、概述

1.定義

凡是可以使信號中特定的頻率成分通過,而極大地衰減或抑制其他頻率成分的裝置或

2010-03-24 13:58:57 2774

2774

2774

2774光濾波器,什么是光濾波器

光濾波器,什么是光濾波器

基于干涉原理的濾波器:熔錐光纖濾波器、Fabry-Perot濾波器、多層介質膜濾波器、馬赫-曾德干涉濾波

2010-04-02 16:54:04 2482

2482

2482

2482Verilog HDL與VHDL及FPGA的比較分析

Verilog HDL與VHDL及FPGA的比較分析. Verilog HDL優點:類似C語言,上手容易,靈活。大小寫敏感。在寫激勵和建模方面有優勢。

2011-01-11 10:45:29 1580

1580

1580

1580Verilog HDL程序設計教程_王金明

《Verilog HDL 程序設計教程》對Verilog HDL程序設計作了系統全面的介紹,以可綜合的設計為重點,同時對仿真和模擬也作了深入的闡述。《Verilog HDL 程序設計教程》以Verilog-1995標準為基礎

2011-09-22 15:53:36 0

0

0

0基于Verilog HDL語言的CAN總線控制器設計及驗證

在此利用Verilog HDL設計了一款CAN總線控制器,首先根據協議把整個CAN總線控制器劃分為接口邏輯管理、寄存器邏輯和CAN核心模塊3個模塊,然后用Verilog HDL硬件描述語言設計了各個功能模塊

2012-07-31 14:25:24 8908

8908

8908

8908

Verilog_HDL的基本語法詳解(夏宇聞版)

Verilog_HDL的基本語法詳解(夏宇聞版):Verilog HDL是一種用于數字邏輯電路設計的語言。用Verilog HDL描述的電路設計就是該電路的Verilog HDL模型。Verilog HDL既是一種行為描述的語言也是一種結

2012-10-08 14:48:31 0

0

0

0基本組合邏輯功能雙向管腳的Verilog HDL源代碼

電子發燒友網核心提示: 本例程是Verilog HDL源代碼:關于基本組合邏輯功能中雙向管腳的功能實現源代碼。 Verilog HDL: Bidirectional Pin This example implements a clocked bidirectional pin in Verilog HDL.

2012-10-15 11:28:26 1808

1808

1808

1808Verilog HDL入門教程

本文主要介紹了Verilog HDL 語言的一些基本知識,目的是使初學者能夠迅速掌握HDL設計方法,初步了解并掌握Verilog HDL語言的基本要素,能夠讀懂簡單的設計代碼并能夠進行一些簡單設計的Verilog HDL建模。

2016-07-15 15:27:00 0

0

0

0設計與驗證:Verilog HDL(清晰PDF)

設計與驗證,很不錯的一本書,《設計與驗證》以實例講解的方式對HDL語言的設計方法進行介紹。全書共分9章,第1章至第3章主要介紹了Verilog HDL語言的基本概念、設計流程、語法及建模方式等內容

2016-10-10 17:04:40 613

613

613

613詳細解析濾波器的定義,濾波器的特性,濾波器的工作原理,濾波器的分類,濾波器的典型電路原理圖

濾波器的基礎是諧振電路,只要能構成諧振電路組合就可實現濾波器。濾波器有4種基本原型,即低通濾波器、帶通濾波器、帶阻濾波器和高通濾波器。實現濾波器就是實現相應的諧振系統。電感、電容形成的濾波器,稱為集總參數濾波器;各種射頻/微波傳輸線形成的諧振器,稱為分布參數濾波器。理論上,濾波器是無耗組件。

2017-05-03 16:20:54 20627

20627

20627

20627

Verilog HDL入門教程之Verilog HDL數字系統設計教程

本文檔的主要內容詳細介紹的是Verilog HDL入門教程之Verilog HDL數字系統設計教程。

2018-09-20 15:51:26 86

86

86

86Verilog HDL入門教程

本文主要介紹了Verilog HDL 語言的一些基本知識,目的是使初學者能夠迅速掌握HDL 設計方法,初步了解并掌握Verilog HDL語言的基本要素,能夠讀懂簡單的設計代碼并能夠進行一些簡單設計的Verilog HDL建模。

2019-02-11 08:00:00 102

102

102

102Verilog-HDL深入講解

Verilog HDL是一種硬件描述語言,以文本形式來描述數字系統硬件的結構和行為的語言,用它可以表示邏輯電路圖、邏輯表達式,還可以表示數字邏輯系統所完成的邏輯功能。 Verilog HDL和VHDL是世界上最流行的兩種硬件描述語言,都是在20世紀80年代中期開發出來的。

2019-11-13 07:03:00 3870

3870

3870

3870Verilog HDL的基礎知識詳細說明

硬件描述語言基本語法和實踐

(1)VHDL 和Verilog HDL的各自特點和應用范圍

(2)Verilog HDL基本結構語言要素與語法規則

(3) Verilog HDL組合邏輯語句結構

2019-07-03 17:36:00 54

54

54

54Verilog HDL語言技術要點

的是硬件描述語言。最為流行的硬件描述語言有兩種Verilog HDL/VHDL,均為IEEE標準。Verilog HDL具有C語言基礎就很容易上手,而VHDL語言則需要Ada編程基礎。另外Verilog

2020-09-01 11:47:09 5063

5063

5063

5063

Verilog教程之Verilog HDL程序設計語句和描述方式

本文檔的主要內容詳細介紹的是Verilog教程之Verilog HDL程序設計語句和描述方式。

2020-12-09 11:24:23 53

53

53

53如何使用Verilog HDL描述可綜合電路?

1、如何使用Verilog HDL描述可綜合電路 Verilog 有什么奇技淫巧?我想最重要的是理解其硬件特性。Verilog HDL語言僅是對已知硬件電路的文本描述。所以編寫前: 對所需實現的硬件

2021-04-04 11:19:00 4854

4854

4854

4854

如何用matlab生成一個可編程FIR濾波器的硬件HDL代碼?

01 概述 本文通過matlab自帶的工具箱生成一個可編程FIR濾波器的硬件HDL代碼,可生成VHDL或者Verilog HDL兩種類型的代碼。 02 具體操作步驟 新建一個matlab的腳本,鍵入

2021-05-03 09:37:00 4624

4624

4624

4624

Verilog HDL verilog hdl和vhdl的區別

Verilog HDL是一種以文本形式描述數字系統硬件的結構和行為的硬件描述語言,也可描述邏輯電路圖、邏輯表達式等。Verilog HDL和VHDL是目前主流的、最受歡迎的兩種硬件描述語言。

2021-07-23 14:36:55 11931

11931

11931

11931這是一個用verilog寫的DC濾波器.

這是一個用verilog寫的DC濾波器.(通訊電源技術的組成)-這是一個用verilog寫的DC濾波器.適合新手學習參考

2021-09-16 11:41:13 10

10

10

10Verilog HDL 編譯器指令說明

Verilog HDL 編譯器指令 復雜一點的系統在進行設計或者驗證時,都會用到一些編譯器指令,那么什么是編譯器指令? ? Verilog HDL編譯器指令由重音符(‘)開始。在Verilog 語言

2021-11-03 09:31:56 4784

4784

4784

4784

Verilog HDL指定用戶定義原語UDP的能力

在前一章中,我們介紹了Verilog HDL提供的內置基本門。本章講述Verilog HDL指定用戶定義原語U D P的能力。

2022-08-08 11:46:46 1616

1616

1616

1616濾波器的種類與濾波原理

濾波器的種類包括低通濾波器、高通濾波器、帶通濾波器、帶阻濾波器等。低通濾波器可以抑制信號中的高頻成分,使信號更加平滑;高通濾波器可以抑制信號中的低頻成分,使信號更加清晰;帶通濾波器可以抑制信號中的高頻和低頻成分,使信號更加精確;

2023-02-17 15:23:10 4946

4946

4946

4946

濾波器的構成 濾波器的特點

濾波器網絡:濾波器網絡是濾波器的核心部分,它由各種不同的電路元件(如電容、電感、電阻等)組成,用于選擇性地通過或者抑制特定頻率的信號。根據不同的濾波器類型,濾波器網絡可以采用不同的電路結構,例如,低通濾波器采用電容-電感結構,高通濾波器采用電感-電容結構,帶通濾波器采用多級串聯或并聯的電容-電感結構等。

2023-02-24 11:16:14 5350

5350

5350

5350Verilog并行FIR濾波器設計

FIR(Finite Impulse Response)濾波器是一種有限長單位沖激響應濾波器,又稱為非遞歸型濾波器。FIR 濾波器具有嚴格的線性相頻特性,同時其單位響應是有限長的,因而是穩定的系統,在數字通信、圖像處理等領域都有著廣泛的應用。

2023-03-27 11:33:53 1596

1596

1596

1596

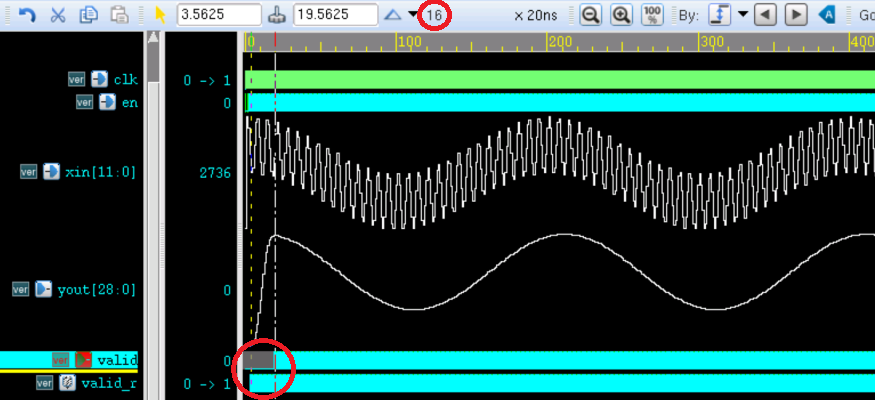

Verilog串行FIR濾波器設計

設計參數不變,與并行 FIR 濾波器參數一致。即,輸入頻率為 7.5 MHz 和 250 KHz 的正弦波混合信號,經過 FIR 濾波器后,高頻信號 7.5MHz 被濾除,只保留 250KMHz 的信號。

2023-03-27 11:36:46 1544

1544

1544

1544

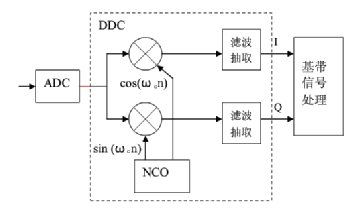

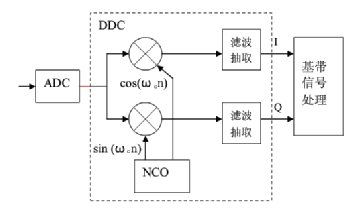

Verilog CIC濾波器設計

積分梳狀濾波器(CIC,Cascaded Integrator Comb),一般用于數字下變頻(DDC)和數字上變頻(DUC)系統。CIC 濾波器結構簡單,沒有乘法器,只有加法器、積分器和寄存器

2023-03-27 11:40:23 2360

2360

2360

2360

Verilog CIC濾波器設計

積分梳狀濾波器(CIC,Cascaded Integrator Comb),一般用于數字下變頻(DDC)和數字上變頻(DUC)系統。

2023-06-01 11:05:41 2232

2232

2232

2232

Verilog串行FIR濾波器設計

設計參數不變,與并行 FIR 濾波器參數一致。即,輸入頻率為 7.5 MHz 和 250 KHz 的正弦波混合信號,經過 FIR 濾波器后,高頻信號 7.5MHz 被濾除,只保留 250KMHz 的信號。

2023-06-01 11:08:38 1520

1520

1520

1520

二十進制編碼器及Verilog HDL描述 Verilog HDL程序的基本結構及特點

節通過硬件描述語言Verilog HDL對二十進制編碼器的描述,介紹Verilog HDL程序的基本結構及特點。

2023-08-28 09:54:34 5319

5319

5319

5319

高通濾波器、低通濾波器、帶通濾波器怎樣測幅頻特性?

高通濾波器、低通濾波器、帶通濾波器怎樣測幅頻特性? 高通濾波器、低通濾波器和帶通濾波器是常用的濾波器類型,它們在信號處理中起到了至關重要的作用。測量它們的幅頻特性是評估和理解這些濾波器性能的重要手段

2024-03-28 17:28:51 7913

7913

7913

7913emi濾波器是什么濾波器

EMI濾波器(Electromagnetic Interference Filter)是一種用于抑制電磁干擾(EMI)的濾波器。電磁干擾是指在電子設備中由于電磁波的傳播而產生的干擾信號,這些干擾信號

2024-08-25 15:59:50 3185

3185

3185

3185FPGA Verilog HDL語法之編譯預處理

Verilog HDL語言和C語言一樣也提供了編譯預處理的功能。“編譯預處理”是Verilog HDL編譯系統的一個組成部分。Verilog HDL語言允許在程序中使用幾種特殊的命令(它們不是一般

2025-03-27 13:30:31 1216

1216

1216

1216

電子發燒友App

電子發燒友App

評論