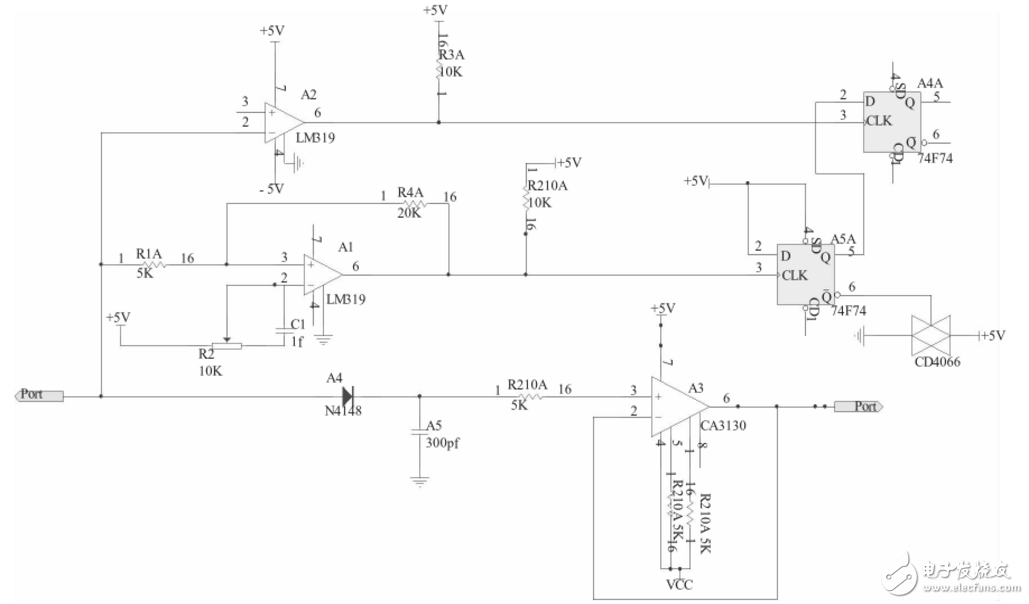

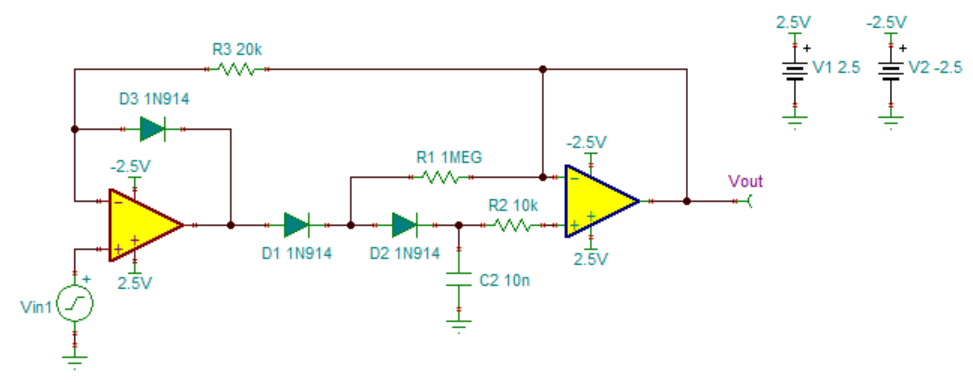

本文主要介紹了基于運放CA3140的峰值檢測電路的設計。本次電路的設計,可以較為精確的完成對峰值信號脈沖的檢測與保持,從而完成對脈沖幅度的測量,進而知道輻射的能量大小。主要解決了以下問題:由于此電路

2018-02-27 08:51:09 20315

20315

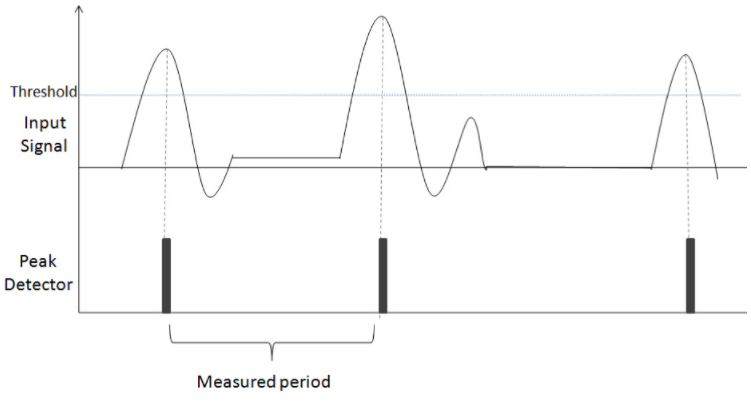

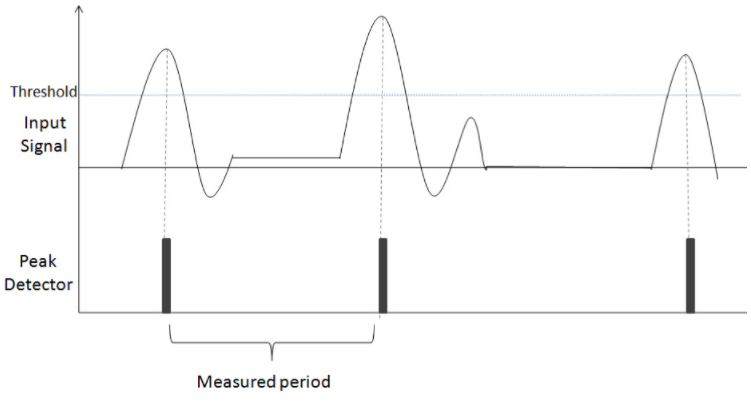

峰值檢測也是最大檢測的后續功能。峰值被定義為信號最大值,隨后是信號值的下降(數學上,信號的二階導數改變符號)。一些應用尋找全局絕對峰值,例如信號流中的單峰值信號。

2019-03-22 08:57:00 8104

8104

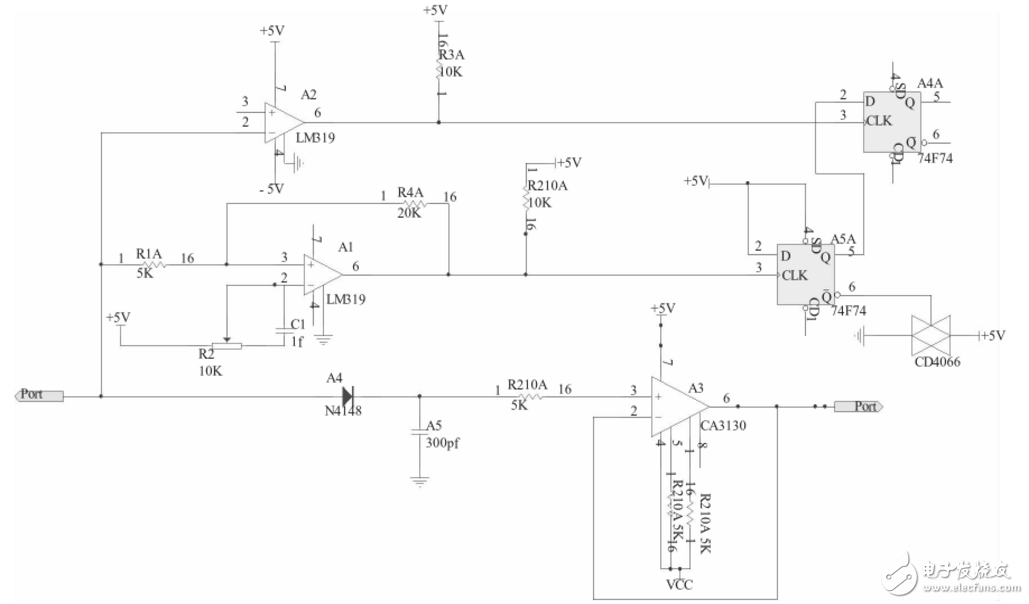

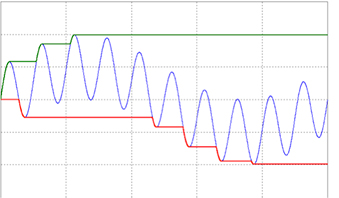

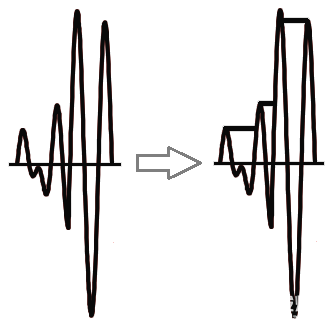

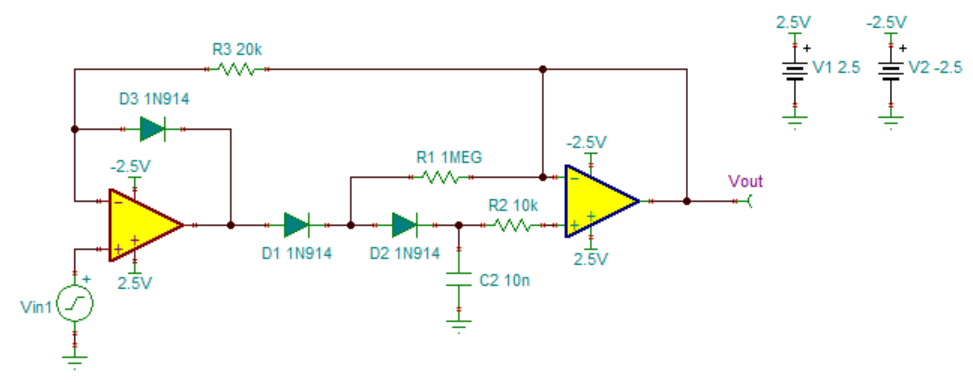

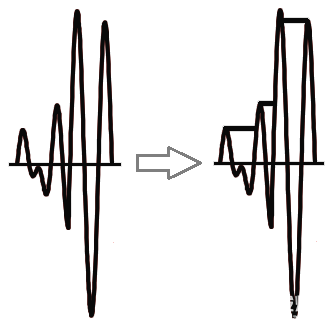

各位大俠,現在需要檢測保持一個幾十ns的脈沖峰值,峰值大概在10mV左右(如果太小可以增大到幾百mV),如下圖所示。目前看了使用比較器的高速峰值保持電路,請問使用該電路能達到10ns的峰值檢測保持嗎?器件該怎么選擇?或者有沒有使用峰值檢波IC或者其他的方案可以選擇?希望各位指教。

2016-11-01 19:47:06

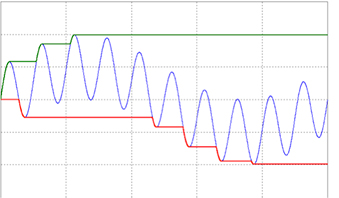

請教各位大神,這個峰值檢測電路有什么問題嗎,仿真之后輸出電壓為什么會下降?有什么解決辦法嗎?(信號源輸入的是30mV的正弦電壓,經op07放大100倍后送到LM393電壓比較器和LF398信號保持器,要求輸出電壓的峰峰值3V )

2016-09-20 21:40:45

峰值檢測電路圖集

2009-11-21 12:39:56

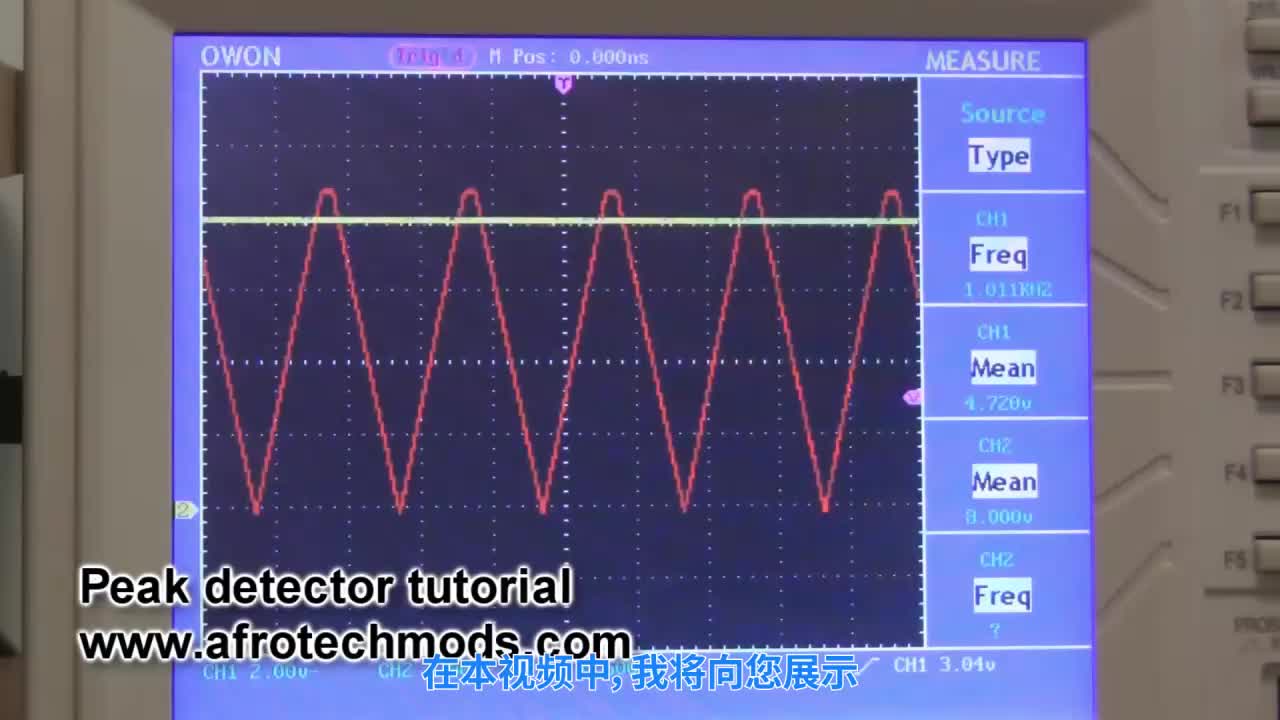

用LM358搭的峰值檢測電路,當輸入的交流信號的頻率在1KHz到5KHz的時候,輸出的值還算正常,但是當輸出的頻率在5KHz以上后,輸出的峰值差的就很多了,當頻率到幾十KHz,輸出就為0了,有什么辦法能夠在頻率高的時候,輸出的峰值誤差不大。或者有什么好的解決辦法?

2016-04-04 17:26:01

振動電機是如何和軸承配合的?振動電機應注意?振動電機在我們生活中越來越多的使用使用振動電機經常有疑問,在維修振動電機的時候經常發現振動電機的軸可以在軸承中間隨意左右竄動,因為在普通的電動機中這種現象

2015-12-28 18:26:34

用labview做了一段程序,用來檢測故障軸承,但是無法模擬故障軸承的振動加速度信號,因此也就無法驗證方法的正確性,求各位高手幫忙做個模擬的VI,謝謝了

2013-05-09 16:51:37

最近小弟在做峰值檢測的試驗,發現手頭上有的LM311的datasheet里面有峰值檢測電路圖,不知道它能檢測的波形頻率和幅度是多少,我的目標是達到10M左右,峰值在100mv以上。不知道貴公司給出的這個電路圖是否能滿足我的需要。

2024-09-12 06:19:03

OP07做峰峰值檢測,輸出直接飽和,用NE5532卻可以,這是為什么?求大神解答,電路圖如下

2024-08-14 08:29:54

請問OPA615是怎么用在峰值檢測上的,七腳控制腳應該輸入脈沖嗎?要檢測信號是不是從十腳輸入待檢測信號?輸出波形應該是什么樣的?真心求指教,謝謝

2024-08-16 14:40:07

TI有沒有專用的峰值檢測芯片????

2016-04-13 22:26:44

`滑動軸承,在滑動摩擦下工作的軸承,滑動軸承工作平穩、可靠、無噪聲。 按滑動軸承振動的機理大致有兩種形式: 第一種:同頻振動(即強迫振動),其激振力為軸系組件不平衡、不對中或安裝不良造成,與軸承

2017-09-01 11:56:41

如何用峰值檢測測量RF功率?如何測量高波峰因數信號的實際功率?

2021-04-12 06:15:53

峰值檢測器,可變衰減器和可變增益放大器。如果峰值檢測器檢測到的電壓高于閾值設置,則將包括衰減器。如果峰值檢測器檢測到的電壓低于閾值設置,則將包括放大器。我想知道這是用FPGA實現的嗎?如果是,是否有任何可用

2019-06-06 11:26:50

有什么好用的verilog HDL編輯工具可用?最好能集成實時的verilog HDL語法檢測、自定義模塊識別觸發等功能,最好能夠免費;

2024-04-28 11:00:46

請問如何去設計一種峰值檢測器?

2021-04-23 06:21:25

求一款能夠避免以往峰值檢測電路弊端的,并且可以在無需專用模/數轉換器的前提下實現了模擬到數字的轉換電路?

2021-04-12 06:05:50

設計一個峰值檢測電路,檢測幅值為10MV左右,頻率40mhz的正弦波小信號,求推薦一個峰值檢測電路模塊!!!

2019-07-25 04:37:21

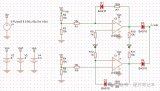

測溫電路、波形調制電路、峰值檢測電路原理這三個電路,沒看懂原理,哪個來說說,多交流一起進步!(悟性不好,正在用最笨的方法學習電路中!不喜勿噴,不要叨逼,請繞道)

2022-12-23 17:53:45

如題,采用負反饋來控制電路輸出幅值時,常用到峰值檢測電路將輸出電壓反饋給單片機,我想的是不通過峰值采樣而直接輸出給單片機可以嗎?這樣采集一個交流周期內的值也能確定輸出信號的具體信息

2018-08-09 10:08:06

高頻峰值檢測器電路圖

2019-10-18 01:29:39

Verilog HDL Synthesis (A Practical Primer)

2009-02-12 09:36:24 40

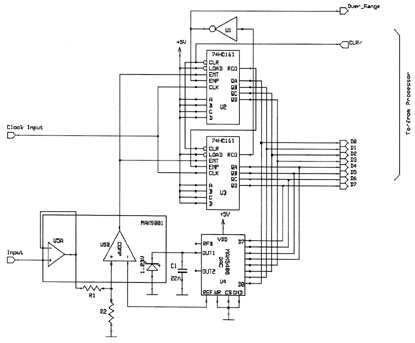

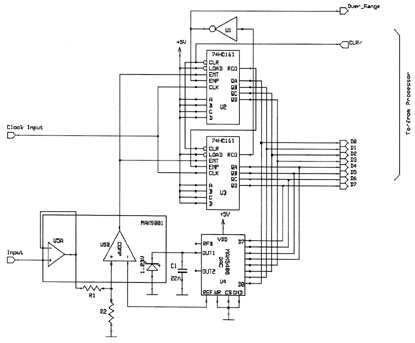

40 介紹模擬峰值電壓的檢測方式,敘述基于Verilog-HDL 與高速A/D轉換器相結合所實現的數字式快速軸承噪聲檢測方法, 給出相關的Verilog-HDL 主模塊部分。

2009-04-16 10:53:02 22

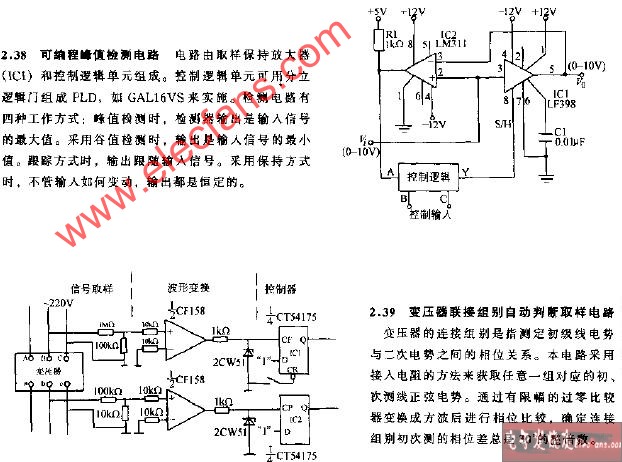

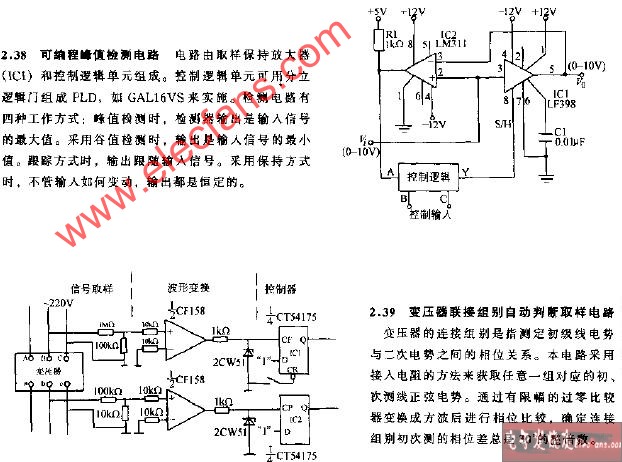

22 用四個器件設計極性可編程峰值檢測器的簡介:

2009-06-06 09:32:41 31

31 介紹模擬峰值電壓的檢測方式,敘述基于Verilpg-HDL與高速A/D轉換器相結合所實現的數字式快速軸承噪聲檢測方法,給出相關的Verilpg-HDL主模塊部分。

2009-07-18 10:30:06 14

14 Verilog HDL 綜合實用教程第1章 基礎知識第2章 從Verilog結構到邏輯門第3章 建模示例第4章 模型的優化第5章 驗證附錄A 可綜合的語言結構附錄B 通用庫

2009-07-20 11:21:13 86

86 采用 Verilog HDL 語言在Altera 公司的FPGA 芯片上實現了RISC_CPU 的關鍵部件狀態控制器的設計,以及在與其它各種數字邏輯設計方法的比較下,顯示出使用Verilog HDL語言的優越性.關鍵詞

2009-08-21 10:50:05 69

69 Verilog-HDL實踐與應用系統設計本書從實用的角度介紹了硬件描述語言Verilog-HDL。通過動手實踐,體驗Verilog-HDL的語法結構、功能等內涵。在前五章,以簡單的實例列舉了Verilog-HDL的用法;

2009-11-14 22:57:40 147

147 Verilog HDL 華為入門教程

本文主要介紹了Verilog HDL 語言的一些基本知識,目的是使初學者能夠迅速掌握HDL設計方法,初步了解并掌握Verilog HDL語言的基本要素,能

2010-02-11 08:35:38 141

141 Verilog HDL入門教程(華為絕密資料)

本文主要介紹了Verilog HDL 語言的一些基本知識,目的是使初學者能夠迅速掌握HDL設計方法,初步了解并掌握Verilog HDL語言的

2010-04-02 11:52:21 0

0 Verilog HDL練習題

2010-11-03 16:47:13 194

194 什么是Verilog HDL?

Verilog HDL是一種硬件描述語言,用于從算法級、門級到開關級的多種抽象設計層次的數字系統建模。被建模的數字系統

2009-01-18 14:53:26 4541

4541

峰值檢測器

圖1電路用于檢測模擬信號峰值,該電路避免了以往峰值檢測電路的弊端:有限的保持時間、檢測性能對保持電容參數極為敏感、需要輸入電阻極大的高

2009-02-08 11:14:07 2925

2925

可編程峰值檢測電路

2009-02-10 09:05:53 1398

1398

【摘 要】 介紹了一種基于Verilog-HDL描述的多功能步進電機控制芯片的可綜合方案,該方案可方便地構成兩相雙極或四相單極步進電機的控制系統。外接元件極少,只需給定時鐘

2009-05-16 19:12:41 2343

2343

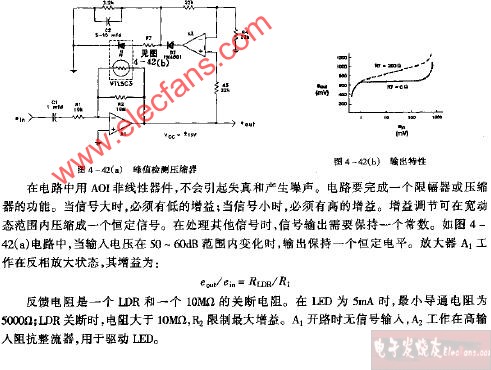

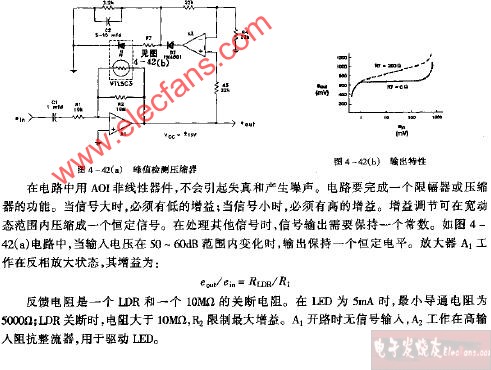

峰值檢測壓縮器電路圖

2009-06-30 09:55:13 752

752

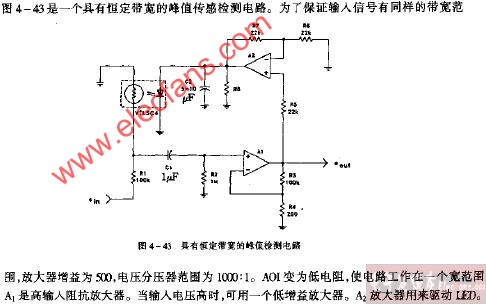

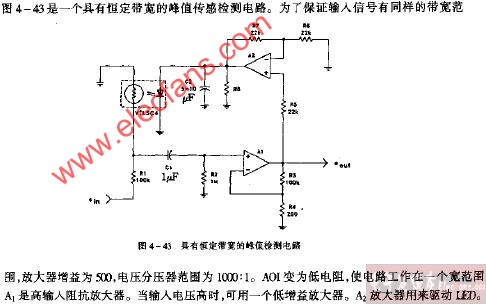

具有恒定帶寬的峰值檢測電路圖

2009-06-30 09:59:42 701

701

Verilog HDL程序基本結構與程序入門

Verilog HDL程序基本結構

Verilog HDL是一種用于數字邏輯電路設計的語言。用Verilog HDL描述的

2010-02-08 11:43:30 2564

2564 Verilog HDL語言簡介

1.什么是Verilog HDLVerilog HDL是硬件描述語言的一種,用于數

2010-02-09 08:59:33 4137

4137 VHDL和Verilog HDL語言對比

Verilog HDL和VHDL都是用于邏輯設計的硬件描述語言,并且都已成為IEEE標準。VHDL是在1987年成為IEEE標準,Verilog HDL

2010-02-09 09:01:17 10864

10864 Verilog HDL與VHDL及FPGA的比較分析. Verilog HDL優點:類似C語言,上手容易,靈活。大小寫敏感。在寫激勵和建模方面有優勢。

2011-01-11 10:45:29 1580

1580 峰值檢測電路(PKD,Peak Detector)的作用是對輸入信號的峰值進行提取,產生輸出Vo = Vpeak,為了實現這樣的目標,電路輸出值會一直保持,直到一個新的更大的峰值出現或電路復位。峰值檢

2011-05-13 16:00:36 199

199 《Verilog HDL 程序設計教程》對Verilog HDL程序設計作了系統全面的介紹,以可綜合的設計為重點,同時對仿真和模擬也作了深入的闡述。《Verilog HDL 程序設計教程》以Verilog-1995標準為基礎

2011-09-22 15:53:36 0

0 Verilog_HDL的基本語法詳解(夏宇聞版):Verilog HDL是一種用于數字邏輯電路設計的語言。用Verilog HDL描述的電路設計就是該電路的Verilog HDL模型。Verilog HDL既是一種行為描述的語言也是一種結

2012-10-08 14:48:31 0

0 電子發燒友網核心提示: 本例程是Verilog HDL源代碼:關于基本組合邏輯功能中雙向管腳的功能實現源代碼。 Verilog HDL: Bidirectional Pin This example implements a clocked bidirectional pin in Verilog HDL.

2012-10-15 11:28:26 1808

1808 Verilog HDL程序設計與實踐著重介紹了Verilog HDL語言

2015-10-29 14:45:47 21

21 Verilog HDL程序設計教程-人郵

2016-05-11 11:30:19 37

37 Verilog HDL實驗練習與語法手冊-高教

2016-05-11 11:30:19 0

0 Verilog_HDL教程,又需要的朋友下來看看

2016-05-11 17:30:15 0

0 Verilog+HDL實用教程-電科,下來看看。

2016-05-11 17:30:15 34

34 Verilog_HDL語言的學習,為FPGA編程打下堅實的基礎

2016-05-19 16:40:52 14

14 Verilog HDL 華為入門教程

2016-06-03 16:57:53 46

46 本文主要介紹了Verilog HDL 語言的一些基本知識,目的是使初學者能夠迅速掌握HDL設計方法,初步了解并掌握Verilog HDL語言的基本要素,能夠讀懂簡單的設計代碼并能夠進行一些簡單設計的Verilog HDL建模。

2016-07-15 15:27:00 0

0 EMI調試:是否需要準峰值檢測?_中文。

2016-09-01 14:52:09 13

13 設計與驗證,很不錯的一本書,《設計與驗證》以實例講解的方式對HDL語言的設計方法進行介紹。全書共分9章,第1章至第3章主要介紹了Verilog HDL語言的基本概念、設計流程、語法及建模方式等內容

2016-10-10 17:04:40 613

613 Verilog HDL設計(進階),感興趣的小伙伴們可以瞧一瞧。

2016-11-10 15:29:36 15

15 Verilog HDL設計(入門),感興趣的小伙伴們可以瞧一瞧。

2016-11-10 15:29:36 25

25 Verilog HDL設計(提高),感興趣的小伙伴們可以瞧一瞧。

2016-11-10 15:29:36 15

15 Verilog HDL虛擬器件和虛擬接口模型

2017-02-07 18:25:21 4

4 基于FPGA Verilog-HDL語言的串口設計

2017-02-16 00:08:59 35

35 本文檔的主要內容詳細介紹的是Verilog HDL入門教程之Verilog HDL數字系統設計教程。

2018-09-20 15:51:26 86

86 本文檔的主要內容詳細介紹的是常用模塊的Verilog HDL設計詳細資料免費下載。

2018-10-16 11:12:54 20

20 本文檔的主要內容詳細介紹的是如何使用Verilog-HDL做CPLD設計的時序邏輯電路的實現。

2018-12-12 16:25:46 11

11 本文主要介紹了Verilog HDL 語言的一些基本知識,目的是使初學者能夠迅速掌握HDL 設計方法,初步了解并掌握Verilog HDL語言的基本要素,能夠讀懂簡單的設計代碼并能夠進行一些簡單設計的Verilog HDL建模。

2019-02-11 08:00:00 102

102 Verilog HDL是一種硬件描述語言,以文本形式來描述數字系統硬件的結構和行為的語言,用它可以表示邏輯電路圖、邏輯表達式,還可以表示數字邏輯系統所完成的邏輯功能。 Verilog HDL和VHDL是世界上最流行的兩種硬件描述語言,都是在20世紀80年代中期開發出來的。

2019-11-13 07:03:00 3870

3870 硬件描述語言基本語法和實踐

(1)VHDL 和Verilog HDL的各自特點和應用范圍

(2)Verilog HDL基本結構語言要素與語法規則

(3) Verilog HDL組合邏輯語句結構

2019-07-03 17:36:00 54

54 的是硬件描述語言。最為流行的硬件描述語言有兩種Verilog HDL/VHDL,均為IEEE標準。Verilog HDL具有C語言基礎就很容易上手,而VHDL語言則需要Ada編程基礎。另外Verilog

2020-09-01 11:47:09 5063

5063

本文檔的主要內容詳細介紹的是Verilog教程之Verilog HDL程序設計語句和描述方式。

2020-12-09 11:24:23 53

53 PKD01:帶復位保持模式的單片峰值檢測器過時數據表

2021-04-22 18:59:59 6

6 PKD01:帶復位保持模式的單片峰值檢測器數據表

2021-04-27 12:59:43 8

8 DN61-峰值檢測器提高速度和性能

2021-04-30 16:57:41 9

9 簡單介紹Verilog HDL語言和仿真工具。

2021-05-06 16:17:10 619

619 LTC6244演示電路-60 kHz正負峰值檢測器

2021-06-01 10:46:15 11

11 Verilog HDL是一種以文本形式描述數字系統硬件的結構和行為的硬件描述語言,也可描述邏輯電路圖、邏輯表達式等。Verilog HDL和VHDL是目前主流的、最受歡迎的兩種硬件描述語言。

2021-07-23 14:36:55 11931

11931 Verilog HDL入門教程.pdf

2021-11-02 16:27:14 120

120 Verilog HDL入門教程-Verilog HDL的基本語法

2022-01-07 09:23:42 189

189 本文概述了如何構建峰值檢測電路,其中包括一個基于輸入信號峰峰值時間計算的頻率監控電路。該 IC 展示了集成多種功能的高效率,因為該項目需要這樣的功能。

2022-06-20 15:20:08 9033

9033

對于基本的峰值檢測器電路,我們甚至不需要任何復雜的電子元件。可以使用二極管和電容器構建簡單的峰值檢測器電路。

2022-09-23 15:38:53 6315

6315

峰值檢測電路(Peak Detection Circuit)是一種用于測量信號中最大值(正峰值)或最小值(負峰值)的電子電路。這種電路在很多領域都有廣泛的應用,以下是峰值檢測電路的一些典型使用場景。

2023-06-06 17:22:32 5523

5523

峰值檢測電路(Peak Detection Circuit)是一種用于測量信號中最大值(正峰值)或最小值(負峰值)的電子電路。

2023-06-13 14:52:02 9725

9725

節通過硬件描述語言Verilog HDL對二十進制編碼器的描述,介紹Verilog HDL程序的基本結構及特點。

2023-08-28 09:54:34 5319

5319

峰值檢測電路在AGC(自動增益控制)電路和傳感器最值求取電路中廣泛應用,自己平時一般作為程控增益放大器倍數選擇的判斷依據。

2024-04-19 10:59:25 1359

1359

和可靠性。 引言 在討論峰值檢測電路的穩定性問題之前,我們需要了解峰值檢測電路的基本原理和常見類型。峰值檢測電路通常包括一個比較器、一個觸發器和一個存儲元件(如電容)。當輸入信號超過存儲元件的電壓時,觸發器會翻轉

2024-10-10 15:20:08 1688

1688 、音頻設備、無線通信、模擬量測量以及電源監測等多個領域有著廣泛的應用。峰值檢測電路的核心功能是及時發現被檢測波形的峰值,并輸出一個與該峰值相等的直流電壓或電流信號,或者是一個瞬時的電壓脈沖,以便于后續電路的處理、存儲或顯示。

2024-10-10 16:10:13 5432

5432 本文繼續介紹Verilog HDL基礎知識,重點介紹賦值語句、阻塞與非阻塞、循環語句、同步與異步、函數與任務語法知識。

2024-10-24 15:00:35 1792

1792

電子發燒友App

電子發燒友App

評論