在數(shù)字電路中,凡是任一時刻的穩(wěn)定輸出不僅決定于該時刻的輸入,而且還和電路原來狀態(tài)有關(guān)者都叫時序邏輯電路。時序邏輯電路結(jié)構(gòu)示意圖如圖2-41所示。時序邏輯電路的狀態(tài)是靠具有存儲功能的觸發(fā)器所組成的存儲電路來記憶和表征的。

2018-01-31 09:27:23 59632

59632

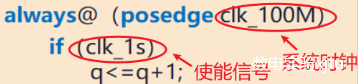

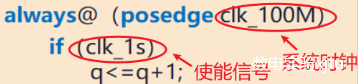

了解嗎? (1)純組合邏輯電路的缺點(diǎn)在哪? (3)純組合邏輯電路完成不了什么功能? (2)為什么需要時鐘和寄存器呢? 帶著這三個疑問我們來認(rèn)識一下時序邏輯電路。 二. 同步時序邏輯電路的作用 1. 時序邏輯電路對于組合邏輯的毛刺具有容忍度,

2020-12-25 14:39:28 6509

6509

時序邏輯電路的精華——計(jì)數(shù)器

2022-12-29 09:23:56 1850

1850 時序邏輯電路的特點(diǎn)是輸出信號不僅與電路的輸入有關(guān),還與電路原來的狀態(tài)有關(guān)。

2023-09-17 16:22:32 4390

4390

嵌入式開發(fā)Verilog教程(二)——Verilog HDL設(shè)計(jì)方法概述前言一、Verilog HDL語言簡介1.1 Verilog HDL語言是什么1.2前言在數(shù)字邏輯設(shè)計(jì)領(lǐng)域,迫切需要一種共同

2021-11-08 09:30:31

Verilog HDL是一種用于數(shù)字邏輯電路設(shè)計(jì)的語言。用Verilog HDL描述的電路設(shè)計(jì)就是該電路的Verilog HDL模型。Verilog HDL既是一種行為描述的語言也是一種結(jié)構(gòu)描述

2019-09-06 09:14:16

時序邏輯電路的特點(diǎn)

2019-10-08 05:34:53

時序邏輯電路的設(shè)計(jì)實(shí)驗(yàn)1 進(jìn)一步強(qiáng)化EDA仿真軟件的使用;2 掌握利用MSI

2009-03-19 15:10:18

微型電子元件,在極小的空間內(nèi)實(shí)現(xiàn)了復(fù)雜的邏輯功能。邏輯電路芯片根據(jù)設(shè)計(jì)不同,可以分為組合邏輯電路和時序邏輯電路兩大類。

邏輯電路芯片的應(yīng)用幾乎涵蓋了所有電子設(shè)備,包括但不限于:

計(jì)算機(jī)硬件:CPU

2024-09-30 10:47:47

12.Verilog HDL語言實(shí)現(xiàn)時序邏輯電路第三階段雖然利用第二階段課程學(xué)到的HDL基本語法可以完成大部分的FPGA功能,但相對復(fù)雜的FPGA系統(tǒng)設(shè)計(jì)中,如果能夠合理的應(yīng)用Verilog HDL

2014-11-30 17:38:06

常用語句11.Verilog HDL語言實(shí)現(xiàn)組合邏輯電路12.Verilog HDL語言實(shí)現(xiàn)時序邏輯電路第三階段雖然利用第二階段課程學(xué)到的HDL基本語法可以完成大部分的FPGA功能,但相對復(fù)雜的FPGA

2014-12-12 09:38:19

邏輯電路 3.8 Verilog HDL語言實(shí)現(xiàn)時序邏輯電路 3.9 Verilog HDL語言與C語言的區(qū)別與聯(lián)系 3.10 Verilog HDL程序設(shè)計(jì)經(jīng)驗(yàn) 3.11 典型實(shí)例3:數(shù)字跑表

2012-02-09 15:45:32

fpga時序邏輯電路的分析和設(shè)計(jì) 時序邏輯電路的結(jié)構(gòu)及特點(diǎn)時序邏輯電路——任何一個時刻的輸出狀態(tài)不僅取決于當(dāng)時的輸入信號,還與電路的原狀態(tài)有關(guān)。[hide][/hide]

2012-06-20 11:18:44

為什么FPGA可以用來實(shí)現(xiàn)組合邏輯電路和時序邏輯電路呢?

2023-04-23 11:53:26

應(yīng)用10.Verilog HDL語言的其他常用語句11.Verilog HDL語言實(shí)現(xiàn)組合邏輯電路12.Verilog HDL語言實(shí)現(xiàn)時序邏輯電路第三階段雖然利用第二階段課程學(xué)到的HDL基本語法可以完成大部分的FPGA

2012-06-13 17:43:58

句11.Verilog HDL語言實(shí)現(xiàn)組合邏輯電路12.Verilog HDL語言實(shí)現(xiàn)時序邏輯電路第三階段 雖然利用第二階段課程學(xué)到的HDL基本語法可以完成大部分的FPGA功能,但相對復(fù)雜的FPGA系統(tǒng)設(shè)計(jì)中

2018-09-19 11:34:03

句11.Verilog HDL語言實(shí)現(xiàn)組合邏輯電路12.Verilog HDL語言實(shí)現(xiàn)時序邏輯電路發(fā)燒友FPGA技術(shù)實(shí)訓(xùn),深圳-廣州-鄭州-長沙-南寧均有分點(diǎn),詳情聯(lián)系郭老師qq754634522 電話

2015-10-27 17:57:38

涉及時序邏輯電路的實(shí)例,希望能夠幫助大家理解在FPGA中實(shí)現(xiàn)時序邏輯電路。與組合邏輯電路相比,時序邏輯電路需要時鐘的參與,電路中會有存儲器件的參與,時序邏輯電路的輸出不僅取決于這一時刻的輸入,也受此

2022-07-22 15:25:03

Verilog程序模塊的結(jié)構(gòu)是由哪些部分組成的?如何去實(shí)現(xiàn)時序邏輯電路和組合邏輯電路的設(shè)計(jì)呢?

2021-11-03 06:35:57

各位大神求救啊用verilog語言實(shí)現(xiàn)電子鐘

2014-05-04 16:37:51

組合邏輯電路的基本模塊是什么?時序邏輯電路怎樣進(jìn)行工作的?

2021-09-18 09:19:42

1 進(jìn)一步強(qiáng)化EDA仿真軟件的使用;2 掌握利用MSI、可編程器件設(shè)計(jì)時序邏輯電路的特點(diǎn)、方法;3 掌握時序邏輯電路的調(diào)試方法;4&

2009-03-18 20:06:31 48

48 時序邏輯電路的輸出不但和當(dāng)前輸入有關(guān),還與系統(tǒng)的原先狀態(tài)有關(guān),即時序電路的當(dāng)前輸出由輸入變量與電路原先的狀態(tài)共同決定。為達(dá)到這一目的,時序邏輯電路從某一狀態(tài)

2009-03-18 22:13:04 71

71 采用 Verilog HDL 語言在Altera 公司的FPGA 芯片上實(shí)現(xiàn)了RISC_CPU 的關(guān)鍵部件狀態(tài)控制器的設(shè)計(jì),以及在與其它各種數(shù)字邏輯設(shè)計(jì)方法的比較下,顯示出使用Verilog HDL語言的優(yōu)越性.關(guān)鍵詞

2009-08-21 10:50:05 69

69 同步時序邏輯電路:本章系統(tǒng)的講授同步時序邏輯電路的工作原理、分析方法和設(shè)計(jì)方法。從同步時序邏輯電路模型與描述方法開始,介紹同步時序邏輯電路的分析步驟和方法。然后

2009-09-01 09:06:27 0

0 異步時序邏輯電路:本章主要從同步時序邏輯電路與異步時序邏輯電路狀態(tài)改變方式不同的特殊性出發(fā), 系統(tǒng)的介紹異步時序邏輯電路的電路結(jié)構(gòu)、工作原理、分析方法和設(shè)計(jì)方法。

2009-09-01 09:12:34 0

0 組合邏輯電路的特點(diǎn)是:在任意時刻,電路產(chǎn)生的穩(wěn)定輸出僅與當(dāng)前時刻的輸入有關(guān)。時序邏輯電路則與它不同,其特點(diǎn)是:在任意時刻電路產(chǎn)生的穩(wěn)定輸出不僅與當(dāng)前時刻的輸入

2010-05-30 09:46:59 44

44 數(shù)字邏輯電路按邏輯功能和電路組成的特點(diǎn)可分為組合邏輯電路和時序邏輯電路兩大類。

2010-08-10 11:51:58 39

39 數(shù)字邏輯電路可分為組合邏輯電路和時序邏輯電路兩大類。組合邏輯電路在任一時刻的穩(wěn)定輸出只取決于當(dāng)前的輸入,而與過去的輸入無關(guān)。在結(jié)構(gòu)上,組合邏輯電路僅由若干邏

2010-08-12 15:54:42 0

0 數(shù)字電路分為組合邏輯電路(簡稱組合電路)和時序邏輯電路(簡稱時序電路)兩類。在第三章中討論的電路為組合電路。組合電路的結(jié)構(gòu)模型如圖4.1所示,它的輸出函數(shù)表達(dá)式為

2010-08-13 15:23:02 24

24 在討論時序邏輯電路的分析與設(shè)計(jì)之前,讓我們先回顧一下在第四章中介紹過的時序電路結(jié)構(gòu)框圖和一些相關(guān)術(shù)語。時序電路的結(jié)構(gòu)框圖如圖5.1所示.。

2010-08-13 15:24:35 69

69 數(shù)字集成電路,根據(jù)原理可分為兩大類,既組合邏輯電路和時序邏輯電路。

組合邏輯電路的組成是邏輯門電路。電路的輸出狀態(tài)僅由同一時刻的輸入狀態(tài)決定,與電路的原

2010-08-18 15:05:23 55

55 實(shí)驗(yàn)十六 時序邏輯電路? 實(shí)驗(yàn)(1) 計(jì)數(shù)器?一、實(shí)驗(yàn)?zāi)康?⒈ 熟悉計(jì)數(shù)器的設(shè)計(jì)方法及工作原理。?⒉ 了解同步計(jì)數(shù)器與異步計(jì)數(shù)器的區(qū)別。?⒊ 應(yīng)用

2008-09-24 22:17:08 3571

3571

時序邏輯電路的分析方法

1. 時序邏輯電路的特點(diǎn) 在時序邏輯電路中,任意時刻的輸出信號不僅取決于當(dāng)時的輸入信

2009-04-07 23:18:11 9154

9154

時序邏輯電路分析實(shí)例

例1 分析圖所示電路的邏輯功能。設(shè)起始狀態(tài)是

2009-04-07 23:20:25 4935

4935

時序邏輯電路的特點(diǎn)

在第三章所討論的組合邏輯電路中,任一時刻的輸出信號僅僅取決于該時刻的輸入信號,而與電路原來

2009-09-30 18:19:22 10881

10881

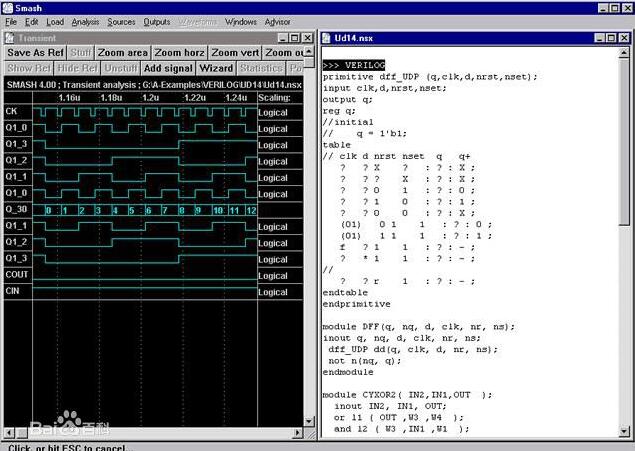

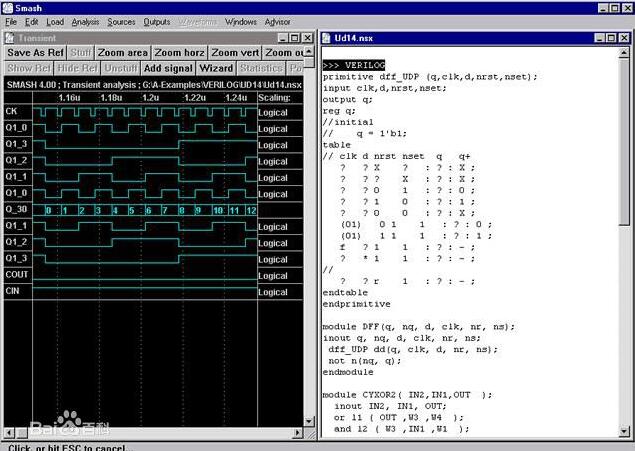

Verilog HDL程序基本結(jié)構(gòu)與程序入門

Verilog HDL程序基本結(jié)構(gòu)

Verilog HDL是一種用于數(shù)字邏輯電路設(shè)計(jì)的語言。用Verilog HDL描述的

2010-02-08 11:43:30 2564

2564 Verilog HDL語言簡介

1.什么是Verilog HDLVerilog HDL是硬件描述語言的一種,用于數(shù)

2010-02-09 08:59:33 4137

4137 VHDL和Verilog HDL語言對比

Verilog HDL和VHDL都是用于邏輯設(shè)計(jì)的硬件描述語言,并且都已成為IEEE標(biāo)準(zhǔn)。VHDL是在1987年成為IEEE標(biāo)準(zhǔn),Verilog HDL

2010-02-09 09:01:17 10864

10864 時序邏輯電路實(shí)例解析

一、觸發(fā)器 1、電位觸發(fā)方式觸發(fā)器

2010-04-15 13:46:25 6161

6161 Verilog_HDL的基本語法詳解(夏宇聞版):Verilog HDL是一種用于數(shù)字邏輯電路設(shè)計(jì)的語言。用Verilog HDL描述的電路設(shè)計(jì)就是該電路的Verilog HDL模型。Verilog HDL既是一種行為描述的語言也是一種結(jié)

2012-10-08 14:48:31 0

0 主要講了時序邏輯電路的相關(guān)知識,能夠方便大家學(xué)習(xí)使用

2016-02-29 14:25:53 0

0 電子專業(yè)單片機(jī)相關(guān)知識學(xué)習(xí)教材資料之時序邏輯電路的分析與設(shè)計(jì)

2016-09-02 14:30:26 0

0 數(shù)字電子技術(shù)--時序邏輯電路

2016-12-12 22:07:22 0

0 數(shù)字電子技術(shù)-- 時序邏輯電路

2016-12-12 21:54:28 0

0 Verilog HDL是一種硬件描述語言(HDL:Hardware Discription Language),Verilog HDL語言是一種以文本形式來描述數(shù)字系統(tǒng)硬件的結(jié)構(gòu)和行為的語言,用它可以表示邏輯電路圖、邏輯表達(dá)式,還可以表示數(shù)字邏輯系統(tǒng)所完成的邏輯功能。

2017-02-11 14:00:20 36720

36720

Verilog HDL是一種硬件描述語言,以文本形式來描述數(shù)字系統(tǒng)硬件的結(jié)構(gòu)和行為的語言,用它可以表示邏輯電路圖、邏輯表達(dá)式,還可以表示數(shù)字邏輯系統(tǒng)所完成的邏輯功能。而C語言是一門通用計(jì)算機(jī)編程語言,應(yīng)用廣泛。

2017-12-08 16:43:30 12969

12969 時序邏輯電路其任一時刻的輸出不僅取決于該時刻的輸入,而且還與過去各時刻的輸入有關(guān)。常見的時序邏輯電路有觸發(fā)器、計(jì)數(shù)器、寄存器等。由于時序邏輯電路具有存儲或記憶的功能,檢修起來就比較復(fù)雜。

2018-04-09 16:00:00 6913

6913

組合邏輯電路和時序邏輯電路都是數(shù)字電路,組合邏輯電路在邏輯功能上的特點(diǎn)是任意時刻的輸出僅僅取決于該時刻的輸入,與電路原來的狀態(tài)無關(guān)。而時序邏輯電路在邏輯功能上的特點(diǎn)是任意時刻的輸出不僅取決于當(dāng)時的輸入信號,而且還取決于電路原來的狀態(tài),或者說,還與以前的輸入有關(guān)。

2018-01-30 17:26:04 94951

94951

分析時序邏輯電路也就是找出該時序邏輯電路的邏輯功能,即找出時序邏輯電路的狀態(tài)和輸出變量在輸入變量和時鐘信號作用下的變化規(guī)律。上面講過的時序邏輯電路的驅(qū)動方程、狀態(tài)方程和輸出方程就全面地描述了時序邏輯電路的邏輯功能。

2018-01-30 18:55:32 128321

128321

本文開始介紹了時序邏輯電路的特點(diǎn)和時序邏輯電路的三種邏輯器件,其次介紹了時序邏輯電路的組成與時序邏輯電路檢修方法,最后介紹了時序邏輯電路的應(yīng)用舉例。

2018-03-01 10:53:38 112182

112182

Verilog HDL是一種硬件描述語言(HDL:Hardware Description Language),以文本形式來描述數(shù)字系統(tǒng)硬件的結(jié)構(gòu)和行為的語言,用它可以表示邏輯電路圖、邏輯表達(dá)式,還可以表示數(shù)字邏輯系統(tǒng)所完成的邏輯功能。

2018-03-23 11:46:04 96388

96388

本文檔的主要內(nèi)容詳細(xì)介紹的是數(shù)字電路基礎(chǔ)教程之時序邏輯電路的詳細(xì)資料概述。內(nèi)容包括了:1.時序邏輯電路分析2.若干常用時序邏輯電路3.時序邏輯電路設(shè)計(jì)

2018-10-17 08:00:00 0

0 本文檔的主要內(nèi)容詳細(xì)介紹的是如何使用Verilog-HDL做CPLD設(shè)計(jì)的時序邏輯電路的實(shí)現(xiàn)。

2018-12-12 16:25:46 11

11 本文檔的主要內(nèi)容詳細(xì)介紹的是數(shù)字電路教程之時序邏輯電路課件的詳細(xì)資料免費(fèi)下載主要內(nèi)容包括了:一 概述,二 時序邏輯電路的分析方法,三 若干常用的時序邏輯電路,四 時序邏輯電路的設(shè)計(jì)方法,五 時序邏輯電路中的競爭冒險(xiǎn)現(xiàn)象

2018-12-28 08:00:00 12

12 數(shù)字電路根據(jù)邏輯功能的不同特點(diǎn),可以分成兩大類,一類叫組合邏輯電路(簡稱組合電路),另一類叫做時序邏輯電路(簡稱時序電路)。組合邏輯電路在邏輯功能上的特點(diǎn)是任意時刻的輸出僅僅取決于該時刻的輸入

2019-02-26 15:22:20 32851

32851 時序邏輯電路是由組合邏輯電路與記憶電路(又稱存儲電路) 組合而成的。 常見時序邏輯電路有觸發(fā)器、 寄存器和計(jì)數(shù)器等。

2019-02-26 15:25:01 52418

52418 組合邏輯電路是任意時刻的輸出僅僅取決于該時刻的輸入,與電路原來的狀態(tài)無關(guān)。而時序邏輯電路不僅僅取決于當(dāng)前的輸入信號,而且還取決于電路原來的狀態(tài),或者說,還與以前的輸入有關(guān)。

2019-02-26 15:32:30 67228

67228 數(shù)字電路根據(jù)邏輯功能的不同特點(diǎn),可以分成兩大類,一類叫組合邏輯電路(簡稱組合電路),另一類叫做時序邏輯電路(簡稱時序電路)。組合邏輯電路在邏輯功能上的特點(diǎn)是任意時刻的輸出僅僅取決于該時刻的輸入

2019-05-16 18:32:37 8978

8978

中國大學(xué)MOOC

本課程以目前流行的Xilinx 7系列FPGA的開發(fā)為主線,全面講解FPGA的原理及電路設(shè)計(jì)、Verilog HDL語言及VIVADO的應(yīng)用,并循序漸進(jìn)地從組合邏輯、時序邏輯的開發(fā)開始,深入到FPGA的基礎(chǔ)應(yīng)用、綜合應(yīng)用和進(jìn)階應(yīng)用。

2019-08-06 06:12:00 4201

4201

本課程以目前流行的Xilinx 7系列FPGA的開發(fā)為主線,全面講解FPGA的原理及電路設(shè)計(jì)、Verilog HDL語言及VIVADO的應(yīng)用,并循序漸進(jìn)地從組合邏輯、時序邏輯的開發(fā)開始,深入到FPGA的基礎(chǔ)應(yīng)用、綜合應(yīng)用和進(jìn)階應(yīng)用。

2019-12-05 07:08:00 3476

3476

本課程以目前流行的Xilinx 7系列FPGA的開發(fā)為主線,全面講解FPGA的原理及電路設(shè)計(jì)、Verilog HDL語言及VIVADO的應(yīng)用,并循序漸進(jìn)地從組合邏輯、時序邏輯的開發(fā)開始,深入到FPGA的基礎(chǔ)應(yīng)用、綜合應(yīng)用和進(jìn)階應(yīng)用。

2019-12-02 07:10:00 3646

3646

Verilog HDL是一種硬件描述語言,以文本形式來描述數(shù)字系統(tǒng)硬件的結(jié)構(gòu)和行為的語言,用它可以表示邏輯電路圖、邏輯表達(dá)式,還可以表示數(shù)字邏輯系統(tǒng)所完成的邏輯功能。

2019-11-28 07:02:00 3391

3391 大家都知道軟件設(shè)計(jì)使用軟件編程語言,例如我們熟知的C、Java等等,而FPGA設(shè)計(jì)使用的是HDL語言,例如VHDL和Verilog HDL。說的直白點(diǎn),F(xiàn)PGA的設(shè)計(jì)就是邏輯電路的實(shí)現(xiàn),就是把我們從

2019-12-05 07:10:00 4016

4016

Verilog HDL是一種硬件描述語言,以文本形式來描述數(shù)字系統(tǒng)硬件的結(jié)構(gòu)和行為的語言,用它可以表示邏輯電路圖、邏輯表達(dá)式,還可以表示數(shù)字邏輯系統(tǒng)所完成的邏輯功能。 Verilog HDL和VHDL是世界上最流行的兩種硬件描述語言,都是在20世紀(jì)80年代中期開發(fā)出來的。

2019-11-13 07:03:00 3872

3872 Verilog HDL是一種硬件描述語言,以文本形式來描述數(shù)字系統(tǒng)硬件的結(jié)構(gòu)和行為的語言,用它可以表示邏輯電路圖、邏輯表達(dá)式,還可以表示數(shù)字邏輯系統(tǒng)所完成的邏輯功能。

2019-11-20 07:00:00 6280

6280 硬件描述語言基本語法和實(shí)踐

(1)VHDL 和Verilog HDL的各自特點(diǎn)和應(yīng)用范圍

(2)Verilog HDL基本結(jié)構(gòu)語言要素與語法規(guī)則

(3) Verilog HDL組合邏輯語句結(jié)構(gòu)

2019-07-03 17:36:00 54

54 本文檔的主要內(nèi)容詳細(xì)介紹的是模擬電路教程之時序邏輯電路的課件資料免費(fèi)下載包括了:1 概述,2 時序邏輯電路的分析方法,3 若干常用的時序邏輯電路,4 時序邏輯電路的設(shè)計(jì)方法。

2020-06-22 08:00:00 13

13 HDL是一種硬件描述語言,以文本形式來描述數(shù)字系統(tǒng)硬件的結(jié)構(gòu)和行為的語言,用它可以表示邏輯電路圖、邏輯表達(dá)式,還可以表示數(shù)字邏輯系統(tǒng)所完成的邏輯功能。 Verilog HDL和VHDL是世界上最流行

2020-08-26 09:14:31 64637

64637 本文檔的主要內(nèi)容詳細(xì)介紹的是組合邏輯電路和時序邏輯電路的學(xué)習(xí)課件免費(fèi)下載包括了:任務(wù)一 組合邏輯電路,任務(wù)二 編碼器,任務(wù)三 譯碼器,任務(wù)四 集成觸發(fā)器,任務(wù)五 寄存器,任務(wù)六 計(jì)數(shù)器。

2020-10-27 15:58:24 31

31 在現(xiàn)階段,作為設(shè)計(jì)人員熟練掌握 Verilog HDL程序設(shè)計(jì)的多樣性和可綜合性,是至關(guān)重要的。作為數(shù)字集成電路的基礎(chǔ),基本數(shù)字邏輯電路的設(shè)計(jì)是進(jìn)行復(fù)雜電路的前提。本章通過對數(shù)字電路中基本邏輯電路的erilog HDL程序設(shè)計(jì)進(jìn)行講述,掌握基本邏輯電路的可綜合性設(shè)計(jì),為具有特定功能的復(fù)雜電路的設(shè)計(jì)打下基礎(chǔ)

2020-12-09 11:24:00 37

37 Verilog HDL是一種以文本形式描述數(shù)字系統(tǒng)硬件的結(jié)構(gòu)和行為的硬件描述語言,也可描述邏輯電路圖、邏輯表達(dá)式等。Verilog HDL和VHDL是目前主流的、最受歡迎的兩種硬件描述語言。

2021-07-23 14:36:55 11932

11932 筆試時也很常見。 [例1] 一個簡單的狀態(tài)機(jī)設(shè)計(jì)--序列檢測器 序列檢測器是時序數(shù)字電路設(shè)計(jì)中經(jīng)典的教學(xué)范例,下面我們將用Verilog HDL語言來描述、仿真、并實(shí)現(xiàn)它。 序列檢測器的邏輯功能描述

2021-08-10 16:33:55 7762

7762

嵌入式開發(fā)Verilog教程(二)——Verilog HDL設(shè)計(jì)方法概述前言一、Verilog HDL語言簡介1.1 Verilog HDL語言是什么1.2前言在數(shù)字邏輯設(shè)計(jì)領(lǐng)域,迫切需要一種共同

2021-11-03 16:36:01 13

13 筆試時也很常見。[例1] 一個簡單的狀態(tài)機(jī)設(shè)計(jì)--序列檢測器序列檢測器是時序數(shù)字電路設(shè)計(jì)中經(jīng)典的教學(xué)范例,下面我們將用Verilog HDL語言來描述、仿真、并實(shí)現(xiàn)它。序列檢測器的邏輯功能...

2021-12-17 18:28:40 16

16 從今天開始新的一章-Circuits,包括基本邏輯電路、時序電路、組合電路等。

2022-10-10 15:39:01 2278

2278 數(shù)字電路根據(jù)邏輯功能的不同特點(diǎn),可以分成兩大類,一類叫組合邏輯電路(簡稱組合電路),另一類叫做時序邏輯電路(簡稱時序電路)。組合邏輯電路在邏輯功能上的特點(diǎn)是任意時刻的輸出僅僅取決于該時刻的輸入

2023-03-14 17:06:50 8731

8731

時序電路的考察主要涉及分析與設(shè)計(jì)兩個部分,上文介紹了時序邏輯電路的一些分析方法,重點(diǎn)介紹了同步時序電路分析的步驟與注意事項(xiàng)。 本文就時序邏輯電路設(shè)計(jì)的相關(guān)問題進(jìn)行討論,重點(diǎn)介紹時序邏輯電路的核心部分——計(jì)數(shù)器。

2023-05-22 17:01:29 5307

5307

時序邏輯電路分析和設(shè)計(jì)的基礎(chǔ)是組合邏輯電路與觸發(fā)器,所以想要分析和設(shè)計(jì),前提就是必須熟練掌握各種常見的組合邏輯電路與觸發(fā)器功能,尤其是各種觸發(fā)器的特征方程與觸發(fā)模式,因此前幾文的基礎(chǔ)顯得尤為重要。 本文主要介紹時序邏輯電路的分析方法。

2023-05-22 18:24:31 5503

5503

?時序邏輯電路分為同步時序邏輯電路和異步時序邏輯電路兩大類。

2023-06-21 14:35:58 8532

8532

Verilog HDL是一種硬件描述語言,以文本形式來描述數(shù)字系統(tǒng)硬件的結(jié)構(gòu)和行為的語言,用它可以表示邏輯電路圖、邏輯表達(dá)式,還可以表示數(shù)字邏輯系統(tǒng)所完成的邏輯功能。 Verilog HDL

2023-08-29 15:58:29 0

0 電子發(fā)燒友網(wǎng)站提供《時序邏輯電路電子課件.ppt》資料免費(fèi)下載

2023-11-21 14:43:40 0

0 時序邏輯電路是一種能夠存儲信息并根據(jù)時鐘信號按照特定順序執(zhí)行操作的電路。它是計(jì)算機(jī)硬件中非常重要的一部分,用于實(shí)現(xiàn)存儲器、時序控制器等功能。與之相對的是組合邏輯電路,它根據(jù)輸入信號的組合情況,立即

2024-02-06 11:18:34 13635

13635 時序邏輯電路的輸出與輸入信號以及內(nèi)部存儲器狀態(tài)有關(guān)。時序邏輯電路是一類特殊的數(shù)字電路,其輸出信號的值不僅取決于當(dāng)前的輸入信號,還取決于過去的輸入信號以及內(nèi)部存儲器的狀態(tài)。 時序邏輯電路由兩部分

2024-02-06 14:30:23 4297

4297 什么是組合邏輯電路和時序邏輯電路?時序邏輯電路和組合邏輯電路的區(qū)別是什么? 組合邏輯電路和時序邏輯電路是數(shù)字電路中兩種基本類型的電路設(shè)計(jì)。 組合邏輯電路是由邏輯門組成的,邏輯門的輸出僅由它的當(dāng)前輸入

2024-03-26 16:12:14 6631

6631 時序邏輯電路是數(shù)字電路中的一種,它不僅具有組合邏輯電路的即時輸出特性,還擁有記憶功能,能夠根據(jù)輸入信號和當(dāng)前狀態(tài)產(chǎn)生輸出。

2024-05-23 15:19:42 5718

5718 在數(shù)字電子學(xué)中,邏輯電路和時序邏輯電路是兩種基本的電路類型。它們在處理數(shù)字信號和實(shí)現(xiàn)數(shù)字系統(tǒng)時起著關(guān)鍵作用。邏輯電路主要用于實(shí)現(xiàn)基本的邏輯運(yùn)算,如與、或、非等,而時序邏輯電路則用于處理具有時間順序

2024-07-30 15:00:11 2196

2196 時序邏輯電路是一種數(shù)字電路,它根據(jù)輸入信號和電路內(nèi)部狀態(tài)的變化產(chǎn)生輸出信號。時序邏輯電路廣泛應(yīng)用于計(jì)算機(jī)、通信、控制等領(lǐng)域。 一、時序邏輯電路概述 時序邏輯電路是一種動態(tài)邏輯電路,其輸出不僅取決于

2024-07-30 15:02:11 3422

3422 加法器不是時序邏輯電路 ,而是組合邏輯電路的一種。時序邏輯電路和組合邏輯電路的主要區(qū)別在于它們?nèi)绾翁幚磔敵鲂盘枴?組合邏輯電路的輸出僅依賴于當(dāng)前的輸入信號,而不依賴于電路之前的狀態(tài)或輸入歷史。這

2024-08-28 11:05:51 2051

2051 時序邏輯電路是數(shù)字電路中的一種重要類型,它具有存儲功能,能夠根據(jù)輸入信號和內(nèi)部狀態(tài)的變化來改變其輸出。時序邏輯電路廣泛應(yīng)用于計(jì)算機(jī)、通信、控制等領(lǐng)域。本文將介紹時序邏輯電路的描述方法,包括狀態(tài)圖

2024-08-28 11:37:00 2093

2093 時序邏輯電路是數(shù)字電路中的一種重要類型,它具有存儲和處理信息的能力。時序邏輯電路的描述方法有很多種,不同的方法適用于不同的設(shè)計(jì)和分析場景。以下是五種常見的時序邏輯電路描述方法的介紹: 狀態(tài)圖

2024-08-28 11:39:35 3536

3536 時序邏輯電路是數(shù)字電路中的一種重要類型,其特點(diǎn)是電路的輸出不僅取決于當(dāng)前的輸入,還取決于電路的狀態(tài)。時序邏輯電路廣泛應(yīng)用于計(jì)算機(jī)、通信、控制等領(lǐng)域。 1. 引言 在數(shù)字電路設(shè)計(jì)中,時序邏輯電路是實(shí)現(xiàn)

2024-08-28 11:41:38 1914

1914 時序邏輯電路是數(shù)字電路中的一種重要類型,它不僅在計(jì)算機(jī)、通信、控制等領(lǐng)域有著廣泛的應(yīng)用,而且對于理解和設(shè)計(jì)現(xiàn)代電子系統(tǒng)具有重要意義。 1. 時序邏輯電路的基本概念 時序邏輯電路(Sequential

2024-08-28 11:45:49 5359

5359 時序邏輯電路必不可少的部分是 存儲電路 ,這一結(jié)論主要基于時序邏輯電路的基本工作原理和特性。存儲電路在時序邏輯電路中扮演著至關(guān)重要的角色,它使得電路能夠存儲和記憶之前的狀態(tài)信息,并在需要時根據(jù)這些

2024-08-28 14:12:09 1491

1491 時序邏輯電路確實(shí)具有記憶功能 。這一特性是時序邏輯電路與組合邏輯電路的本質(zhì)區(qū)別之一。

2024-08-29 10:31:28 2362

2362 時序邏輯電路的主要故障分析是一個復(fù)雜而重要的課題,它涉及電路的穩(wěn)定性、可靠性以及整體性能。以下是對時序邏輯電路主要故障的全面分析,旨在幫助理解和解決這些故障。

2024-08-29 11:13:44 2415

2415

電子發(fā)燒友App

電子發(fā)燒友App

評論