在《數(shù)字電路之如雷貫耳的“邏輯電路”》、《數(shù)字電路之數(shù)字集成電路IC》之后,本文是數(shù)字電路入門3,將帶來「時序電路」的講解,及其核心部件觸發(fā)器的工作原理。什么是時序電路?

2016-08-01 10:58:48 19579

19579

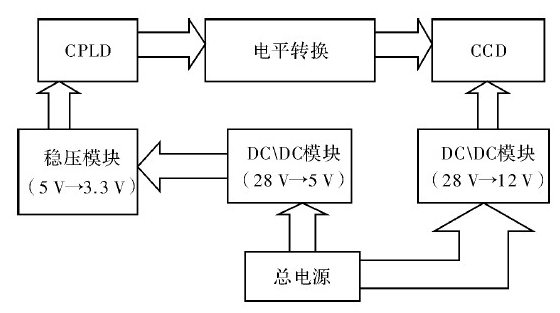

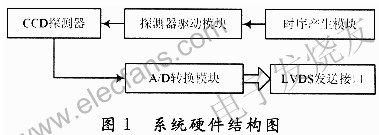

為了降低CCD驅(qū)動電路的功耗,提出了基于共模扼流圈的CCD驅(qū)動電路設計方案。該方案采用CCD驅(qū)動器產(chǎn)生低電壓的驅(qū)動信號,然后利用共模扼流圈進行電壓幅度的放大。

2013-10-24 15:54:48 4186

4186

KAI-01050是KODAK公司生產(chǎn)的最高幀頻可達120 f/s的高速面陣CCD.本方案針對其驅(qū)動信號特點,詳細介紹CCD各部分功率驅(qū)動電路設計。

2013-10-28 09:29:12 5030

5030

根據(jù)線陣CCD圖像檢測和識別系統(tǒng)的要求,分析線陣CCD圖像與子圖像的位置關(guān)系,采用“圖像轉(zhuǎn)置緩沖區(qū)”和讀寫狀態(tài)機的處理方式,設計基于FPGA 的線陣CCD 子圖像提取模塊,具有FPGA 資源占用少、邏輯清晰的特點。用MATLAB 和Modelsim 軟件進行聯(lián)合仿真,驗證了設計的正確性。

2014-02-18 15:34:54 1778

1778

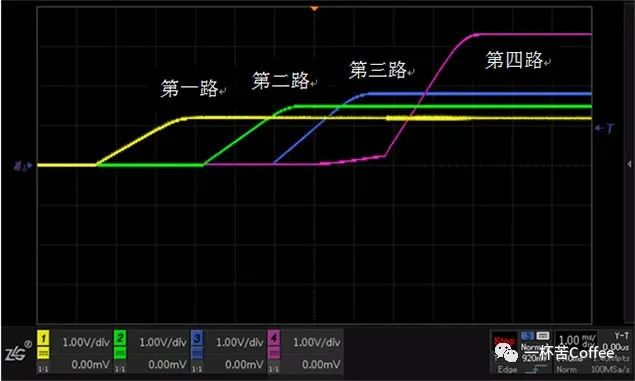

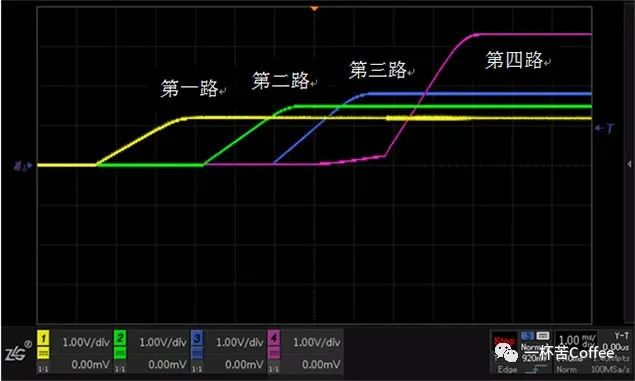

上電時序(Power-up Sequeence)是指各電源軌上電的先后關(guān)系。 與之對應的是下電時序,但是在電路設計過程中,一般不會去考慮下電時序(特殊的場景除外)。今天,我們主要了解一下上電時序控制相關(guān)內(nèi)容。

2023-12-11 18:17:05 5626

5626

的設計與實現(xiàn),基于FPGA的模式可調(diào)線陣CCD驅(qū)動電路設計,基于FPGA的線陣CCD驅(qū)動模塊的實現(xiàn),基于FPGA的線陣型CCD驅(qū)動電路設計,基于USB3_0的FPGA對線陣CCD驅(qū)動時序電路設計,基于單片機的線陣CCD驅(qū)動模塊硬件設計與實現(xiàn)。

2019-06-03 16:45:25

有木有做過線陣CCD驅(qū)動的,線陣CCD輸出經(jīng)過AD轉(zhuǎn)換后,為什么被遮擋部分的輸出值大于光照區(qū)的值,不是應該相反嘛,求解答

2017-03-29 11:21:19

采樣的時序控制。最后,利用quartus7.2軟件平臺結(jié)合VHDL語言進行開發(fā),對所需驅(qū)動脈沖進行仿真設計。仿真結(jié)果表明,該驅(qū)動電路簡單、功耗小、成本低、抗干擾能力強,適用于設備小型化的要求。基于FPGA的線陣CCD驅(qū)動時序及模擬信號處理的設計.pdf

2020-09-01 14:50:25

有木有做過線陣CCD驅(qū)動的,線陣CCD輸出經(jīng)過AD轉(zhuǎn)換后,為什么被遮擋部分的輸出值大于光照區(qū)的值,不是應該相反嘛,求解答

2017-03-29 11:20:08

邏輯電路分為組合邏輯電路和時序邏輯電路。第四章已經(jīng)學習了組合邏輯電路的分析與設計的方法,這一章我們來學習時序電路的分析與設計的方法。在學習時序邏輯電路時應注意的重點是常用時序部件的分析與設計這一

2018-08-23 10:28:59

本帖最后由 eehome 于 2013-1-5 09:47 編輯

線陣CCD驅(qū)動的幾種設計方法分享

2012-11-14 19:57:15

有木有做過線陣CCD驅(qū)動的,線陣CCD輸出經(jīng)過AD轉(zhuǎn)換后,為什么被遮擋部分的輸出值大于光照區(qū)的值,不是應該相反嘛,求解答

2017-03-29 11:18:40

有沒哪位高手可以做線陣CCD測量開發(fā),可聯(lián)系。QQ:八五一五47九六九

2012-02-08 10:36:08

#CMOS線陣傳感器##CCD線陣傳感器#在項目中,CMOS線陣傳感器的型號我用的是,濱松光子的S8378-512Q,這個CMOS線陣傳感器用起來比較方便,我的方案是用單片機對其進行驅(qū)動,輸出類似于

2022-01-19 06:19:17

Verilog 設計初學者例程一 時序電路設計 By 上海 無極可米 12/13/2001 ---------基礎-----------1. 1/2分頻器module halfclk(reset

2018-08-23 13:43:31

什么是時序電路?時序電路核心部件觸發(fā)器的工作原理

2021-03-04 06:32:49

利用STM32的定時器中斷功能編寫線陣CCD(ILX554B)的驅(qū)動時序1.利用定時器完成線陣CCDILX554B的驅(qū)動時序,采用兩個管腳1個用于產(chǎn)生ROG信號,一個用于產(chǎn)生CLK信號2.使用一個

2022-01-07 07:01:51

各位大神,有沒有做過STM32驅(qū)動線陣CCD的啊?小弟求指教啊。

2014-05-12 16:22:41

為了實現(xiàn)—是彈武器瞄準自動化,本文設計了基于DSP和FPGA的高速高精確度雙通道CCD圖像采集系統(tǒng),采用QUartuBn在AJtera的FPGA器件CYCLONEII上設計了CCD驅(qū)動時序電路,采用

2014-11-07 14:54:07

實驗二 基本時序電路設計(1)實驗目的:熟悉QuartusⅡ的VHDL文本設計過程,學習簡單時序電路的設計、仿真和硬件測試。(2)實驗內(nèi)容:Ⅰ.用VHDL設計一個帶異步復位的D觸發(fā)器,并利用

2009-10-11 09:21:16

CCD驅(qū)動電路的實現(xiàn)是CCD應用技術(shù)的關(guān)鍵問題。以往大多是采用普通數(shù)字芯片實現(xiàn)驅(qū)動電路,CCD外圍電路復雜,為了克服以上方法的缺點,利用VHDL硬件描述語言.運用FPGA技術(shù)完成驅(qū)動時序電路的實現(xiàn)

2019-10-21 06:05:17

根據(jù)波形圖設計異步時序電路 急 求大神

2017-12-08 23:07:44

線陣CCD數(shù)據(jù)采集系統(tǒng)的特點有哪些?如何實現(xiàn)線陣CCD數(shù)據(jù)采集系統(tǒng)的硬件電路設計?如何實現(xiàn)線陣CCD數(shù)據(jù)采集系統(tǒng)軟件的設計?

2021-04-09 06:58:21

求Labview采集線陣CCD數(shù)據(jù)的程序,我用的CCD是TCD1501C,類似的程序也參考一下啊

2016-10-10 20:26:55

CD 1501D CCD工作參數(shù)及時序分析基于FPGA的線陣CCD驅(qū)動時序及模擬信號處理的設計

2021-04-22 06:13:19

用單片機驅(qū)動線陣CCD的探討

2012-08-19 22:23:15

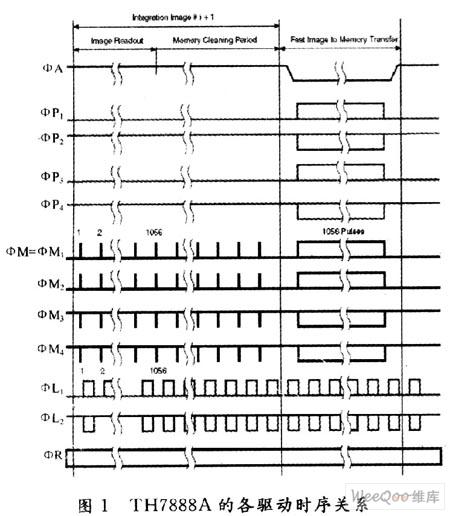

邏輯器件的編程,能實現(xiàn)任意復雜的時序邏輯, 且調(diào)試方便, 只使用一片集成電路以及少數(shù)外圍器件, 故可靠性高。本文即采用這種方法, 實現(xiàn)了CCD97 所需的12 路驅(qū)動時序。 1CCD97 簡介

2018-11-13 11:13:20

PLD練習2(時序電路)

2006-05-26 00:14:19 20

20 線陣CCD數(shù)據(jù)采集及LCD顯示 Linear Array CCD Data Acquisition and LCD Display

摘要:以TCD1200D為例,介紹了線陣CCD的一種通用高速數(shù)據(jù)采集方法,詳細介紹了電路組成、數(shù)據(jù)采集軟件實現(xiàn),

2009-01-11 12:08:46 45

45 以紡織布坯疵點在線檢測系統(tǒng)為應用背景,探討了基于Camera Link接口協(xié)議標準的線陣CCD相機圖像高速采集邏輯控制接口的實現(xiàn)技術(shù)。重點闡述了信號轉(zhuǎn)換接口、基于FPGA的生成幀圖

2009-06-03 09:50:56 23

23 時序電路設計實例 (Sequential-Circuit Design Examples):We noted in previous chapters that we typically deal

2009-09-26 13:01:04 37

37 針對Kodak 公司的前照明行間轉(zhuǎn)移型面陣CCD KAI-0340,對其驅(qū)動要求進行詳細的分析,設計滿足CCD 所需偏置電壓的供電模塊;搭建CCD 時序脈沖驅(qū)動器電路;利用Xilinx 公司的可編程邏

2009-12-26 16:50:20 36

36 在分析了Sarnoff 公司的VCCD512H 面陣型CCD 圖像傳感器驅(qū)動時序關(guān)系的基礎上,結(jié)合某CCD 相機電子系統(tǒng)的總體要求,完成了基于FPGA 驅(qū)動時序發(fā)生器與數(shù)據(jù)緩存器的一體化設計。選用X

2010-01-06 15:23:12 36

36 為解決TDI-CCD 作為遙感相機的圖像傳感器在使用中所面臨的時序電路設計問題,文中較為詳細地介紹了TDI-CCD 的結(jié)構(gòu)和工作原理,并根據(jù)工程項目所使用的ILE2TDI-CCD 的特性,設

2010-01-12 09:54:50 22

22 本文提出了一種基于線陣CCD的精密測角系統(tǒng),該系統(tǒng)由線陣CCD作為光學傳感器、利用嵌入式處理器和可編程邏輯器件對CCD進行驅(qū)動和數(shù)據(jù)采集和處理。實現(xiàn)了對小范圍內(nèi)角度的精密測

2010-02-24 11:35:34 32

32 針對傳統(tǒng)驅(qū)動電路一旦做出修改,則需對硬件或程序進行改變的缺點,以型號為TCD1707D的線陣CCD為例,介紹了一種工作模式可調(diào)的驅(qū)動方法.該方法是利用復雜可編程邏輯器件和控制外端

2010-04-27 08:53:07 61

61 摘要:針對同步時序電路的初始化問題,提出了一種新的實現(xiàn)方法。當時序電路中有未確定狀態(tài)的觸發(fā)器時,就不能順利完成該電路的測試生成,因此初始化是時序電路測試生成中

2010-05-13 09:36:52 6

6 摘 要:本文以日本東芝公司的線陣CCD器件TCD1206SUP為例,在研究了線陣CCD器件工作原理和驅(qū)動電路波形的基礎上,介紹了采用圖形式層次設計方法,用復雜可編程邏輯器件(CPLD)設計線陣CCD

2010-07-15 13:42:30 68

68 本文介紹將量子進化算法應用在時序電路測試生成的研究結(jié)果。結(jié)合時序電路的特點,本文將量子計算中的量子位和疊加態(tài)的概念引入傳統(tǒng)的測試生成算法中,建立了時序電路的量

2010-08-03 15:29:01 0

0 摘要:本文就彌補以往用單片機產(chǎn)生線陣CCD驅(qū)動時序的不足進行了探討;給出了使用AVR單片機產(chǎn)生驅(qū)動TCD1206線陣CCD的具體實例及相應程序。其定時關(guān)系精確,驅(qū)動頻率達到推薦的速率

2010-09-14 21:30:44 109

109 針對設計微型光譜儀時常會根據(jù)需要更換CCD,PDA的現(xiàn)狀,采用Cypress公司的AD2131Q和Cyclone系列FPGA設計適用于多種線陣CCD和小型面陣CCD的通用采集系統(tǒng),設計16口入8口出異步FIFO,提供192

2010-12-30 10:30:37 0

0 摘要:分析了線陣CCD用于實時檢測系統(tǒng)的特點和要求,介紹了一種基于AT89C2051單片機的線陣CCD實時檢測系統(tǒng)的設計方案。本方案電路結(jié)構(gòu)簡單可靠,信號處理靈活檢

2006-03-11 11:48:25 1145

1145

線陣CCD在圖像傳感和測量技術(shù)領(lǐng)域的應用中發(fā)欣極為迅速。為滿足自適應測量的工程化需要,設計出了基于線陣CCD的單同軸電纜雙向時分復用傳輸外總線。

2006-03-11 13:24:50 1055

1055

時序電路設計串入/并出移位寄存器一 實驗目的1掌握VHDL語言的基本描述語句的使用方法。2掌握使用VHDL語言進行時序電路設計的方法。

2009-03-13 19:29:51 6306

6306

時序電路設計串入/并出移位寄存器一 實驗目的1掌握VHDL語言的基本描述語句的使用方法。2掌握使用VHDL語言進行時序電路設計的方法。

2009-03-13 19:29:52 2380

2380

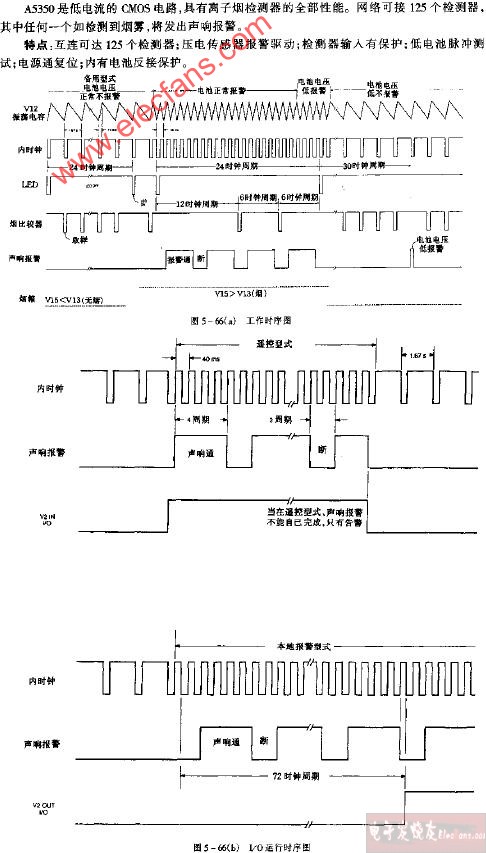

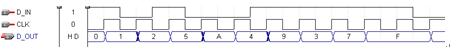

A5350工作時序電路圖

2009-07-03 12:22:16 905

905

同步時序電路

4.2.1 同步時序電路的結(jié)構(gòu)和代數(shù)法描述

2010-01-12 13:31:55 5768

5768

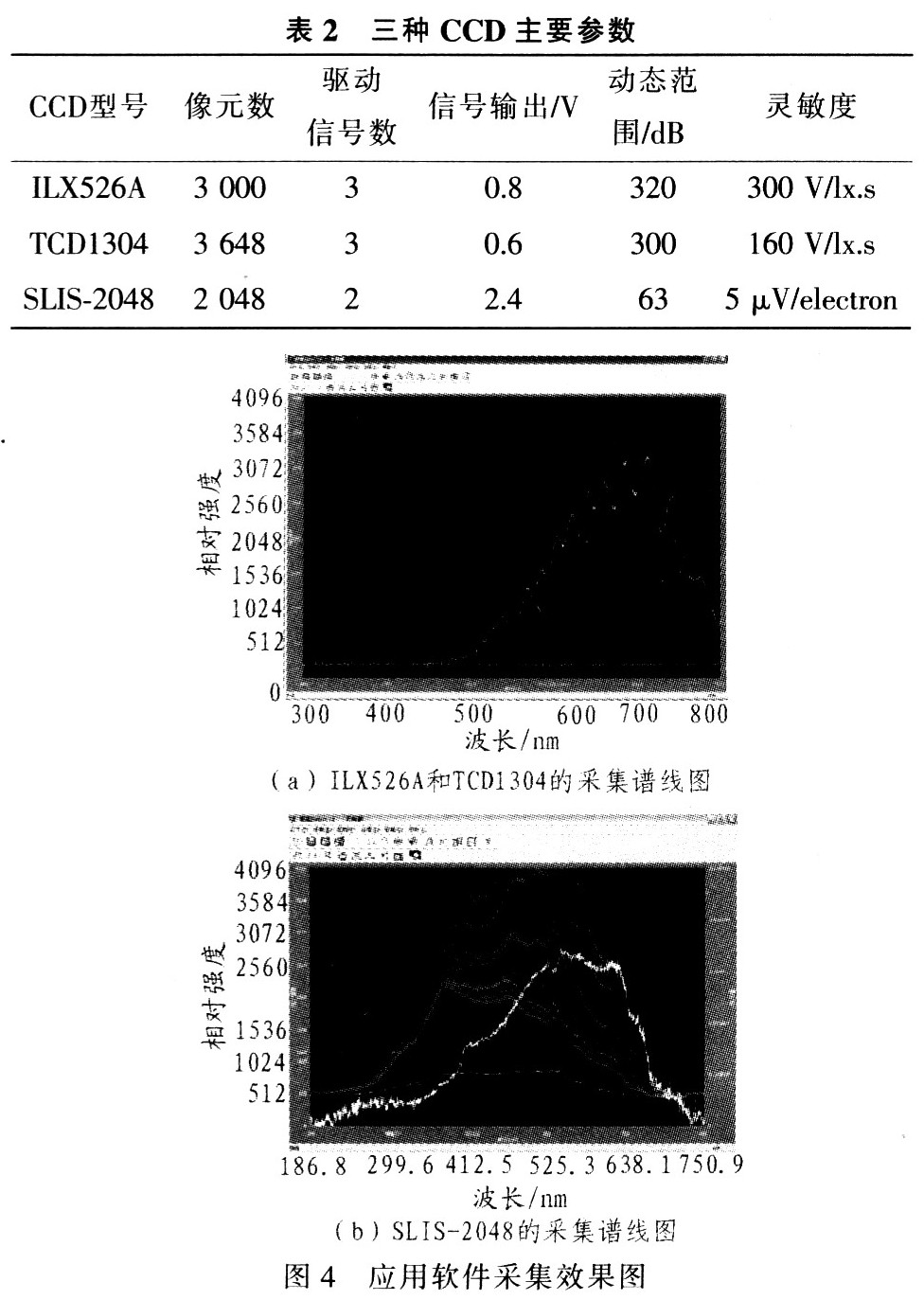

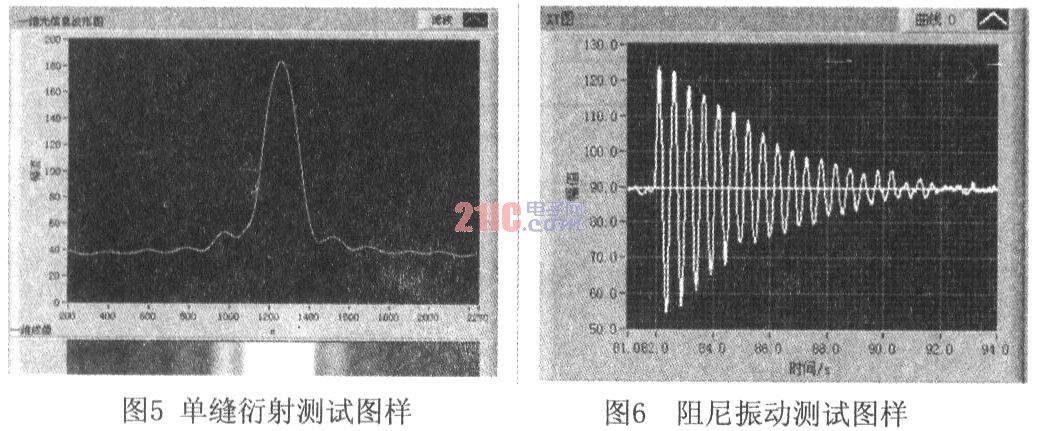

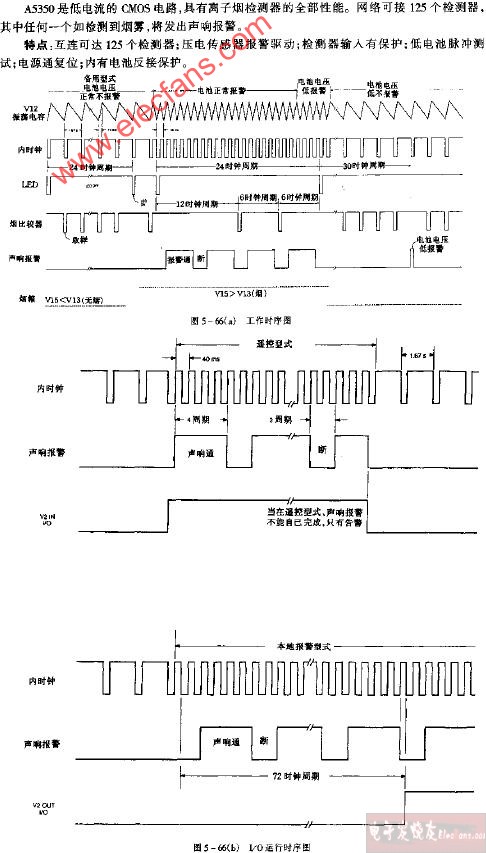

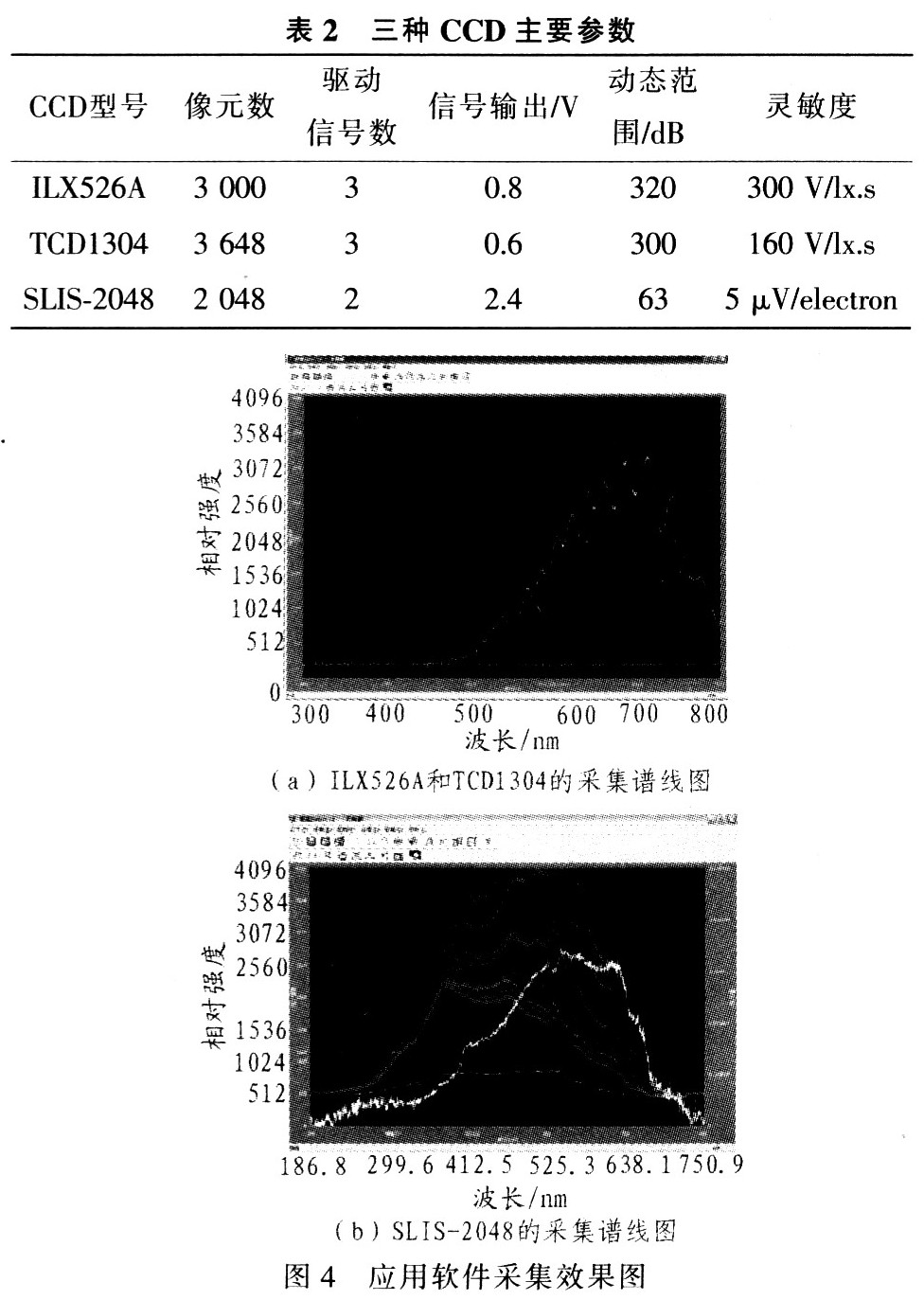

通用線陣CCD采集系統(tǒng)設計

摘要:針對設計微型光譜儀時常會根據(jù)需要更換CCD,PDA的現(xiàn)狀,采用Cypress公司的AD21310和Cyclone系列FPGA設計適用于多種線陣CCD和小型面陣CCD的通

2010-03-13 10:23:28 2726

2726

基于線陣CCD的圖像和位置傳感系統(tǒng)

摘要:本文介紹的是一種基于線陣CCD的圖像和位置傳感系統(tǒng)。此系統(tǒng)以C18051F020型微控制器作為下位機,進行CCD的驅(qū)動和與計算機(上位機)

2010-04-13 14:15:49 1492

1492

什么是時序電路

任意時刻的穩(wěn)定輸出,不僅與該時刻的輸入有關(guān),而且還

2010-01-12 13:23:14 8908

8908

CCD驅(qū)動電路的實現(xiàn)是CCD應用技術(shù)的關(guān)鍵問題。以往大多是采用普通數(shù)字芯片實現(xiàn)驅(qū)動電路,CCD外圍電路復雜,為了克服以上方法的缺點,利用VHDL硬件描述語言.運用FPGA技術(shù)完

2010-08-30 09:58:19 1581

1581

捅要:為了實現(xiàn)是彈武器瞄準自動化,本文設計了基于DSP和FPGA的高速高精確度雙通道CCD圖像采集系統(tǒng),采用QUartuBn在AJtera的FPGA器件CYCLONEII上設計了CCD驅(qū)動時序電路,采用PsPICE設計了可以

2011-02-25 13:48:05 190

190 設計了一種以 線陣CCD 作為光電傳感器的測隙裝置。首先設計了測隙裝置的總體方案,分析了方案的可行性;其次以CPLD為驅(qū)動利用Verlog-HDL語言設計了線陣CCD的工作時序,在對輸出信號分

2011-08-10 16:41:58 44

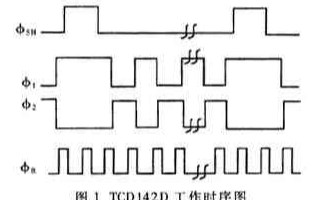

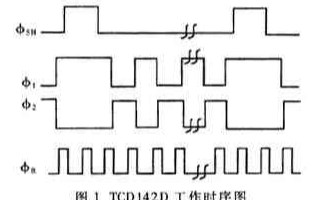

44 TCD142D構(gòu)成線陣 CCD驅(qū)動 電路:

2011-10-28 11:17:17 4954

4954

采用MAXⅡ器件的EPM240T100C5N為控制核心,以TCD1500C為例,設計了基于CPLD的線陣CCD驅(qū)動電路,完成了硬件電路的原理圖的設計,并實現(xiàn)了軟件調(diào)試。通過QuartusⅡ軟件平臺,對其進行了模擬仿真。實

2011-11-03 15:24:40 129

129 本文在分析當前圖像采集系統(tǒng)的前提下,充分利用USB和FPGA的高速、靈活等優(yōu)勢,提出并設計了一種基于USB接口的線陣CCD圖像采集系統(tǒng)。系統(tǒng)以Xilinx公司的FPGA為核心控制器,設計了線陣

2011-11-07 14:52:11 156

156 為保證線陣CCD在圖像測量中正常、穩(wěn)定工作.必須設計出適合其工作的時序驅(qū)動電路。在分析TCDl501D線陣CCD驅(qū)動時序關(guān)系的基礎上,通過分析CCD輸出的圖像信號1,給出了內(nèi)、外相關(guān)雙采

2011-11-07 15:08:43 148

148 以TCD1208AP線陣CCD為對象,設計了CCD到PC機串口的接口電路。內(nèi)容主要包括:TCD1208AP驅(qū)動電路、輸出信號處理電路、采樣存儲電路和串行接口電路。使用常規(guī)元器件完成了電路設計,實現(xiàn)

2013-03-06 16:28:35 214

214 為了實現(xiàn)對車牌識別系統(tǒng)對高速行駛車輛圖像分辨率的要求,提出了一種基于線陣CCD掃描的車輛圖像系統(tǒng)的方案,完成了對線陣CCD芯片驅(qū)動電路的設計。該系統(tǒng)的硬件部分完成對線陣

2013-09-03 16:45:09 0

0 基于FPGA技術(shù)的RS232接口時序電路設計方案

2017-01-26 11:36:55 30

30 一種基于單片機的新型線陣CCD電路

2017-01-14 22:41:04 16

16 圖像處理技術(shù)應用越來越廣泛,特別是工業(yè)檢測領(lǐng)域。然而,圖像處理技術(shù)應用的基礎是圖像的獲取,為了更加靈活地設計各種應用產(chǎn)品,本課題研究基于FPGA的面陣 CCD驅(qū)動傳輸電路設計,利用該電路能夠獲取高質(zhì)量、高分辨率的圖像,為后續(xù)的圖像處理技術(shù)應用打下基礎。

2017-08-30 16:38:07 3

3 在傳統(tǒng)設計中,所有計算機運算(算法、邏輯和存儲進程)都參考時鐘同步執(zhí)行,時鐘增加了設計中的時序電路數(shù)量。在這個電池供電設備大行其道的移動時代,為了節(jié)省每一毫瓦(mW)的功耗,廠商間展開了殘酷的競爭

2017-11-15 15:40:13 12

12 針對面陣CCD KAI-1020 在高幀頻工作模式下的驅(qū)動要求,以FPGA 作為控制單元及時序發(fā)生器,完成CCD 高幀頻工作模式下的硬件及軟件設計,仿真驗證了驅(qū)動時序的正確性,完成了硬件電路的調(diào)試

2017-11-18 13:07:01 2739

2739

,在此基礎上設計出合理的時序電路,選用現(xiàn)場可編程邏輯門陣列(FPGA)作為硬件設計平臺,使用VHDL 語言對驅(qū)動電路方案進行了硬件描述,采用EDA 軟件對所設計的時序發(fā)生器成功地進行了功能仿真。

2017-11-24 14:24:45 2668

2668

CCD驅(qū)動 電路的實現(xiàn)是CCD應用技術(shù)的關(guān)鍵問題。以往大多是采用普通數(shù)字芯片實現(xiàn)驅(qū)動電路,CCD外圍電路復雜,為了克服以上方法的缺點,利用VHDL硬件描述語言.運用FPGA技術(shù)完成驅(qū)動時序電路的實現(xiàn)

2017-11-24 18:55:51 2079

2079

工作要求的CCD驅(qū)動方法才能保證測量結(jié)果準確。 在驅(qū)動CCD時要解決的兩個主要問題分別是驅(qū)動時序的產(chǎn)生和輸出信號的采集處理。在驅(qū)動時序產(chǎn)生方面,以往的研究大多只以成功驅(qū)動CCD為目的,因此掃描頻率不高,一般采用器件的典型頻

2018-01-24 14:12:43 0

0 在分析了SONY ICX415AL行間轉(zhuǎn)移型面陣CCD的驅(qū)動時序的基礎之上,提出了基于FPGA的驅(qū)動時序發(fā)生器的設計方案,并使用VHDL語言實現(xiàn)了該設計方案。整個設計充分結(jié)合了FPGA器件的設計簡單

2018-05-22 10:21:00 3841

3841

“時鐘是時序電路的控制者” 這句話太經(jīng)典了,可以說是FPGA設計的圣言。FPGA的設計主要是以時序電路為主,因為組合邏輯電路再怎么復雜也變不出太多花樣,理解起來也不沒太多困難。但是時序電路就不同了

2018-07-21 10:55:37 5151

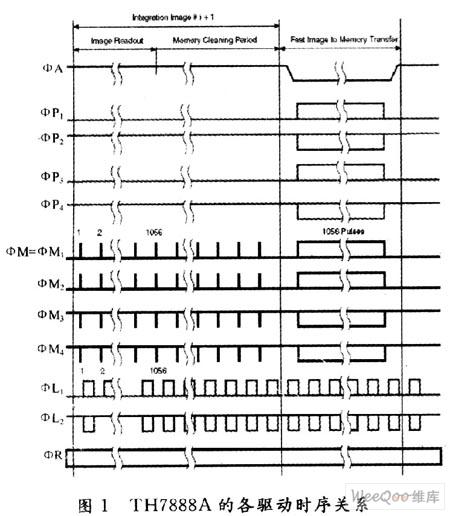

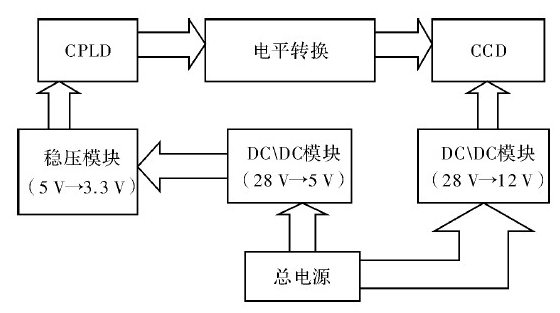

5151 本文主要介紹CCD傳感器驅(qū)動電路的設計,包括驅(qū)動時序產(chǎn)生電路、電源變換電路和驅(qū)動器電路。其中,驅(qū)動時序產(chǎn)生電路向CCD傳感器提供正常工作所需要的各種時序脈沖;電源變換電路向CCD提供正常工作時所需的各種直流偏置電壓;驅(qū)動器電路用來提高驅(qū)動時序的驅(qū)動能力。

2018-12-30 09:47:00 10185

10185

組合電路和時序電路是計算機原理的基礎課,組合電路描述的是單一的函數(shù)功能,函數(shù)輸出只與當前的函數(shù)輸入相關(guān);時序電路則引入了時間維度,時序電路在通電的情況下,能夠保持狀態(tài),電路的輸出不僅與當前的輸入有關(guān),而且與前一時刻的電路狀態(tài)相關(guān),如我們個人PC中的內(nèi)存和CPU中的寄存器,均為時序電路。

2018-09-25 09:50:00 25945

25945 關(guān)鍵詞:時序電路 , 同步 同步時序電路設計 1.建立原始狀態(tài)圖. 建立原始狀態(tài)圖的方法是: 確定輸入、輸出和系統(tǒng)的狀態(tài)函數(shù)(用字母表示). 根據(jù)設計要求,確定每一狀態(tài)在規(guī)定條件下的狀態(tài)遷移方向

2018-10-31 18:14:01 1681

1681 的面陣CCD驅(qū)動時序發(fā)生器設計,基于CPLD的面陣CCD驅(qū)動時序發(fā)生器設計及其硬件實現(xiàn),基于CPLD的線陣CCD驅(qū)動電路的設計,基于CPLD的線陣CCD驅(qū)動電路設計與實現(xiàn),基于CPLD的線陣CCD驅(qū)動

2019-05-16 08:00:00 16

16 時序電路,是由最基本的邏輯門電路加上反饋邏輯回路(輸出到輸入)或器件組合而成的電路,與組合電路最本質(zhì)的區(qū)別在于時序電路具有記憶功能。

2019-09-27 07:10:00 2875

2875

時序電路,是由最基本的邏輯門電路加上反饋邏輯回路(輸出到輸入)或器件組合而成的電路,與組合電路最本質(zhì)的區(qū)別在于時序電路具有記憶功能。

2019-09-23 07:08:00 2734

2734

線陣CCD一般不能直接在測量裝置中使用,因此CCD驅(qū)動信號的產(chǎn)生及輸出信號的處理是設計高精度、高可靠性和高性價比線陣CCD驅(qū)動模塊的關(guān)鍵。

2019-09-18 15:43:43 3795

3795

為保證線陣CCD在圖像測量中正常、穩(wěn)定工作,必須設計出適合其工作的時序驅(qū)動電路。在分析TCD1501D 線陣CCD驅(qū)動時序關(guān)系的基礎上 ,通過分析CCD輸出的圖像信號[1],給出了內(nèi)、外相關(guān)雙采樣

2019-11-21 16:58:25 14

14 設計出高幀頻的成像系統(tǒng),以及能否實現(xiàn)兩個CCD相機的同步采集。CCD工業(yè)相機的關(guān)鍵技術(shù)在于CCD驅(qū)動傳輸電路的設計,為了在實踐中解決這兩個問題,本文對CCD芯片的驅(qū)動脈沖和時序關(guān)系進行了詳細的分析,設計出了基于FPGA的CCD驅(qū)動傳輸電路。

2019-11-26 15:35:15 27

27 介紹了CCD驅(qū)動電路的4種常用方式及其優(yōu)缺點,詳細闡述了基于高速超微型單片機C8051F300的CCD驅(qū)動電路設計,包括內(nèi)部CCD驅(qū)動時序和外部輸出同步信號的產(chǎn)生、像素輸出電壓的簡單處理以及通過RS232接口在線調(diào)整CCD驅(qū)動頻率等。系統(tǒng)克服了目前單片機方式在CCD驅(qū)動應用中存在的一些缺點。

2019-11-26 16:58:19 28

28 介紹了基于CPLD的線陣CCD數(shù)據(jù)采集系統(tǒng)的硬、軟件構(gòu)成,工作原理及設計方案。采用TOSHIBA公司近年來推出的高速線陣CCD芯片TCD1209D,針對其驅(qū)動時序的要求,選用XILINX公司的復雜

2019-11-28 16:23:00 24

24 線陣CCD(Charge Coupled Device)越來越廣泛地被應用到工業(yè)、軍事、民用行業(yè)。采用CCD數(shù)據(jù)采集卡和微機相結(jié)合,對被測圖像信息進行快速采樣、存儲及數(shù)據(jù)處理,是線陣CCD數(shù)據(jù)采集發(fā)展的新方向。配以適當?shù)墓鈱W系統(tǒng),可以實現(xiàn)光-機-電-算一體化設計。

2020-08-21 09:30:14 5871

5871

時序電路是數(shù)字電路的基本電路,也是FPGA設計中不可缺少的設計模塊之一。

2020-09-08 14:21:22 7784

7784

時間的重要性不言而喻,加上時間這個維度就如同X-Y的平面加上了一個Z軸,如同打開了一個新的世界。所以今天我們就要來聊聊時序電路。 在時序電路中,電路任何時刻的穩(wěn)定狀態(tài)輸出不僅取決于當前的輸入,還與前

2021-01-06 17:07:22 5770

5770 設計平臺,使用VHDL語言對驅(qū)動時序發(fā)生器進行了硬件描述,采用QuartusⅡ5.0對所設計的驅(qū)動時序發(fā)生器進行了仿真,針對Altera公司的FPGA器件EP1C3T144C8進行了適配。實驗結(jié)果表明,設計的驅(qū)動電路可以滿足其全幀CCD的各項驅(qū)動要求并且具有設計靈活,硬件調(diào)試簡單的優(yōu)點.

2021-01-26 15:57:01 12

12 針對傳統(tǒng)驅(qū)動電路一旦做出修改,則需對硬件或程序進行改變的缺點,以型號為TCD1707D的線陣CCD為例,介紹了一種工作模式可調(diào)的驅(qū)動方法。該方法是利用復雜可編程邏輯器件和控制外端結(jié)合,通過分別設置

2021-03-01 16:51:00 9

9 針對傳統(tǒng)驅(qū)動電路一旦做出修改,則需對硬件或程序進行改變的缺點,以型號為TCD1707D的線陣CCD為例,介紹了一種工作模式可調(diào)的驅(qū)動方法。該方法是利用復雜可編程邏輯器件和控制外端結(jié)合,通過分別設置

2021-03-01 16:51:00 25

25 組合邏輯和時序邏輯電路是數(shù)字系統(tǒng)設計的奠基石,其中組合電路包括多路復用器、解復用器、編碼器、解碼器等,而時序電路包括鎖存器、觸發(fā)器、計數(shù)器、寄存器等。 在本文中,小編簡單介紹關(guān)于時序電路的類型和特點等相關(guān)內(nèi)容。

2022-09-12 16:44:00 10673

10673

從今天開始新的一章-Circuits,包括基本邏輯電路、時序電路、組合電路等。

2022-10-10 15:39:01 2278

2278 那么,如何才能將過去的輸入狀態(tài)反映到現(xiàn)在的輸出上呢?「時序電路」到底需要些什么呢?人類總是根據(jù)過去的經(jīng)驗,決定現(xiàn)在的行動,這時我們需要的就是—記憶。同樣,「時序電路」也需要這樣的功能。這種能夠?qū)崿F(xiàn)人類記憶功能的元器件就是觸發(fā)器。

2023-03-24 10:48:58 1943

1943

同步和異步時序電路都是使用反饋來產(chǎn)生下一代輸出的時序電路。根據(jù)這種反饋的類型,可以區(qū)分這兩種電路。時序電路的輸出取決于當前和過去的輸入。時序電路分為同步時序電路和異步時序電路是根據(jù)它們的觸發(fā)器來完成的。

2023-03-25 17:29:52 29287

29287

時序電路的考察主要涉及分析與設計兩個部分,上文介紹了時序邏輯電路的一些分析方法,重點介紹了同步時序電路分析的步驟與注意事項。 本文就時序邏輯電路設計的相關(guān)問題進行討論,重點介紹時序邏輯電路的核心部分——計數(shù)器。

2023-05-22 17:01:29 5306

5306

時序電路是由觸發(fā)器等時序元件組成的數(shù)字電路,用于處理時序信號,實現(xiàn)時序邏輯功能。根據(jù)時序元件的類型和組合方式的不同,時序電路可以分為同步時序電路和異步時序電路。本文將從這兩個方面詳細介紹時序電路,并

2024-02-06 11:22:30 2830

2830 時序電路是一種能夠按照特定的順序進行操作的電路。它以時鐘信號為基準,根據(jù)輸入信號的狀態(tài)和過去的狀態(tài)來確定輸出信號的狀態(tài)。時序電路廣泛應用于計算機、通信系統(tǒng)、數(shù)字信號處理等領(lǐng)域。根據(jù)不同的分類標準

2024-02-06 11:25:21 4239

4239 時序電路基本原理是指電路中的輸出信號與輸入信號的時間相關(guān)性。簡單來說,就是電路的輸出信號要依賴于其輸入信號的順序和時間間隔。 時序電路由時鐘信號、觸發(fā)器和組合邏輯電路組成。時鐘信號是時序電路的重要

2024-02-06 11:30:00 3204

3204 電荷耦合器件(CCD)自20世紀70年代初問世以來,已發(fā)展成為圖像采集領(lǐng)域不可或缺的核心組件。其中,線陣CCD和面陣CCD作為兩種主要的CCD類型,各自擁有獨特的結(jié)構(gòu)和功能特性,適用于不同的應用場景。本文將深入探討線陣CCD與面陣CCD的技術(shù)差異以及它們在不同領(lǐng)域的應用。

2025-01-29 16:27:00 2486

2486

電子發(fā)燒友App

電子發(fā)燒友App

評論