今天分享蒸汽發(fā)生器原理、蒸汽發(fā)生器的工作原理、蒸汽發(fā)生器的特點(diǎn)、蒸汽發(fā)生器的優(yōu)點(diǎn)、蒸汽發(fā)生器的作用以及蒸汽發(fā)生器的應(yīng)用領(lǐng)域。

2012-06-03 00:17:17 24274

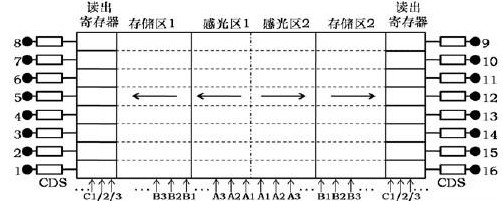

24274 本文在分析了 Sarnoff公司的 VCCD512H型幀轉(zhuǎn)移面陣 CCD芯片的特性和工作過(guò)程后,結(jié)合整個(gè) CCD相機(jī)電子系統(tǒng)的要求,完成了基于 FPGA技術(shù)的驅(qū)動(dòng)時(shí)序發(fā)生器與數(shù)據(jù)緩存器的一體化

2019-01-04 07:55:00 4747

4747

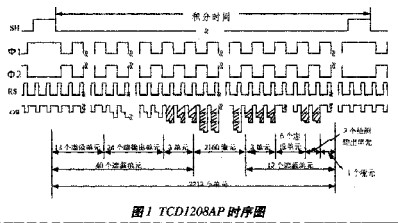

的面陣CCD驅(qū)動(dòng)時(shí)序發(fā)生器設(shè)計(jì),基于CPLD的面陣CCD驅(qū)動(dòng)時(shí)序發(fā)生器設(shè)計(jì)及其硬件實(shí)現(xiàn),基于CPLD的線陣CCD驅(qū)動(dòng)電路的設(shè)計(jì),基于CPLD的線陣CCD驅(qū)動(dòng)電路設(shè)計(jì)與實(shí)現(xiàn),基于CPLD的線陣CCD驅(qū)動(dòng)

2019-06-03 16:45:25

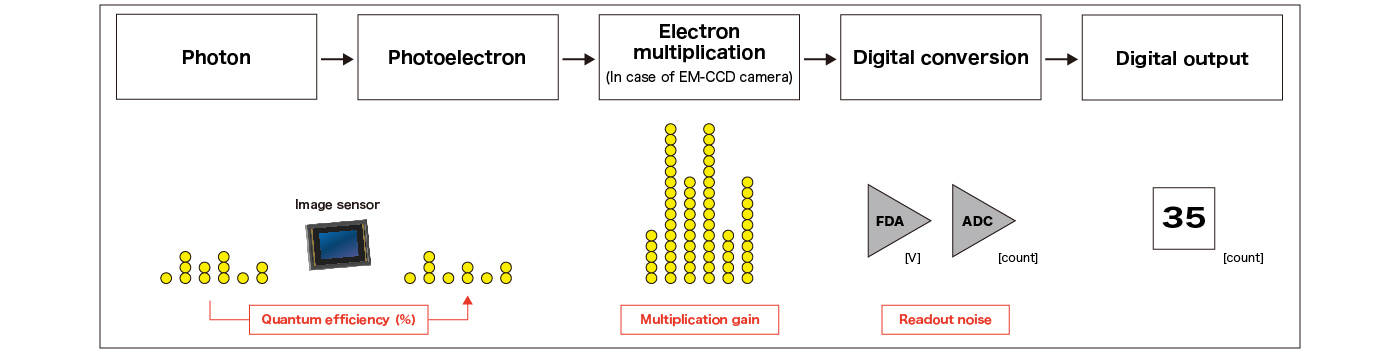

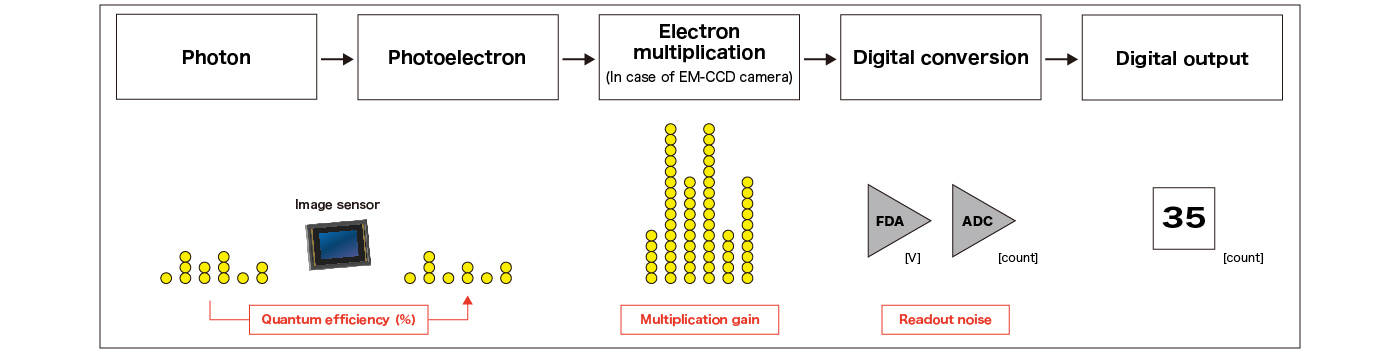

的熒光圖像,并利用終端設(shè)備進(jìn)行相應(yīng)的圖像處理,以此來(lái)對(duì)細(xì)胞的形態(tài)變化等進(jìn)行監(jiān)測(cè)。隨著科學(xué)級(jí)CCD相機(jī)性能的不斷提升,各項(xiàng)新技術(shù)共同推動(dòng)著更高品質(zhì)共聚焦顯微鏡的出現(xiàn)。科學(xué)級(jí)CCD相機(jī)性能的提升對(duì)共聚焦系統(tǒng)

2014-04-03 11:47:05

信號(hào)發(fā)生器和DA轉(zhuǎn)換 FPGA案例教程

2019-08-17 09:01:48

利用FPGA實(shí)現(xiàn)信號(hào)發(fā)生器

2016-08-24 16:24:24

求一個(gè)基于FPGA的DDS信號(hào)發(fā)生器設(shè)計(jì),最好有DA模塊和相位累加器模塊的代碼。

2019-03-18 22:09:03

在做基于FPGA的任意波形發(fā)生器。求大神幫忙。

2014-05-19 10:43:01

可編程邏輯器件(PFGA)或數(shù)字信號(hào)處理器(DSA)。采用硬件方式實(shí)現(xiàn)的時(shí)序脈沖信號(hào)發(fā)生器存在儀器功能單一,信號(hào)輸出通道路數(shù)較少,參數(shù)調(diào)節(jié)不方便,儀器的升級(jí)換代困難等缺點(diǎn);而采用基于LabVIEW的“虛擬儀器

2019-04-09 09:40:04

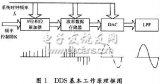

DDS的工作原理和基本結(jié)構(gòu)基于FPGA的DDS信號(hào)發(fā)生器的設(shè)計(jì)如何建立頂層模塊?

2021-04-09 06:46:42

波形發(fā)生器廣泛應(yīng)用于電子電路、自動(dòng)控制和科學(xué)試驗(yàn)領(lǐng)域,是一種為電子測(cè)量工作提供符合嚴(yán)格技術(shù)要求的電信號(hào)設(shè)備,和示波器、電壓表、頻率計(jì)等儀器一樣是最普通、最基本也是應(yīng)用最為廣泛的電子儀器之一,幾乎所有電參量的測(cè)量都要用到波形發(fā)生器。

2019-10-15 06:30:37

本文采用atelra公司的可編程芯片FPGA設(shè)計(jì)了一款周期和輸出個(gè)數(shù)可變的脈沖發(fā)生器。經(jīng)過(guò)板級(jí)調(diào)試獲得良好的運(yùn)行效果。

2021-04-29 07:08:33

本文在分析了Sarnoff公司的VCCD512H型幀轉(zhuǎn)移面陣CCD芯片的特性和工作過(guò)程后,結(jié)合整個(gè)CCD相機(jī)電子系統(tǒng)的要求,完成了基于FPGA技術(shù)的驅(qū)動(dòng)時(shí)序發(fā)生器與數(shù)據(jù)緩存器的一體化設(shè)計(jì)。即在一塊

2021-06-08 06:35:41

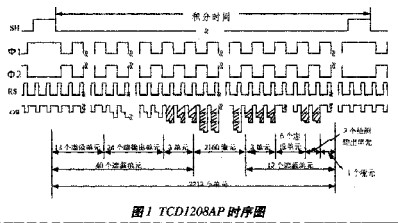

設(shè)計(jì)一種基于CPLD的可編程高精度CCD信號(hào)發(fā)生器,設(shè)計(jì)中充分利用CPLD的可編程性,模擬出滿足系統(tǒng)要求的CD信號(hào),輸出信號(hào)頻率達(dá)到1IMHZ。

2021-04-13 06:44:36

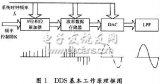

本文在討論DDS的基礎(chǔ)上,介紹利用FPGA設(shè)計(jì)的基于DDS的信號(hào)發(fā)生器。

2021-05-06 09:54:10

怎么實(shí)現(xiàn)信號(hào)發(fā)生器系統(tǒng)的FPGA設(shè)計(jì)?

2021-09-30 06:35:31

)。DDS是開(kāi)環(huán)系統(tǒng),無(wú)反饋環(huán)節(jié),輸出響應(yīng)速度快,頻率穩(wěn)定度高。因此直接數(shù)字頻率合成技術(shù)是目前頻率合成的主要技術(shù)之一。文中的主要內(nèi)容是采用FPGA結(jié)合虛擬儀器技術(shù),進(jìn)行DDS信號(hào)發(fā)生器的開(kāi)發(fā)。

2019-09-29 08:08:12

怎樣去設(shè)計(jì)一種基于FPGA的正弦信號(hào)發(fā)生器?如何對(duì)基于FPGA的正弦信號(hào)發(fā)生器進(jìn)行仿真?

2021-09-28 06:31:34

CD 1501D CCD工作參數(shù)及時(shí)序分析基于FPGA的線陣CCD驅(qū)動(dòng)時(shí)序及模擬信號(hào)處理的設(shè)計(jì)

2021-04-22 06:13:19

科學(xué)級(jí)相機(jī)是專門用于科學(xué)領(lǐng)域應(yīng)用的專用相機(jī),雖然都是CCD作為光的基本接收器件,但是CCD本身是不同級(jí)別的。根據(jù)科學(xué)實(shí)驗(yàn)的要求:需要高靈敏度的,低噪聲的,高速度的,不同冷卻溫度的,我們要提供

2014-04-29 15:11:22

清晰程度的分辨率、決定圖像采集能力的動(dòng)態(tài)范圍、與靈敏度以及分辨率等眾多參數(shù)有著密切關(guān)聯(lián)的噪聲、表示光電信號(hào)轉(zhuǎn)換效率的量子效率以及決定像素之間響應(yīng)度的線性度等。那么,在為科研領(lǐng)域選擇合適的科學(xué)級(jí)相機(jī)時(shí)

2014-03-26 15:25:46

相位需要調(diào)整的RΦ2HV, 用以滿足CCD97 增益寄存器轉(zhuǎn)移過(guò)程中的嚴(yán)格時(shí)序要求。 在FPGA 時(shí)序發(fā)生設(shè)計(jì)中, 依照CCD97 工作的流程, 進(jìn)行逆序設(shè)計(jì)。從最高頻率的像素移位讀出時(shí)鐘到行轉(zhuǎn)移

2018-11-13 11:13:20

詳細(xì)介紹紫金山天文臺(tái)紅外實(shí)驗(yàn)室開(kāi)發(fā)的CCD 相機(jī)系統(tǒng)的軟硬件設(shè)計(jì)。根據(jù)柯達(dá)CCD 芯片KAF-0401LE 的時(shí)序要求, 用復(fù)雜可編程邏輯器件(CPLD)實(shí)現(xiàn)了CCD 的時(shí)序;采用相關(guān)雙采樣技術(shù)降低

2009-05-14 16:07:46 36

36 采用IL2E2 TDI CCD 做為傳感器,與計(jì)算機(jī)構(gòu)成了成像系統(tǒng),并在計(jì)算機(jī)CRT 上顯示出圖像。主要介紹高速CCD 相機(jī)的工作時(shí)鐘產(chǎn)生電路的設(shè)計(jì),采用大規(guī)模集成電路FPGA 實(shí)現(xiàn)了該工作時(shí)鐘驅(qū)動(dòng)

2009-07-04 16:02:55 44

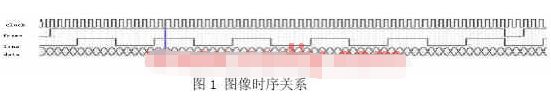

44 本文介紹了一種基于FPGA 的圖像目標(biāo)發(fā)生器的設(shè)計(jì)方法,介紹了它的設(shè)計(jì)原理、硬件電路結(jié)構(gòu)、各功能的實(shí)現(xiàn)方法。該圖像發(fā)生器能產(chǎn)生灰度階圖像、靜態(tài)目標(biāo)圖像和運(yùn)動(dòng)目標(biāo)

2009-09-02 11:16:55 27

27 本實(shí)驗(yàn)是基于EasyFPGA030的波形發(fā)生器設(shè)計(jì),用EasyFPGA030開(kāi)發(fā)套件實(shí)現(xiàn)頻率可以受按鍵控制調(diào)節(jié)的,矩形波和三角波發(fā)生器。 本設(shè)計(jì)通過(guò)DAC0832和LM358來(lái)實(shí)現(xiàn)數(shù)模轉(zhuǎn)換,8位的變化的數(shù)字

2009-11-02 17:06:45 389

389 為了降低科學(xué)級(jí)CCD 相機(jī)的噪聲,提高相機(jī)的成像質(zhì)量,針對(duì)不同的噪聲源,根據(jù)相應(yīng)的噪聲產(chǎn)生原理,設(shè)計(jì)了實(shí)用的噪聲抑制電路和處理電路。,應(yīng)用于選用ISD029AP型CCD 圖像傳感器自己開(kāi)

2009-12-16 15:01:44 20

20 本文介紹基于FPGA 和DDFS 技術(shù),應(yīng)用Altera 公司的FPGA 開(kāi)發(fā)工具DSP Builder 設(shè)計(jì)數(shù)字移相信號(hào)發(fā)生器,該數(shù)字移相信號(hào)發(fā)生器的頻率、相位、幅度均可預(yù)置,分辨率高,精確可調(diào)。且可分

2009-12-18 11:59:54 44

44 根據(jù)直接數(shù)字合成器的基本原理,給出了基于FPGA 的直接數(shù)字合成器的設(shè)計(jì)與實(shí)現(xiàn),利用FPGA有效地?cái)U(kuò)展了輸出波形的頻率范圍,實(shí)現(xiàn)了數(shù)字移相信號(hào)發(fā)生器。該信號(hào)發(fā)器主要采用了

2009-12-26 16:34:58 36

36 在分析了Sarnoff 公司的VCCD512H 面陣型CCD 圖像傳感器驅(qū)動(dòng)時(shí)序關(guān)系的基礎(chǔ)上,結(jié)合某CCD 相機(jī)電子系統(tǒng)的總體要求,完成了基于FPGA 驅(qū)動(dòng)時(shí)序發(fā)生器與數(shù)據(jù)緩存器的一體化設(shè)計(jì)。選用X

2010-01-06 15:23:12 36

36 為解決TDI-CCD 作為遙感相機(jī)的圖像傳感器在使用中所面臨的時(shí)序電路設(shè)計(jì)問(wèn)題,文中較為詳細(xì)地介紹了TDI-CCD 的結(jié)構(gòu)和工作原理,并根據(jù)工程項(xiàng)目所使用的ILE2TDI-CCD 的特性,設(shè)

2010-01-12 09:54:50 22

22 本實(shí)驗(yàn)是基于EasyFPGA030的波形發(fā)生器設(shè)計(jì),用EasyFPGA030開(kāi)發(fā)套件實(shí)現(xiàn)頻率可以受按鍵控制調(diào)節(jié)的,矩形波和三角波發(fā)生器。

2010-03-11 15:35:15 61

61 根據(jù)直接數(shù)字合成器的基本原理,給出了基于FPGA的直接數(shù)字合成器的設(shè)計(jì)與實(shí)現(xiàn),利用FPGA有效地?cái)U(kuò)展了輸出波形的頻率范圍,實(shí)現(xiàn)了數(shù)字移相信號(hào)發(fā)生器。該信號(hào)發(fā)生器主要采用了直接

2010-07-21 17:30:47 69

69

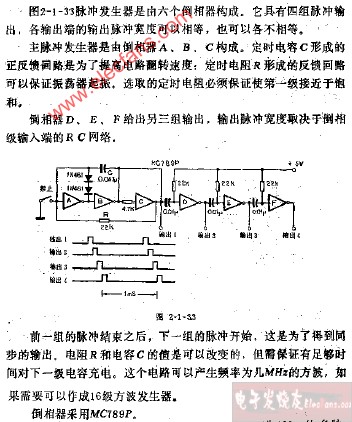

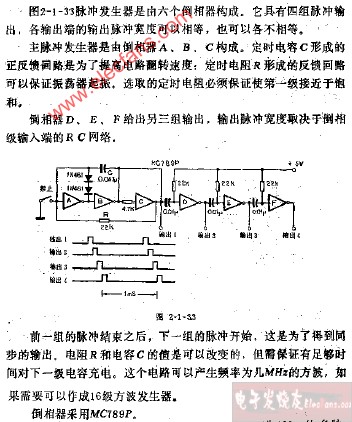

多路時(shí)序脈沖發(fā)生器

2009-03-23 09:54:16 703

703

基于LabVIEW的多路時(shí)序控制脈沖發(fā)生器設(shè)計(jì)

0 引 言

在過(guò)程控制和自動(dòng)測(cè)量中,經(jīng)常需要一些時(shí)序控制脈沖來(lái)觸發(fā)和關(guān)閉不同的控制單元和功能部件的工作。

2009-12-02 11:31:20 4366

4366 采用ML2035的簡(jiǎn)易正弦信號(hào)發(fā)生器應(yīng)用設(shè)計(jì)

摘要:在電子和通信產(chǎn)品中往往需要高精度的正弦信號(hào),而傳統(tǒng)的正弦信號(hào)發(fā)生器往往在低頻輸出時(shí)

2009-12-29 11:39:05 4024

4024

本文設(shè)計(jì)了一種基于CPLD的可編程高精度CCD信號(hào)發(fā)生器。充分利用CPLD的可編程性.模擬出滿足系統(tǒng)要求的CD信號(hào),輸出信號(hào)頻率

2010-06-19 11:14:45 1173

1173

要求改變脈沖周期和輸出脈沖個(gè)數(shù)的脈沖輸出電路模塊在許多工業(yè)領(lǐng)域都有運(yùn)用。采用數(shù)字器件設(shè)計(jì)周期和輸出個(gè)數(shù)可調(diào)節(jié)的脈沖發(fā)生模塊是方便可行的。為了使之具有高速、靈活的優(yōu)點(diǎn),本文采用atelra公司的可編程芯片FPGA設(shè)計(jì)了一款周期和輸出個(gè)數(shù)可變的脈沖發(fā)生器

2011-01-20 13:40:28 6772

6772

捅要:為了實(shí)現(xiàn)是彈武器瞄準(zhǔn)自動(dòng)化,本文設(shè)計(jì)了基于DSP和FPGA的高速高精確度雙通道CCD圖像采集系統(tǒng),采用QUartuBn在AJtera的FPGA器件CYCLONEII上設(shè)計(jì)了CCD驅(qū)動(dòng)時(shí)序電路,采用PsPICE設(shè)計(jì)了可以

2011-02-25 13:48:05 190

190 FPGA實(shí)現(xiàn)智能函數(shù)發(fā)生器設(shè)計(jì)介紹了一種基于 FPGA 的智能函數(shù)發(fā)生器的設(shè)計(jì).采用EDA技術(shù)對(duì)此設(shè)計(jì)進(jìn)行功能仿真和時(shí)序仿真,在EDA/SOPC系統(tǒng)開(kāi)發(fā)平臺(tái)上實(shí)現(xiàn)程序下載,同時(shí)在示波器上觀察波形

2011-07-25 11:00:53 56

56 函數(shù)信號(hào)發(fā)生器的實(shí)現(xiàn)方法通常是采用分立元件或單片專用集成芯片,但其頻率不高,穩(wěn)定性較差,且不易調(diào)試,開(kāi)發(fā)和使用上都受到較大限制。隨著可編程邏輯器件(FPGA)的不斷發(fā)展,

2011-09-19 17:08:53 33604

33604

以FPGA 芯片為載體, 通過(guò)QuartusII 的LPM_ROM 模塊和VHDL 語(yǔ)言為核心設(shè)計(jì)一個(gè)多功能信號(hào)發(fā)生器,根據(jù)輸入信號(hào)的選擇可以輸出遞增鋸齒波、遞減鋸齒波、三角波、階梯波和方波等5 種信號(hào),

2011-09-26 14:05:54 9165

9165

為了降低傳統(tǒng)函數(shù)信號(hào)發(fā)生器成本,改善函數(shù)信號(hào)發(fā)生器低頻穩(wěn)定性,本文結(jié)合FPGA和51單片機(jī)設(shè)計(jì)并實(shí)現(xiàn)了產(chǎn)生以0.596Hz頻率精度各種函數(shù)信號(hào)。函數(shù)信號(hào)頻率、波形、幅度由51單片機(jī)控

2012-03-22 12:08:01 125

125 設(shè)計(jì)采用Altera公司CycloneII系列EP2C5Q208作為核心器件,采用直接數(shù)字頻率合成技術(shù)實(shí)現(xiàn)了一個(gè)頻率、相位可控的基本信號(hào)發(fā)生器。該信號(hào)發(fā)生器可以產(chǎn)生正弦波、方波、三角波和鋸齒波四種波形。仿真及硬件驗(yàn)證的結(jié)果表明,該信號(hào)發(fā)生器精度高,抗干擾性好,此設(shè)計(jì)方案具有一定的實(shí)用性。

2013-01-22 14:45:33 472

472 為了提高數(shù)字調(diào)制信號(hào)發(fā)生器的頻率準(zhǔn)確度和穩(wěn)定度,并使其相關(guān)技術(shù)參數(shù)靈活可調(diào),提出了基于FPGA和DDS技術(shù)的數(shù)字調(diào)制信號(hào)發(fā)生器設(shè)計(jì)方法。利用Matlab/Simulink、DSP Builder、QuartusⅡ 3個(gè)

2013-04-27 16:50:59 183

183 基于FPGA的正弦信號(hào)發(fā)生器的 技術(shù)論文

2015-10-30 10:39:05 21

21 基于FPGA的多功能圖像目標(biāo)發(fā)生器的設(shè)計(jì)與實(shí)現(xiàn)

2016-08-30 15:10:14 6

6 波形發(fā)生器

2017-08-11 08:33:25 14

14 FPGA和51單片機(jī)信號(hào)發(fā)生器設(shè)計(jì)

2017-10-31 09:15:37 22

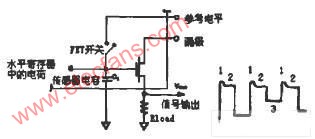

22 基于運(yùn)放的信號(hào)發(fā)生器精度低且穩(wěn)定性和可調(diào)節(jié)性差,而基于DDS的信號(hào)發(fā)生器則成本高、電路復(fù)雜。為此提出了基于FPGA+PWM的多路信號(hào)發(fā)生器設(shè)計(jì)方法。該方法硬件上無(wú)需DAC與多路模擬開(kāi)關(guān),由FPGA產(chǎn)生調(diào)制輸出波形信號(hào)所需的PWM脈沖波,經(jīng)二階低通濾波和放大電路后即可得到所需波形信號(hào)。

2017-11-18 09:42:01 7556

7556

針對(duì)面陣CCD KAI-1020 在高幀頻工作模式下的驅(qū)動(dòng)要求,以FPGA 作為控制單元及時(shí)序發(fā)生器,完成CCD 高幀頻工作模式下的硬件及軟件設(shè)計(jì),仿真驗(yàn)證了驅(qū)動(dòng)時(shí)序的正確性,完成了硬件電路的調(diào)試

2017-11-18 13:07:01 2739

2739

將虛擬儀器技術(shù)同FPGA技術(shù)結(jié)合,設(shè)計(jì)了一個(gè)頻率可控的DDS任意波形信號(hào)發(fā)生器。在闡述直接數(shù)字頻率合成技術(shù)的工作原理、電路構(gòu)成的基礎(chǔ)上,分別介紹了上位機(jī)虛擬儀器監(jiān)控面板的功能和結(jié)構(gòu),以及實(shí)現(xiàn)DDS

2017-12-04 11:40:09 33

33 本文檔內(nèi)容介紹了基于fpga實(shí)現(xiàn)信號(hào)發(fā)生器,供參考

2018-04-20 15:23:35 71

71 在分析了SONY ICX415AL行間轉(zhuǎn)移型面陣CCD的驅(qū)動(dòng)時(shí)序的基礎(chǔ)之上,提出了基于FPGA的驅(qū)動(dòng)時(shí)序發(fā)生器的設(shè)計(jì)方案,并使用VHDL語(yǔ)言實(shí)現(xiàn)了該設(shè)計(jì)方案。整個(gè)設(shè)計(jì)充分結(jié)合了FPGA器件的設(shè)計(jì)簡(jiǎn)單

2018-05-22 10:21:00 3841

3841

CCD驅(qū)動(dòng)電路的設(shè)計(jì)是CCD應(yīng)用的關(guān)鍵問(wèn)題之一。由于不同廠家生產(chǎn)的CCD的驅(qū)動(dòng)時(shí)序不盡相同,同一廠家不同型號(hào)的CCD驅(qū)動(dòng)時(shí)序也不完全一樣,因此CCD用戶必須面對(duì)驅(qū)動(dòng)電路的設(shè)計(jì)問(wèn)題。以往采用不同功能的數(shù)字芯片搭成的驅(qū)動(dòng)電路,調(diào)試?yán)щy,靈活性較差。

2019-06-04 08:03:00 3649

3649

針對(duì)信號(hào)發(fā)生器對(duì)輸出頻率精度高和幅值可調(diào)的要求,采用直接數(shù)字頻率合成(DDS)技術(shù),提出一種基于FPGA的幅值、頻率均可調(diào)的、高分辨率、高穩(wěn)定度的信號(hào)發(fā)生器設(shè)計(jì)方案。采用AT89S52單片機(jī)為控制器

2018-11-06 19:35:28 21

21 的面陣CCD驅(qū)動(dòng)時(shí)序發(fā)生器設(shè)計(jì),基于CPLD的面陣CCD驅(qū)動(dòng)時(shí)序發(fā)生器設(shè)計(jì)及其硬件實(shí)現(xiàn),基于CPLD的線陣CCD驅(qū)動(dòng)電路的設(shè)計(jì),基于CPLD的線陣CCD驅(qū)動(dòng)電路設(shè)計(jì)與實(shí)現(xiàn),基于CPLD的線陣CCD驅(qū)動(dòng)

2019-05-16 08:00:00 16

16 設(shè)計(jì)出高幀頻的成像系統(tǒng),以及能否實(shí)現(xiàn)兩個(gè)CCD相機(jī)的同步采集。CCD工業(yè)相機(jī)的關(guān)鍵技術(shù)在于CCD驅(qū)動(dòng)傳輸電路的設(shè)計(jì),為了在實(shí)踐中解決這兩個(gè)問(wèn)題,本文對(duì)CCD芯片的驅(qū)動(dòng)脈沖和時(shí)序關(guān)系進(jìn)行了詳細(xì)的分析,設(shè)計(jì)出了基于FPGA的CCD驅(qū)動(dòng)傳輸電路。

2019-11-26 15:35:15 27

27 本文在介紹了CCO工作原理、分析了CCD輸出信號(hào)中混有的芥種噪聲的基礎(chǔ)上,提出幾種產(chǎn)生CCD驅(qū)動(dòng)時(shí)序方法,重點(diǎn)介紹了選用FGPA(現(xiàn)場(chǎng)可編程邏輯門陣列)來(lái)作為時(shí)序發(fā)生器的優(yōu)點(diǎn),并講解了采用原理圖

2019-12-06 15:36:00 25

25 研制了基于現(xiàn)場(chǎng)可編程門陣列 (FPGA)實(shí)現(xiàn)的、用于± 50 0 kvar靜止補(bǔ)償器 (STATCOM)的 PWM脈沖發(fā)生器。該脈沖發(fā)生器通過(guò)接口單元接收 DSP寫(xiě)入的 PWM脈沖寬度數(shù)據(jù) ,然后

2020-01-07 11:15:43 24

24 科學(xué)級(jí)CCD相機(jī)(Scientific grade CCD camera)是一種具有低噪聲、高靈敏度、大動(dòng)態(tài)范圍和高量子效率等優(yōu)良性能的CCD相機(jī),用于對(duì)微光信號(hào)檢測(cè)和微光成像。它在射線數(shù)字成像檢測(cè)、生物醫(yī)學(xué)工程、水下攝影、武器裝備、天文觀測(cè)、空間對(duì)地觀測(cè)等多種技術(shù)領(lǐng)域得到了廣泛應(yīng)用。

2020-08-06 17:21:18 1768

1768

在CCD圖像采集中,需要對(duì)圖像采集系統(tǒng)的性能進(jìn)行評(píng)估,而由于CCD相機(jī)的研制時(shí)間長(zhǎng),研制成本高,并且不易于控制,因此,研制出開(kāi)發(fā)周期短、易于控制的圖像目標(biāo)發(fā)生器成為評(píng)估圖像采集系統(tǒng)中很重要的一步。

2020-08-10 18:01:07 1032

1032

設(shè)計(jì)平臺(tái),使用VHDL語(yǔ)言對(duì)驅(qū)動(dòng)時(shí)序發(fā)生器進(jìn)行了硬件描述,采用QuartusⅡ5.0對(duì)所設(shè)計(jì)的驅(qū)動(dòng)時(shí)序發(fā)生器進(jìn)行了仿真,針對(duì)Altera公司的FPGA器件EP1C3T144C8進(jìn)行了適配。實(shí)驗(yàn)結(jié)果表明,設(shè)計(jì)的驅(qū)動(dòng)電路可以滿足其全幀CCD的各項(xiàng)驅(qū)動(dòng)要求并且具有設(shè)計(jì)靈活,硬件調(diào)試簡(jiǎn)單的優(yōu)點(diǎn).

2021-01-26 15:57:01 12

12 本文介紹了一種基于FPGA的圖像目標(biāo)發(fā)生器的設(shè)計(jì)方法,介紹了它的設(shè)計(jì)原理、硬件電路結(jié)構(gòu)、各功能的實(shí)現(xiàn)方法。該圖像發(fā)生器能產(chǎn)生灰度階圖像、靜態(tài)目標(biāo)圖像和運(yùn)動(dòng)目標(biāo)圖像,用來(lái)對(duì)圖像采集系統(tǒng)進(jìn)行評(píng)估。

2021-01-26 15:57:03 7

7 本文根據(jù)單峰映射產(chǎn)生混沌序列極易被攻擊的特點(diǎn),采用髙維的混沌系統(tǒng)來(lái)設(shè)計(jì)混沌跳頻序列發(fā)生器。針對(duì)n維非線性數(shù)字濾波器產(chǎn)生序列的周期和分布特性,我們?cè)谙到y(tǒng)結(jié)構(gòu)上作了相應(yīng)的設(shè)計(jì),并最終應(yīng)用FPGA(現(xiàn)場(chǎng)

2021-02-02 15:14:55 11

11 AD9923A: CCD 信號(hào)處理器,內(nèi)置垂直驅(qū)動(dòng)器和Precision Timing發(fā)生器 數(shù)據(jù)手冊(cè)

2021-03-19 06:53:40 1

1 的設(shè)計(jì)變得相對(duì)簡(jiǎn)單而且高效。本文采用Altera Cyclone ||系列FPGA 實(shí)現(xiàn)可選擇音頻發(fā)生器,以實(shí)現(xiàn)聲樂(lè)中的幾種不同頻率的聲音。

2021-03-19 09:40:42 3888

3888

AD9992:帶精確定時(shí)發(fā)生器數(shù)據(jù)表的12位CCD信號(hào)處理器

2021-04-15 11:26:57 1

1 AD9991:帶精確定時(shí)發(fā)生器數(shù)據(jù)表的10位CCD信號(hào)處理器

2021-04-15 11:43:59 0

0 AD9891/AD9895:帶精密時(shí)序發(fā)生器的CCD信號(hào)處理器數(shù)據(jù)表

2021-04-16 10:02:05 0

0 AD9937:帶精確定時(shí)發(fā)生器的CCD信號(hào)處理器數(shù)據(jù)表

2021-04-16 10:40:50 8

8 AD9898:帶精確定時(shí)?發(fā)生器的CCD信號(hào)處理器數(shù)據(jù)表

2021-04-19 11:20:16 21

21 AD9929:帶精確定時(shí)發(fā)生器的CCD信號(hào)處理器數(shù)據(jù)表

2021-04-20 11:41:32 5

5 ADDI9020:帶V驅(qū)動(dòng)器和精密時(shí)序發(fā)生器的60 MHz CCD信號(hào)處理器數(shù)據(jù)表

2021-05-08 18:50:37 3

3 AD9970:帶精確定時(shí)?發(fā)生器的14位CCD信號(hào)處理器數(shù)據(jù)表

2021-05-09 11:09:15 10

10 基于FPGA的偽隨機(jī)數(shù)發(fā)生器設(shè)計(jì)方案

2021-06-28 14:36:49 4

4 FPGA實(shí)現(xiàn)基于ROM的正弦波發(fā)生器(嵌入式開(kāi)發(fā)系統(tǒng))-該文檔為FPGA實(shí)現(xiàn)基于ROM的正弦波發(fā)生器總結(jié)文檔,是一份很不錯(cuò)的參考資料,具有較高參考價(jià)值,感興趣的可以下載看看………………

2021-07-30 11:45:41 32

32 基于FPGA和DAC設(shè)計(jì)的dds發(fā)生器(普德新星電源技術(shù)有限公司的LoGo)-該文檔為基于FPGA和DAC設(shè)計(jì)的dds發(fā)生器總結(jié)文檔,是一份很不錯(cuò)的參考資料,具有較高參考價(jià)值,感興趣的可以下載看看………………

2021-09-16 12:09:10 42

42 脈沖發(fā)生器: 顧名思義,脈沖發(fā)生器是一種產(chǎn)生脈沖的信號(hào)發(fā)生器。這些信號(hào)發(fā)生器通常采用邏輯脈沖發(fā)生器的形式,可以產(chǎn)生具有可變延遲的脈沖,有些甚至提供可變上升和下降時(shí)間。

2022-08-02 15:48:42 5860

5860 變化過(guò)程。搭配微距鏡頭物方分辨率可達(dá)3μm。 MAG-F7科學(xué)級(jí)中波制冷型熱像儀 MAG-F7科學(xué)級(jí)中波制冷型熱像儀采用640×512 InSb紅外探測(cè)器,內(nèi)部集成200萬(wàn)像素可見(jiàn)光相機(jī),可多光譜同步觀測(cè)記錄,支持高精度同步模式,可用于鎖相檢測(cè)。 MAG-F7科學(xué)級(jí)中波制冷型熱

2022-11-04 13:24:50 966

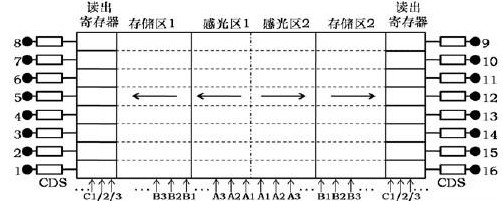

966 Interline CCD 圖像傳感器的垂直時(shí)序優(yōu)化

2022-11-15 20:36:34 3

3 本設(shè)計(jì)以FPGA為控制核心,采用直接數(shù)字頻率合成(DDS)設(shè)計(jì)了一款信號(hào)可調(diào)的信號(hào)發(fā)生器,采用的FPGA是Altera公司研發(fā)的的Cyclnoe II系列,所選用的型號(hào)是EP4C6F17C8,外圍

2022-12-22 11:08:05 9

9 ?基于運(yùn)用EDA技術(shù),以FPGA器件為,用Verilog HDL硬件描述語(yǔ)言來(lái)設(shè)計(jì)各個(gè)功能模塊,采用DDS直接數(shù)字頻率合成技術(shù)設(shè)計(jì)信號(hào)發(fā)生器,通過(guò)CPU控制每個(gè)采樣點(diǎn)的輸出間隔來(lái)控制輸出波形的頻率

2023-04-14 15:15:02 1904

1904 電子發(fā)燒友網(wǎng)站提供《GPS C/A碼發(fā)生器的仿真研究與FPGA設(shè)計(jì).pdf》資料免費(fèi)下載

2023-11-06 14:17:54 0

0 CCD是“電荷耦合器件”(Charge-Coupled Device)的縮寫(xiě),是一種常用的圖像傳感器技術(shù),廣泛應(yīng)用于數(shù)碼相機(jī)、攝像機(jī)、掃描儀、天文望遠(yuǎn)鏡等領(lǐng)域。本文將從CCD的原理、結(jié)構(gòu)、工作方式

2024-01-10 15:27:40 8233

8233 電子發(fā)燒友網(wǎng)站提供《基于FPGA 的DDS正弦信號(hào)發(fā)生器的設(shè)計(jì)和實(shí)現(xiàn).pdf》資料免費(fèi)下載

2024-03-24 09:34:50 10

10 了改進(jìn),CCD技術(shù)被超越,成為消費(fèi)類數(shù)碼相機(jī)的首選傳感器。該技術(shù)隨后得到進(jìn)一步改進(jìn),以滿足科學(xué)成像所必需的更高要求。 CMOS傳感器技術(shù)與CCD傳感器的不同之處在于,CMOS傳感器不像CCD傳感器那樣將所有傳感器像素都通過(guò)一個(gè)輸出節(jié)點(diǎn)、一個(gè)放大器和一個(gè)模數(shù)轉(zhuǎn)換器(ADC)饋送,而是

2024-03-25 06:32:13 3665

3665

在提供適合客戶需求的科學(xué)相機(jī)時(shí),傳統(tǒng)趨勢(shì)是使用超靈敏 EM-CCD(電子倍增 CCD)相機(jī)在極低光照區(qū)域進(jìn)行測(cè)量,以及大像素?cái)?shù)的 sCMOS(科學(xué) CMOS)相機(jī),在相對(duì)明亮的區(qū)域具有高速度和高動(dòng)態(tài)

2024-03-26 10:26:19 1538

1538

基于FPGA的CCD工業(yè)相機(jī)系統(tǒng)設(shè)計(jì)是一個(gè)綜合性的項(xiàng)目,它結(jié)合了硬件電路設(shè)計(jì)、FPGA編程以及圖像處理技術(shù)。以下是一個(gè)詳細(xì)的系統(tǒng)設(shè)計(jì)方案,包括設(shè)計(jì)概述、硬件架構(gòu)、FPGA編程要點(diǎn)以及部分關(guān)鍵代碼示例。

2024-07-17 11:24:39 2692

2692 分享如何在Xilinx Breadboardable Spartan-7 FPGA, CMOD S7中實(shí)現(xiàn)4位偽隨機(jī)數(shù)發(fā)生器(PRNGs)。

2024-08-06 11:20:47 1668

1668

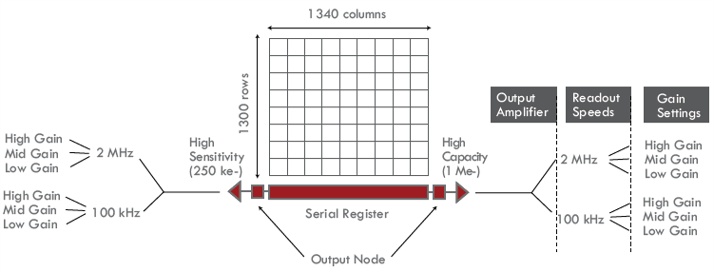

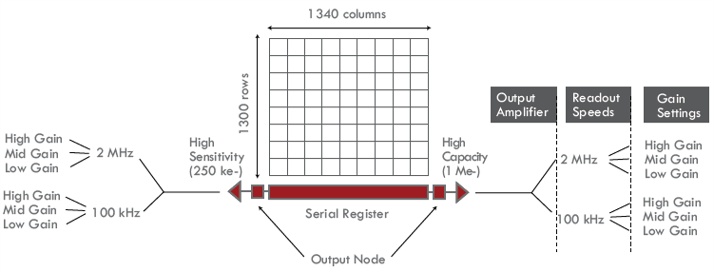

,隨著許多學(xué)科不斷發(fā)展,涵蓋了更多不同的調(diào)查技術(shù),關(guān)鍵要求也不斷擴(kuò)大。在尋找滿足各種需求的科學(xué)相機(jī)時(shí),必須確保尋找功能最豐富、性能比較高的解決方案。 本文介紹了 Teledyne Princeton Instruments 科學(xué) CCD 相機(jī)靈活的電子結(jié)構(gòu)如何擴(kuò)展應(yīng)用

2024-11-20 06:25:40 729

729

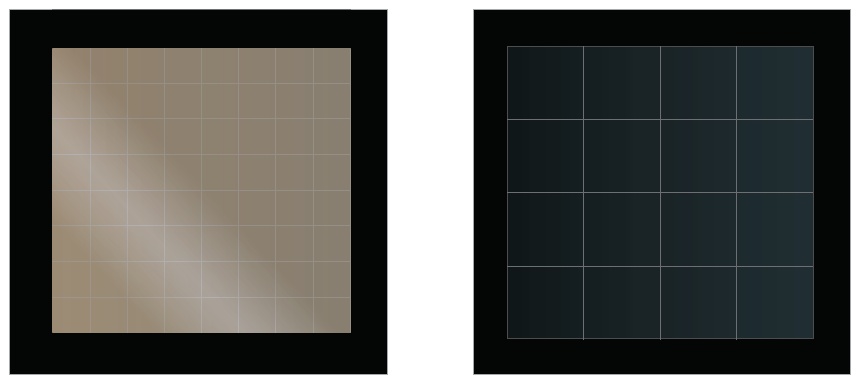

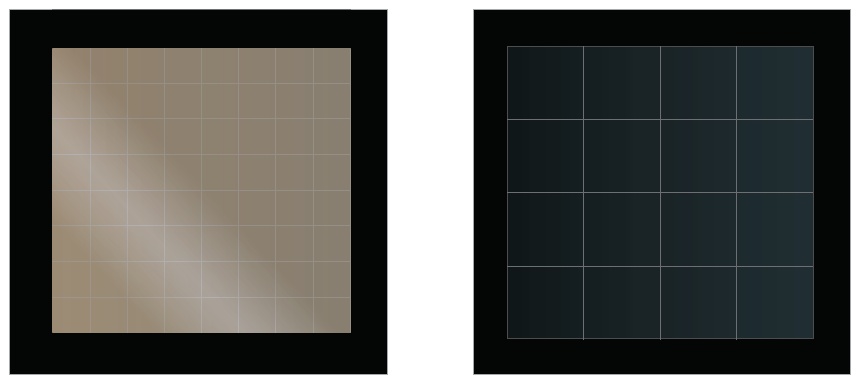

圖 1.典型的前照式 CCD/sCMOS 傳感器(左)在外觀上是反射性的,而背照式傳感器(右)則顯得較暗。 概述 微光科學(xué)相機(jī)是從量子成像到天文學(xué)等許多革命性發(fā)現(xiàn)的背后。五十多年來(lái),CCD 相機(jī)及其

2024-11-26 06:22:09 1793

1793

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論