FPGA/CPLD在數(shù)字系統(tǒng)設(shè)計中的廣泛應(yīng)用,影響到了生產(chǎn)生活的各個方面。在FPGA/CPLD的設(shè)計開發(fā)中,VHDL語言作為

2010-10-15 11:08:00 7826

7826

EDA技術(shù)徹底改變了數(shù)字系統(tǒng)的設(shè)計方法和實現(xiàn)手段,借助于硬件描述語言的國際標(biāo)準(zhǔn)VHDL 和強大的EDA工具,可減少設(shè)計風(fēng)險并縮短周期,隨著VHDL語言使用范圍的日益擴大

2011-04-11 11:34:47 2453

2453

VHDL語言基礎(chǔ)

2012-08-15 17:36:58

VHDL與其他傳統(tǒng)集成電路描述語言相比具有什么優(yōu)勢?VHDL語言為核心的EDA技術(shù)在醫(yī)學(xué)中的應(yīng)用

2021-05-07 06:38:41

VHDL硬件描述語言與和數(shù)字邏輯電路設(shè)計.侯伯亭&顧新

2020-05-11 09:22:18

VHDL硬件描述語言與和數(shù)字邏輯電路設(shè)計.侯伯亭&顧新.掃描版

2020-05-03 09:46:42

VHDL語言是一種用于電路設(shè)計的高級語言。它在80年代的后期出現(xiàn)。最初是由美國國防部開發(fā)出來供美軍用來提高設(shè)計的可靠性和縮減開發(fā)周期的一種使用范圍較小的設(shè)計語言 。VHDL翻譯成中文就是

2015-09-30 13:48:29

電路設(shè)計VHDL設(shè)計基礎(chǔ)知識,幾個文檔集合在一起的。

2016-10-08 10:32:17

Perl語言在電路設(shè)計中的應(yīng)用實用提取和報表語言是由Perl語言在電路設(shè)計中的應(yīng)用 開發(fā)并不斷更新,用于Perl語言在電路設(shè)計中的應(yīng)用 環(huán)境下編程的一種模塊化的、可擴展的高級語言。在集成電路后端

2012-01-11 15:19:01

[VHDL硬件描述語言與和數(shù)字邏輯電路設(shè)計].侯伯亭&顧新.掃描版

2020-05-21 09:25:46

求一款基于VHDL的異步串行通信電路設(shè)計分享

2021-04-08 06:16:42

電子設(shè)計的主流。VHDL語言作為可編程邏輯器件的標(biāo)準(zhǔn)語言描述能力強,覆蓋面廣,抽象能力強,應(yīng)用越來越廣泛。VHDL語言具有多層次描述系統(tǒng)硬件功能的能力,可以從系統(tǒng)的數(shù)學(xué)模型直到門級電路,其高層次的行為

2018-11-20 10:39:39

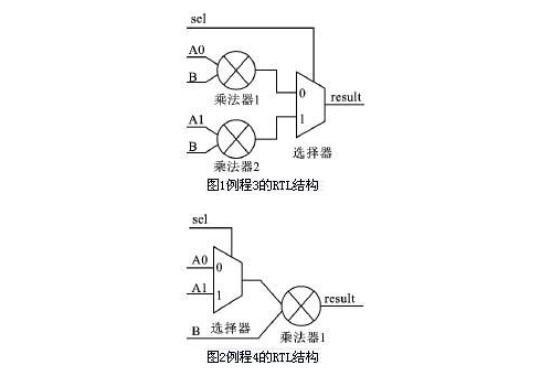

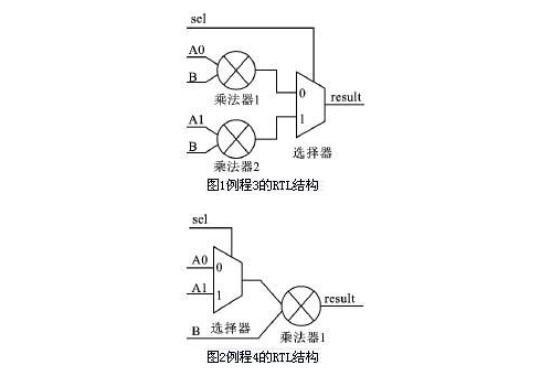

語言進行CPLD/FPGA設(shè)計開發(fā),Altera和Lattice已經(jīng)在開發(fā)軟件方面提供了基于本公司芯片的強大開發(fā)工具。但由于VHDL設(shè)計是行為級設(shè)計,所帶來的問題是設(shè)計者的設(shè)計思想與電路結(jié)構(gòu)相脫節(jié),而且

2019-06-18 07:45:03

VHDL(Very High Speed Integrated Circuit Hardware Description Language)是IEEE工業(yè)標(biāo)準(zhǔn)硬件描述語言,是隨著可編程邏輯器件(PLD)的發(fā)展而發(fā)展起來的。

2019-10-18 08:20:51

VHDL(Very High Speed Integrated Circuit Hardware Description Language)是IEEE工業(yè)標(biāo)準(zhǔn)硬件描述語言,是隨著可編程邏輯器件

2019-08-28 08:05:46

什么是VHDL?VHDL(Very High Speed Integrated Circuit Hardware Description Language)是IEEE工業(yè)標(biāo)準(zhǔn)硬件描述語言,是隨著

2019-08-08 07:08:00

感覺模擬IC設(shè)計就應(yīng)該是設(shè)計模擬電路.設(shè)計運放等,通過設(shè)計電路、在硅片上搭建TTL.CMOS......從而做成IC芯片;而我經(jīng)常看到說IC設(shè)計就是使用VHDL語言設(shè)計IC,寫好VHDL語言后燒錄到FPGA.CPLD.......從而做成芯片。我想問的是這兩者有什么區(qū)別?

2018-08-29 09:45:43

硬件描述語言VHDL課件 硬件描述語言VHDL 數(shù)字系統(tǒng)設(shè)計分為硬件設(shè)計和軟件設(shè)計, 但是隨著計算機技術(shù)、超大規(guī)模集成電路(CPLD

2008-09-11 15:47:23

用VHDL語言編出一個電壓信號源,再編出一個積分電路,放大電路,濾波電路,移相電路對這個信號源進行處理

2015-05-26 21:29:51

{:12:}誰有清華大學(xué)vhdl的電路設(shè)計的代碼PCB打樣找華強 http://www.hqpcb.com/3 樣板2天出貨

2012-10-09 23:10:36

用VHDL語言實現(xiàn)樂曲演奏電路本程序是用VHDL對《梁祝協(xié)奏曲》中《化蝶》部分的樂曲電路實現(xiàn)。

2011-08-18 10:31:53

VHDL硬件描述語言教學(xué):包括fpga講義,VHDL硬件描述語言基礎(chǔ),VHDL語言的層次化設(shè)計的教學(xué)幻燈片

2006-03-27 23:46:49 93

93 組合邏輯控制器電路設(shè)計分析

本章系統(tǒng)的討論采用MSI、LSI及VLSI通用的74系列集成芯片設(shè)計各種常用的組合邏

2007-12-18 00:03:05 149

149

VHDL的定義和功能VHDL的發(fā)展概況程序編程語言和硬件描述語言的對比引入硬件描述語言對系統(tǒng)進

2008-09-03 12:58:41 39

39

全面地介紹了VHDL硬件描述語言的基本知識和利用VHDL進行數(shù)字電路系統(tǒng)設(shè)計的方法。全書共分13章:第1-6

2008-09-11 15:45:27 1339

1339 組合邏輯電路設(shè)計一、實驗?zāi)康?. 熟悉組合邏輯電路的基本設(shè)計方法;2. 練習(xí)用門電路、譯碼器、數(shù)據(jù)選擇器設(shè)計組合邏輯電路。二、實驗設(shè)備1.

2008-09-12 16:41:23 0

0 VHDL語言及其應(yīng)用是在作者歷時七年為通信與信息系統(tǒng)、信號與信息處理專業(yè)研究生講授VHDL語言及其應(yīng)用課程的教學(xué)實踐基礎(chǔ)上編寫而成的。全書共分15章,以教授完整的VHDL語言體

2009-02-12 09:41:38 174

174 [學(xué)習(xí)要求] 掌握VHDL硬件描述語言的基本語法和源文件的結(jié)構(gòu),學(xué)會用VHDL硬件描述語言設(shè)計典型數(shù)字邏輯電路。[重點與難點]重點:VHDL語言的程序結(jié)構(gòu);VHDL語言的數(shù)據(jù)類型及數(shù)

2009-03-18 20:02:35 47

47 VHDL語言及其應(yīng)用是在作者歷時七年為通信與信息系統(tǒng)、信號與信息處理專業(yè)研究生講授VHDL語言及其應(yīng)用課程的教學(xué)實踐基礎(chǔ)上編寫而成的。全書共分15章,以教授完整的VHDL語言體

2009-07-10 17:21:44 18

18 VHDL語言及其應(yīng)用的主要內(nèi)容:第一章 硬件模型概述第二章 基本的VHDL編程語言第三章 VHDL模型的組織第四章 VHDL綜合工具第五章 VHDL應(yīng)用樣例附錄A VHDL

2009-07-20 12:06:15 0

0 VHDL語言概述:本章主要內(nèi)容:硬件描述語言(HDL)VHDL語言的特點VHDL語言的開發(fā)流程

1.1 1.1 硬件描述語言( 硬件描述語言(HDL HDL)H

2009-08-09 23:13:20 47

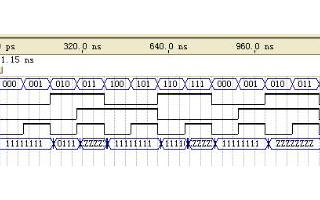

47 VHDL(超高速集成電路硬件描述語言)目前在電子設(shè)計領(lǐng)域得到了廣泛的應(yīng)用。但是,實現(xiàn)同樣的系統(tǒng)功能,不同的電路設(shè)計師可以采用不同的實際方法,這樣就存在一個電路復(fù)雜程

2009-08-13 08:27:22 20

20 本文介紹了在ALTERA 公司的EDA 軟件MAX+plusII 平臺下用VHDL 語言進行數(shù)字電路設(shè)計的主要流程,并用一個設(shè)計實例闡述演示了設(shè)計過程。關(guān)鍵詞:電子設(shè)計自動化 MAX+plusII 硬件描述

2009-08-25 14:50:32 38

38 VHDL語言描述數(shù)字系統(tǒng):本章介紹用 VHDL 描述硬件電路的一些基本手段和基本方法。 VHDL 語言是美國國防部在 20 世紀(jì) 80 年代初為實現(xiàn)其高速集成電路計劃(VHSIC)而提出的

2009-09-01 09:02:40 37

37 結(jié)合應(yīng)用MaxplusⅡ軟件進行VHDL 語言代碼編寫的經(jīng)驗,闡述使用VHDL 語言的過程中比較常見的幾個問題。

2009-09-10 16:19:24 25

25 VHDL 語言程序的元素:本章主要內(nèi)容:VHDL語言的對象VHDL語言的數(shù)據(jù)類型VHDL語言的運算符VHDL語言的標(biāo)識符VHDL語言的詞法單元

2009-09-28 14:32:21 41

41 vhdl數(shù)字系統(tǒng)設(shè)計是數(shù)字電路自動化設(shè)計(EDA)入門的工具書。其內(nèi)容主要包括:用VHDL語言設(shè)計的基本組合電路、時序電路、數(shù)字綜合電路、電路圖輸入法要領(lǐng)概述、實用VHDL語句

2009-10-08 21:54:01 0

0 VHDL硬件描述語言與數(shù)字邏輯電路設(shè)計:本書系統(tǒng)地介紹了一種硬件描述語言,即VHDL語言設(shè)計數(shù)字邏輯電路和數(shù)字系統(tǒng)的新方法。這是電子電路設(shè)計方法上一次革命性的變化,也是邁

2010-02-06 16:55:22 363

363 講述組合邏輯電路設(shè)計基礎(chǔ)

2010-05-06 10:29:15 0

0 摘要:介紹應(yīng)用高速集成電路硬件描述語言(VHDL)在Altera公司的MAX+plusII環(huán)境下,設(shè)計專用分配器和計數(shù)器。關(guān)鍵詞:VHDL;分配器;計數(shù)器

2010-05-13 09:44:11 38

38 用VHDL語言實現(xiàn)3分頻電路

標(biāo)簽/分類:

眾所周知,分頻器是FPGA設(shè)計中使用頻率非常高的基本設(shè)計之一,盡管在目前大部分設(shè)計中,廣泛使用芯片廠家集成的鎖相

2007-08-21 15:28:16 5980

5980 組合機床順序控制電路設(shè)計

一、 實驗?zāi)康模?、 熟悉常用低壓電器元件的使用。2、 掌握控制電路設(shè)計的方法

2008-09-23 08:18:48 3775

3775

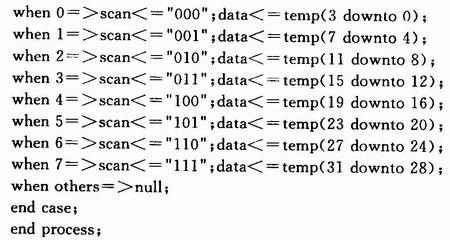

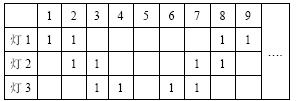

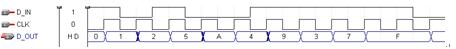

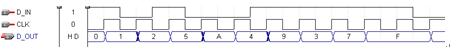

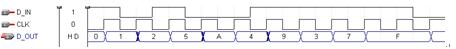

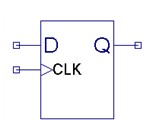

時序電路設(shè)計串入/并出移位寄存器一 實驗?zāi)康?掌握VHDL語言的基本描述語句的使用方法。2掌握使用VHDL語言進行時序電路設(shè)計的方法。

2009-03-13 19:29:51 6306

6306

時序電路設(shè)計串入/并出移位寄存器一 實驗?zāi)康?掌握VHDL語言的基本描述語句的使用方法。2掌握使用VHDL語言進行時序電路設(shè)計的方法。

2009-03-13 19:29:52 2380

2380

VHDL語言應(yīng)用實例指導(dǎo)

VHDL中的標(biāo)識符可以是常數(shù)、變量、信號、端口、子程序或參數(shù)的名字。使用標(biāo)識符要遵守如下法則

2009-03-20 14:15:53 2355

2355

【摘 要】 通過設(shè)計實例詳細(xì)介紹了用VHDL(VHSIC Hardware DescriptionLanguage)語言開發(fā)FPGA/CPLD的方法,以及與電路圖輸入和其它HDL語言相比,使用VHDL語言的優(yōu)越性。

2009-05-10 19:47:30 1437

1437

【摘 要】 介紹了在VXI總線儀器構(gòu)成的導(dǎo)彈測試系統(tǒng)中,利用ISP器件使接口電路設(shè)計簡化,并用VHDL語言實現(xiàn)了ISP器件的內(nèi)部邏輯,給出了設(shè)計的方法及部分VHDL源代碼。

2009-05-11 20:00:04 1317

1317

基于VHDL語言的智能撥號報警器的設(shè)計

介紹了以EDA技術(shù)作為開發(fā)手段的智能撥號報警系統(tǒng)的實現(xiàn)。本系統(tǒng)基于VHDL語言,采用FPGA作為控制核心,實現(xiàn)了遠(yuǎn)程防盜報警。該

2009-10-12 19:08:43 1509

1509

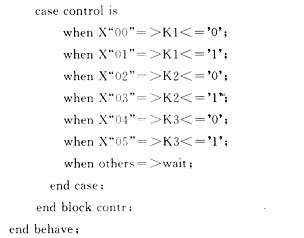

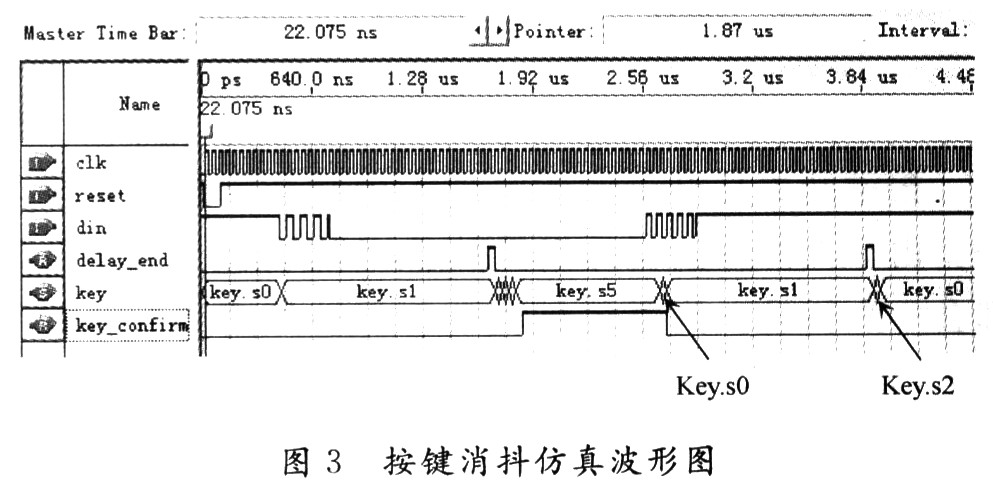

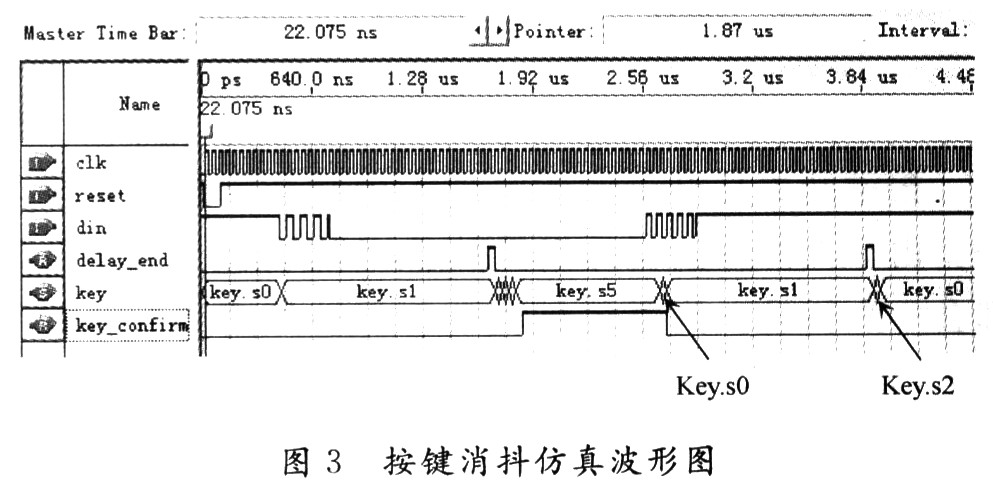

基于VHDL語言的按鍵消抖電路設(shè)計及仿真

按鍵開關(guān)是電子設(shè)備實現(xiàn)人機對話的重要器件之一。由于大部分按鍵是機械觸點,在觸點閉合和斷開時都會產(chǎn)生抖動。為避免

2010-01-04 10:39:13 6598

6598

VHDL和Verilog HDL語言對比

Verilog HDL和VHDL都是用于邏輯設(shè)計的硬件描述語言,并且都已成為IEEE標(biāo)準(zhǔn)。VHDL是在1987年成為IEEE標(biāo)準(zhǔn),Verilog HDL

2010-02-09 09:01:17 10864

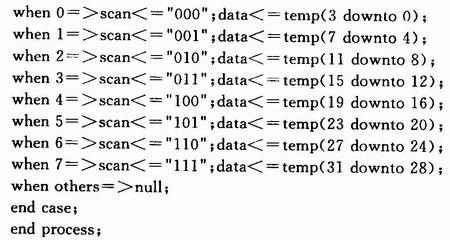

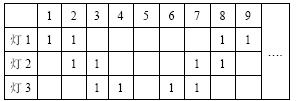

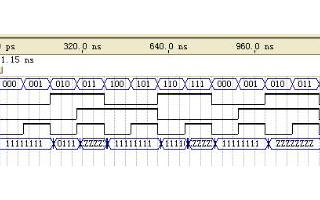

10864 采用CPLD/FPGA的VHDL語言電路優(yōu)化原理設(shè)計

VHDL(Very High Speed Integrated Circuit Hardware Description Language)是IEEE工業(yè)標(biāo)準(zhǔn)硬件描述語言,是隨著可編程邏輯器件(PLD)的發(fā)展而發(fā)展起

2010-03-19 11:38:02 2834

2834

VHDL超高速集成電路硬件描述語言是隨著集成電路系統(tǒng)化和高度集成化逐步發(fā)展起來的,是一種用于數(shù)字系統(tǒng)設(shè)計、測試,面向多領(lǐng)域、多層次的IEEE標(biāo)準(zhǔn)硬件描述語言。它從20世紀(jì)70年代作為電路設(shè)計工具誕生于美國國防部至今,已經(jīng)成為十分流行的硬件描述工具,并且

2011-01-18 12:45:17 1501

1501

本書比較系統(tǒng)地介紹了VHDL 的基本語言現(xiàn)象和實用技術(shù)全書以實用和可操作 為基點簡潔而又不失完整地介紹了VHDL 基于EDA 技術(shù)的理論與實踐方面的知識 其中包括VHDL 語句語法基礎(chǔ)知識第1 章第7 章邏輯綜合與編程技術(shù)第9 章 有限狀態(tài)機及其設(shè)計第10 章基于FPGA

2011-03-03 15:47:13 0

0 《VHDL與數(shù)字電路設(shè)計》是有盧毅、賴杰主編的,主要介紹涉及數(shù)字系統(tǒng)設(shè)計的多方面原理、技術(shù)及應(yīng)用,主要內(nèi)容有數(shù)字系統(tǒng)的基本設(shè)計思想、設(shè)計方法和設(shè)計步驟, VHDL 硬件描述語言

2011-07-11 15:54:27 0

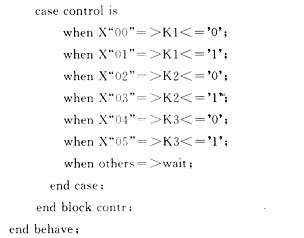

0 簡要介紹了 VHDL 語言進行工程設(shè)計的優(yōu)點,并詳細(xì)說明了利用VHDL語言設(shè)計狀態(tài)機電電路的過程,最后進行了仿真,仿真結(jié)果證明該設(shè)計能夠?qū)崿F(xiàn)狀態(tài)機電路的功能。

2011-07-18 10:31:20 84

84 VHDL(Very High Speed Integrated CIRCUITHARDWARE DESCRIPTION Language)是IEEE工業(yè)標(biāo)準(zhǔn)硬件描述語言,是隨著可編程邏輯器件(PLD)的發(fā)展而發(fā)展起來的。

2012-03-02 09:16:05 4599

4599

電子發(fā)燒友網(wǎng)站提供《[VHDL硬件描述語言與和數(shù)字邏輯電路設(shè)計].侯伯亭&顧新.掃描版.txt》資料免費下載

2012-07-10 18:32:33 0

0 電子發(fā)燒友網(wǎng)站提供《經(jīng)典教材-VHDL硬件描述語言與數(shù)字邏輯電路設(shè)計(第三版).txt》資料免費下載

2014-08-27 11:41:09 0

0 VHDL語言快速入門,很精練的語言總結(jié),希望大家有用到

2015-10-29 18:24:46 31

31 基于CPLD的VHDL語言數(shù)字鐘(含秒表)設(shè)計

2015-11-04 15:14:36 9

9 vhdl語言,第二章介紹。關(guān)于數(shù)字系統(tǒng)設(shè)計方面的知識。

2016-01-18 14:41:55 0

0 硬件描述語言VHDL簡介,好東西,喜歡的朋友可以下載來學(xué)習(xí)。

2016-02-19 17:19:50 0

0 VHDL語言在MAXPLUS軟件的設(shè)計案例,好東西,喜歡的朋友可以下載來學(xué)習(xí)。

2016-02-19 17:18:55 0

0 本書共分為三個基本組成部分,首先詳細(xì)介紹VHDL語言的背景知識、基本語法結(jié)構(gòu)和VHDL代碼的編寫方法;然后介紹VHDL電路單元庫的結(jié)構(gòu)和使用方法,以及如何將新的設(shè)計加入到現(xiàn)有的或自己新建立的單元庫中

2016-04-25 17:07:53 0

0 本書共分為三個基本組成部分,首先詳細(xì)介紹VHDL語言的背景知識、基本語法結(jié)構(gòu)和VHDL代碼的編寫方法;然后介紹VHDL電路單元庫的結(jié)構(gòu)和使用方法,以及如何將新的設(shè)計加入到現(xiàn)有的或自己新建立的單元庫中

2016-04-25 17:07:53 0

0 這本VHDL書籍,配套學(xué)習(xí)VHDL語言時從簡到難的例子,極大地幫助學(xué)習(xí)VHDL硬件編輯語言的初學(xué)者,如果是剛學(xué)完不就VHDL語言,下篇也是非常有益的例子,例子非常詳細(xì)。

2016-08-03 18:36:25 21

21 VHDL語言(修改)有需要的朋友下來看看

2016-08-05 17:32:53 24

24 VHDL語言編程學(xué)習(xí)之VHDL硬件描述語言

2016-09-01 15:27:27 0

0 硬件描述語言VHDL的學(xué)習(xí)文檔,詳細(xì)的介紹了VHDL

2016-09-02 17:00:53 12

12 VHDL語言要素,大學(xué)EDA課程必備資料,在實際的應(yīng)用中,VHDL仿真器講INTEGER類型的數(shù)據(jù)作為有符號數(shù)處理,而綜合器將INTEGER作為無符號數(shù)處理. VHDL綜合器要求利用RANGE子句為

2016-11-21 15:40:34 0

0 VHDL硬件描述語言與數(shù)字邏輯電路設(shè)計,感興趣的小伙伴們可以瞧一瞧。

2016-11-10 14:20:34 0

0 電子設(shè)計研發(fā)部分的研發(fā)人員常用資料——VHDL語言的LCD12864。

2016-11-03 14:26:19 0

0 VHDL在顯示屏控制電路設(shè)計中的應(yīng)用

2017-01-02 17:27:10 4

4 在小規(guī)模數(shù)字集成電路就要淘汰的今天,作為一個電類專業(yè)的畢業(yè)生應(yīng)該熟悉VHDL語言和CPLD、FPGA器件的設(shè)計,閻石教授新編寫的教材也加入了VHDL語言方面的內(nèi)容,可見使用VHDL語言將數(shù)字系統(tǒng)集成

2017-12-05 09:00:31 20

20 1987年, VHDL被正式確定為IEEE 1076標(biāo)準(zhǔn)。 VHDL是一種強類型語言, 具有豐富的表達(dá)能力, 可使各種復(fù)雜度(系統(tǒng)級、 電路板級、 芯片級、 門級)的電路網(wǎng)絡(luò)在同一抽象程度上被描述

2018-03-30 11:20:15 9

9 VHDL語言是一種在EDA設(shè)計中廣泛流行的硬件描述語言,主要用于描述數(shù)字系統(tǒng)的結(jié)構(gòu)、行為、功能和接口。除了含有許多具有硬件特征的語句外,VHDL語言的句法、語言形式和描述風(fēng)格十分類似于一般的計算機高級語言,是目前硬件描述語言中應(yīng)用最為廣泛的一種。

2018-03-30 16:04:27 21

21 基于VHDL的串口RS232電路設(shè)計 隨著電子技術(shù)的發(fā)展,現(xiàn)場可編程門陣列 FPGA和復(fù)雜可編程邏輯器件CPLD的出現(xiàn),使得電子系統(tǒng)的設(shè)計者利用與器件相應(yīng)的電子CAD軟件,在實驗室里就可以設(shè)計自己的專用集成電路ASIC器件。

2018-06-25 09:03:00 2397

2397

本文檔的主要內(nèi)容詳細(xì)介紹的是VHDL教程之VHDL語言元素的詳細(xì)資料概述一內(nèi)容包括了:1. VHDL語言的客體2 VHDL語言的數(shù)據(jù)類型3 VHDL數(shù)據(jù)類型轉(zhuǎn)換4 VHDL詞法規(guī)則與標(biāo)識符

2018-11-05 08:00:00 0

0 本文檔的主要內(nèi)容詳細(xì)介紹的是VHDL硬件描述語言入門教程資料免費下載包括了:1. VHDL語言基礎(chǔ),2. VHDL基本結(jié)構(gòu),3. VHDL語句,4. 狀態(tài)機在VHDL中的實現(xiàn),5. 常用電路VHDL程序,6. VHDL仿真,7. VHDL綜合

2019-04-08 08:00:00 54

54 本文檔的主要內(nèi)容詳細(xì)介紹的是使用VHDL語言設(shè)計的音樂播放盒資料合集免費下載含有電路圖與源程序。

2019-06-03 08:00:00 6

6 VHDL是一種用來描述數(shù)字邏輯系統(tǒng)的“編程語言”。它通過對硬件行為的直接描述來實現(xiàn)對硬件的物理實現(xiàn),代表了當(dāng)今硬件設(shè)計的發(fā)展方向。VHDL是為了滿足邏輯設(shè)計過程中的各種需求而設(shè)計的。

2020-04-23 15:51:03 3421

3421

什么是vhdl語言 VHDL 的英文全名是VHSIC Hardware Description Language(VHSIC硬件描述語言)。VHSIC是Very High Speed

2020-04-23 15:58:49 13149

13149 VHDL電路設(shè)計的優(yōu)化與VHDL描述語句、EDA工具以及可編程器件(PLD)的選用都有著直接的關(guān)系。

2020-07-16 08:46:03 3181

3181

VHDL語言由于其其強大的行為描述能力及與硬件行為無關(guān)的特性,被廣泛的用于數(shù)字系統(tǒng)設(shè)計,實現(xiàn)了硬件電路設(shè)計的軟件化,成為實現(xiàn)Petri網(wǎng)邏輯控制器的有力的工具。用VHDL語言進行數(shù)字電路設(shè)計的很大

2020-09-22 20:46:51 1259

1259

本文檔的主要內(nèi)容詳細(xì)介紹的是FPGA VHDL語言基礎(chǔ)的學(xué)習(xí)課件免費下載。

2021-01-21 16:30:00 27

27 本文檔的主要內(nèi)容詳細(xì)介紹的是使用VHDL實現(xiàn)數(shù)字電路設(shè)計的詳細(xì)資料說明包括了:ASIC技術(shù)的發(fā)展,電路系統(tǒng)設(shè)計方法,自定向下的設(shè)計流程,設(shè)計描述風(fēng)格。

2021-01-21 17:03:18 15

15 VHDL 語言的英文全名為Very High Speed IntegratedCircuit Hardware Description Language,即超高速集成電路硬件描述語言。

2021-01-21 17:03:17 8

8 本文檔的主要內(nèi)容詳細(xì)介紹的是VHDL的硬件描述語言基礎(chǔ)詳細(xì)資料說明包括了:簡介,基本結(jié)構(gòu),基本數(shù)據(jù)類型,設(shè)計組合電路,設(shè)計時序電路,設(shè)計狀態(tài)機,大規(guī)模電路的層次化設(shè)計,F(xiàn)unction and Procedure

2021-01-21 17:03:16 18

18 本文檔的主要內(nèi)容詳細(xì)介紹的是VHDL硬件描述語言的學(xué)習(xí)課件免費下載包括了:VHDL概述,VHDL數(shù)據(jù)類型與數(shù)據(jù)對象,VHDL命令語句

2021-01-22 08:00:00 5

5 本例針對一個典型的加法器進行VHDL語言的描述,比較特殊的是該加法器帶有一個控制端口。它用于完成兩個位向量的相加:其電路系統(tǒng)示意圖如圖1.1所示。

2022-11-03 16:12:28 18

18 和結(jié)構(gòu)體這兩個基本結(jié)構(gòu)是必須的,他們可以構(gòu)成最簡單的VHDL程序。實體用于描述電路器件的外部特性;結(jié)構(gòu)體用于描述電路器件的內(nèi)部邏輯功能或電路結(jié)構(gòu);包集合存放各設(shè)計模塊都能共享的數(shù)據(jù)類型、常數(shù)和子程序等;配置用于從庫中選取所需單元來組成系統(tǒng)設(shè)計的不同版本;庫用于存放已經(jīng)編譯的實體、結(jié)構(gòu)體、包集合

2022-11-09 13:32:25 5989

5989 電子發(fā)燒友網(wǎng)站提供《基于VHDL的組合邏輯設(shè)計.ppt》資料免費下載

2024-03-11 09:23:29 2

2

電子發(fā)燒友App

電子發(fā)燒友App

評論