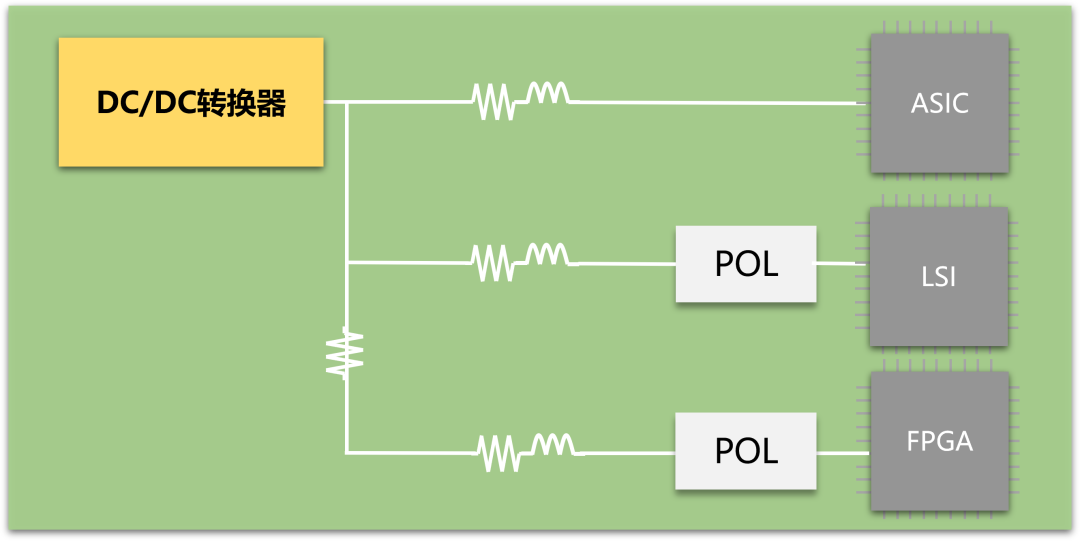

對(duì)于基于FPGA的電路板而言,需要四至五個(gè)不同的低壓電源對(duì)不同元件供電在現(xiàn)已經(jīng)非常普遍,從最開(kāi)始的3.3V,然后逐步降至2.5V、1.8V、1.5V,現(xiàn)在的低壓僅為1.2V。每個(gè)新一代FPGA似乎都需要一個(gè)新的低電源電壓。

2015-02-05 13:53:40 2597

2597

以AMD-Xilinx FPGA為例,不同的制程工藝下針對(duì)用戶的各種需求,會(huì)規(guī)劃有多個(gè)產(chǎn)品系列,其中集成不同功能、不同性能的功能模塊,因此我們按照功能模塊劃分來(lái)描述AMD-Xilinx FPGA需要的各種供電電源,簡(jiǎn)單把電源種類分為PL供電電源、PS供電電源、集成功能塊供電電源。

2022-09-23 14:51:21 3117

3117 電子發(fā)燒友網(wǎng)綜合報(bào)道,當(dāng)前,可穿戴設(shè)備正朝著更小、更智能、續(xù)航更高的方向演進(jìn)。就在12月,Nordic 發(fā)布nRF54LV10A系統(tǒng)級(jí)芯片(SoC),成為業(yè)界首款將超低電壓供電能力與藍(lán)牙信道探測(cè)

2025-12-12 09:19:35 6062

6062 PLD是小規(guī)模集成電路,主要是替代TTL集成電路的可編程邏輯電路FPGA 是大規(guī)模集成電路,它是在PLD、PAL、GAL 、CPLD等可編程器件的基礎(chǔ)上進(jìn)一步發(fā)展而成的。或者說(shuō)是經(jīng)過(guò)了幾代的升級(jí)產(chǎn)品

2018-08-28 09:15:53

通常FPGA中會(huì)有各種資源可以使用,而每種資源都需要有電源電壓支持。在單片機(jī)中,通常是使用同樣的電源電壓供電的,比如常見(jiàn)的5V、3.3V。而在FPGA中,一般需要:核心電壓、I/O口電壓、PLL電壓

2024-05-22 18:42:44

1.PLD/FPGA/CPLDPLD(Programmable Logic Device):可編程邏輯器件,數(shù)字集成電路半成品,芯片上按照一定的排列方式集成了大量的門和觸發(fā)器等基本邏輯元件,使用者

2021-07-30 07:26:19

。

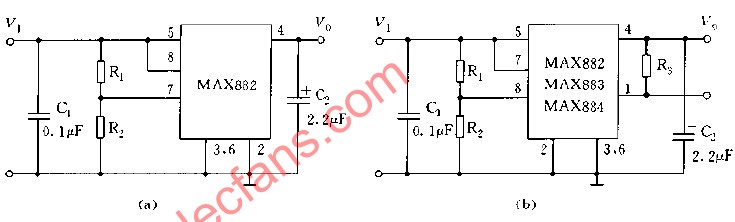

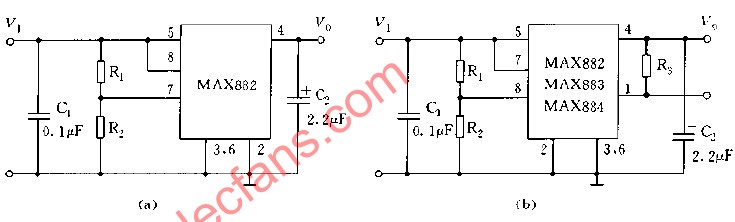

如何設(shè)計(jì)3.3v,2.5v 等低電壓PLD/FPGA的電源?

用低壓差線形穩(wěn)壓器(LDO)或采用開(kāi)關(guān)電源,詳細(xì)內(nèi)容參見(jiàn)低電壓PLD/FPGA的相關(guān)供電設(shè)計(jì)。

CPLD/FPGA的宏單元是怎么定義?是否是指包含

2024-04-12 16:58:35

`PLD/FPGA的分類和使用 在PLD/FPGA開(kāi)發(fā)軟件中完成設(shè)計(jì)以后,軟件會(huì)產(chǎn)生一個(gè)最終的編程文件(如 .pof )。如何將編程文件燒到PLD芯片中去呢? 1.對(duì)于基于乘積項(xiàng)

2012-02-27 10:42:53

PLD是可編程邏輯器件(Programable Logic Device)的簡(jiǎn)稱,FPGA是現(xiàn)場(chǎng)可編程門陣列(Field Programable Gate Array)的簡(jiǎn)稱,兩者的功能基本相

2009-06-20 10:38:05

,足以滿足設(shè)計(jì)一般的數(shù)字系統(tǒng)的需要。目前常用EEPROM,CPLD,FPGA。 PLA,PAL,GAL是早期的可編程器件,已經(jīng)淘汰。可編程邏輯器件PLD(Programmable Logic Dev...

2021-07-22 09:05:48

作者:張宇清可編程邏輯器件(PLD)的兩種主要類型是現(xiàn)場(chǎng)可編程門陣列(FPGA)和復(fù)雜可編程邏輯器件(CPLD)。根據(jù)半導(dǎo)體行業(yè)協(xié)會(huì)提供的數(shù)據(jù),PLD現(xiàn)在是半導(dǎo)體行業(yè)中增長(zhǎng)最快的領(lǐng)域之一,高性能

2019-07-29 08:07:20

可編程邏輯器件(PLD)的兩種主要類型是現(xiàn)場(chǎng)可編程門陣列(FPGA)和復(fù)雜可編程邏輯器件(CPLD)。根據(jù)半導(dǎo)體行業(yè)協(xié)會(huì)提供的數(shù)據(jù),PLD現(xiàn)在是半導(dǎo)體行業(yè)中增長(zhǎng)最快的領(lǐng)域之一,高性能PLD現(xiàn)在已經(jīng)從

2019-07-17 07:19:16

可編程邏輯器件(PLD)的兩種主要類型是現(xiàn)場(chǎng)可編程門陣列(FPGA)和復(fù)雜可編程邏輯器件(CPLD)。根據(jù)半導(dǎo)體行業(yè)協(xié)會(huì)提供的數(shù)據(jù),PLD現(xiàn)在是半導(dǎo)體行業(yè)中增長(zhǎng)最快的領(lǐng)域之一,高性能PLD現(xiàn)在已經(jīng)從

2019-07-22 06:51:56

更優(yōu),所以各大半導(dǎo)體公司都將3.3V、2.5V等低電壓集成電路作為推廣重點(diǎn),如高端的DSP、PLD/FPGA產(chǎn)品已廣泛采用3.3V、2.5V甚至1.8V、1 5V供電。因此,低電壓數(shù)字系統(tǒng)的電源設(shè)計(jì),是電子工程師面臨的嚴(yán)峻挑戰(zhàn)。

2021-05-25 07:29:36

低電壓穿越是什么? 低電壓穿越有哪些基本要求?低電壓穿越:當(dāng)電網(wǎng)故障或擾動(dòng)引起風(fēng)電場(chǎng)并網(wǎng)點(diǎn)的電壓跌落時(shí),在電壓跌落的范圍內(nèi),風(fēng)電機(jī)組能夠不間斷并網(wǎng)運(yùn)行。低電壓穿越(LVRT),指在風(fēng)力發(fā)電機(jī)并網(wǎng)

2012-02-02 09:08:12

低電壓,低電阻檢測(cè)資料

2012-08-16 16:38:15

。 低電壓和低功耗 隨著超大規(guī)模集成電路的發(fā)展,NMOS 工藝單片機(jī)被CMOS代替,并開(kāi)始向HMOS 過(guò)渡。供電電壓由5V 降到3V,2V 甚至到1V ,工作電流由mA 降至μA ,這在便攜式產(chǎn)品中大

2017-06-29 11:35:30

【FPGA學(xué)習(xí)教程】第1課.FPGA/PLD新手入門1. 可編程邏輯器件的發(fā)展歷程當(dāng)今社會(huì)是數(shù)字化的社會(huì),是數(shù)字集成電路廣泛應(yīng)用的社會(huì)。數(shù)字集成電路本身在不斷地進(jìn)行更新?lián)Q代。它由早期的電子管、晶體管

2012-02-27 11:52:00

過(guò)電壓對(duì)電氣設(shè)備和電力系統(tǒng)有何影響?高壓電動(dòng)機(jī)縱差動(dòng)保護(hù)工作原理與變壓器縱差動(dòng)保護(hù)相似嗎?高壓電動(dòng)機(jī)的供電網(wǎng)絡(luò)一般是什么?什么是低電壓繼電器?

2021-09-16 06:53:00

從FPGA或PLD轉(zhuǎn)換到門陣會(huì)遇到哪些時(shí)序問(wèn)題?如何去避免這些問(wèn)題的發(fā)生?

2021-04-30 06:54:18

1.25a、12v供電。低成本的物理層assp可用做與pld的接口,以進(jìn)一步增強(qiáng)數(shù)據(jù)處理。

視頻輸出

dvi和hdmi都基于最小化傳輸差分信號(hào)(tmds)信道,采用8b/10b編碼。a類hdmi

2018-12-28 07:00:06

請(qǐng)問(wèn)如何使用PLD去設(shè)計(jì)三相正弦波電壓發(fā)生器?

2021-04-29 07:01:08

應(yīng)用中也需要隔離技術(shù)來(lái)確保安全性。下圖是這類系統(tǒng)電源需求的簡(jiǎn)單方框圖。低電壓軌(通常 3.3V 或 5V)適用于主系統(tǒng)電源。可將該電壓軌用于生成隔離式低功耗電壓軌,其通常需要低于 2W 的功耗,而且未經(jīng)

2022-11-23 06:03:32

可編程邏輯器件(PLD)的兩種主要類型是現(xiàn)場(chǎng)可編程門陣列(FPGA)和復(fù)雜可編程邏輯器件(CPLD)。根據(jù)半導(dǎo)體行業(yè)協(xié)會(huì)提供的數(shù)據(jù),PLD現(xiàn)在是半導(dǎo)體行業(yè)中增長(zhǎng)最快的領(lǐng)域之一,高性能PLD現(xiàn)在已經(jīng)從

2019-09-24 06:58:39

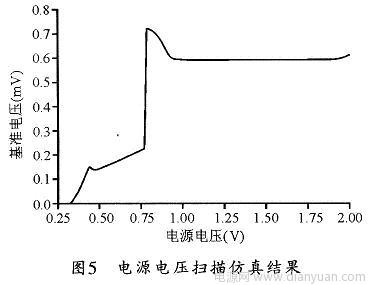

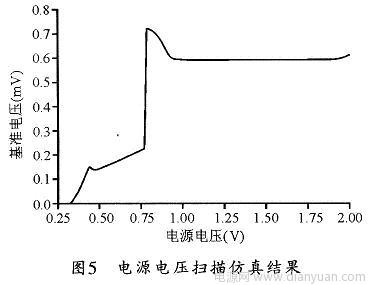

正常開(kāi)發(fā)板外部供電電壓是5v,如果將此電壓降低,FPGA實(shí)際使用的電壓有什么反應(yīng),會(huì)因?yàn)橛幸恍┓€(wěn)壓器件而沒(méi)有反應(yīng)么?比如降到1V甚至0.5V已知使用了SPX1117及SPX3819M5-L-1-2低壓差穩(wěn)壓芯片

2015-08-19 17:12:01

如題,現(xiàn)手上有一電源,能輸出0—-300V電壓,想通過(guò)0-5V電壓對(duì)應(yīng)控制該電源的輸出。第一種,0V低電壓控制電源輸出0V,1V低電壓控制電源輸出60V,2V低電壓控制電源輸出120V,…… 5

2013-05-11 17:35:43

GSM模塊供電,使用VBAT 和GND供電,最高電壓和最低電壓分別多少

2019-04-18 06:36:07

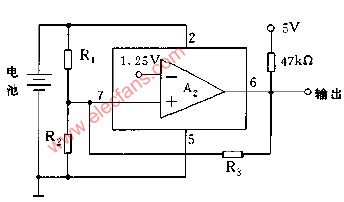

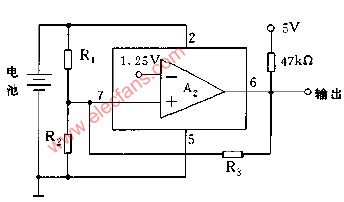

如何實(shí)現(xiàn)低電壓帶隙基準(zhǔn)電壓源的設(shè)計(jì)?傳統(tǒng)帶隙基準(zhǔn)電壓源的工作原理是什么?低電源帶隙基準(zhǔn)電壓源的工作原理是什么?

2021-04-20 06:12:32

/s。火線接口可在沒(méi)有主設(shè)備的情況下運(yùn)行,進(jìn)行點(diǎn)對(duì)點(diǎn)的通信,線纜最長(zhǎng)可達(dá)4.5m,最多支持63個(gè)設(shè)備。對(duì)于相連的設(shè)備,可提供1.25A、12V供電。低成本的物理層ASSP可用做與PLD的接口,以進(jìn)一步

2019-05-14 07:00:12

頻率和較低電壓對(duì)眼圖張開(kāi)的影響高速數(shù)據(jù)速率系統(tǒng)信號(hào)完整性基礎(chǔ)知識(shí)和關(guān)鍵問(wèn)題

2021-02-25 08:20:45

用單片機(jī)配置FPGA—PLD設(shè)計(jì)技巧

Configuration/Program Method for Altera Device

Configure the FLEX Device

You

2008-09-11 09:36:56 23

23 近期發(fā)布的低電壓微處理器監(jiān)控電路可以構(gòu)成低電壓、低功耗LED 閃爍器,并能夠調(diào)節(jié)點(diǎn)亮?xí)r間與閃爍速率的。圖1 所示,μP監(jiān)控電路(IC1)由兩節(jié)Nicd或NiMH電池供電,能夠驅(qū)動(dòng)高

2009-04-23 08:47:38 147

147 基于PLD及FPGA的頻率與相位測(cè)量系統(tǒng)設(shè)計(jì)與實(shí)現(xiàn):摘 要:本測(cè)量系統(tǒng)由頻率相位測(cè)量?jī)x和DDS 雙路移相信號(hào)發(fā)生器兩部分組成。頻率相位測(cè)量由Altera EPM7128S84 CPLD 完成,雙路移相信號(hào)

2009-09-25 15:50:03 31

31 探討了一種基于SOPC( System on a Programmable Chip) 的低電壓電泳芯片系統(tǒng)平臺(tái)設(shè)計(jì)方案。以基于FPGA 內(nèi)嵌NiosII 軟核處理器為系統(tǒng)控制模塊,運(yùn)用SOPC Builder 定制低電壓電泳芯片運(yùn)動(dòng)梯度電勢(shì)

2009-11-30 15:54:22 7

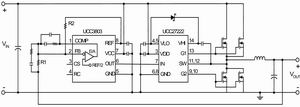

7 就低電壓高電流電源應(yīng)用而言,開(kāi)關(guān)式電源柵極驅(qū)

2006-03-11 12:59:28 2248

2248

ia

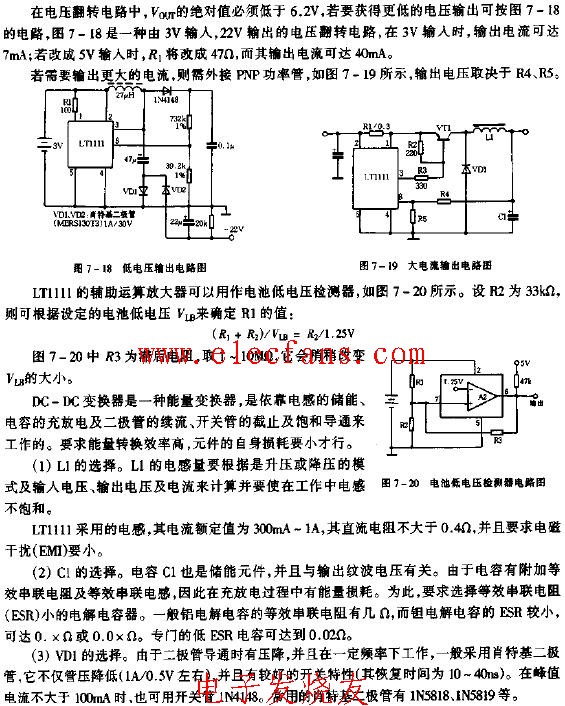

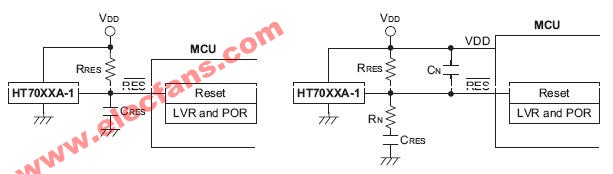

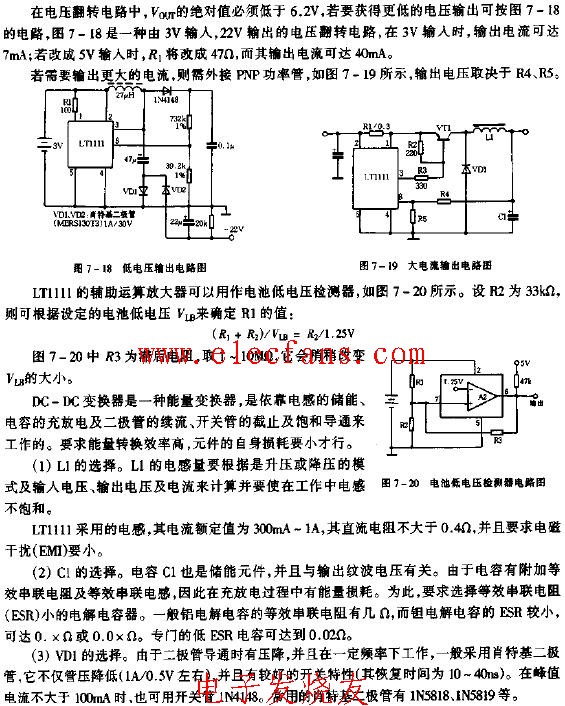

低電壓輸出電路圖

2008-05-06 23:26:28 2177

2177

低電壓

2008-06-14 12:23:54 2132

2132

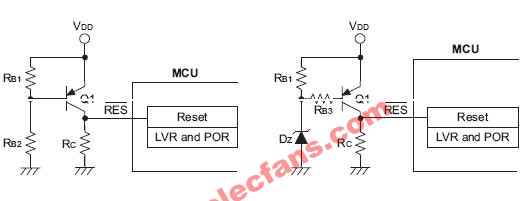

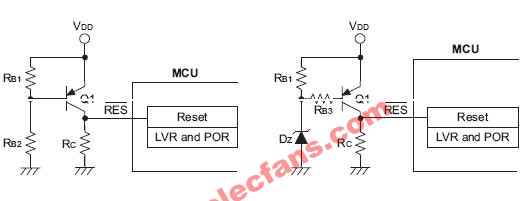

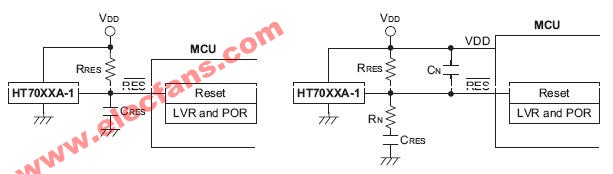

三極管低電壓復(fù)位電路

• 當(dāng)內(nèi)建的低電壓復(fù)位電路的電壓與應(yīng)用規(guī)格

2008-10-24 16:06:18 7486

7486

低電壓檢測(cè)IC的復(fù)位電路

• 當(dāng)內(nèi)

2008-10-24 16:08:01 4405

4405

低電壓輸出電路圖

2009-05-13 15:23:43 952

952

PLD/FPGA新手入門知識(shí)

PLD是可編程邏輯器件(Programable Logic Device)的簡(jiǎn)稱,FPGA是現(xiàn)場(chǎng)可編程門陣列(Field Programable Gate Array)的簡(jiǎn)稱,兩者的功能基本相

2009-06-20 10:31:05 1427

1427

什么是PLD(可編程邏輯器件)

PLD是可編程邏輯器件(Programable Logic Device)的簡(jiǎn)稱,FPGA是現(xiàn)場(chǎng)可編程門陣列(Field Programable Gate Array)

2009-06-20 10:32:32 29733

29733

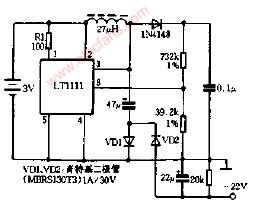

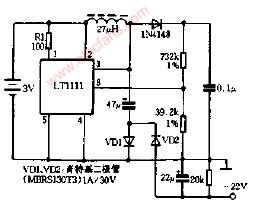

低電壓輸入DC/AC變換器模塊

摘要:介紹在低電壓輸入下工作的低頻交流模塊的工作原理、應(yīng)用范圍和技術(shù)指標(biāo)。

2009-07-10 11:33:04 1504

1504

低電壓用PTC恒溫加熱器

產(chǎn)品概述

低電壓PTC恒溫加熱器只需3~24V電壓即可恒溫發(fā)

2009-10-01 12:25:29 15072

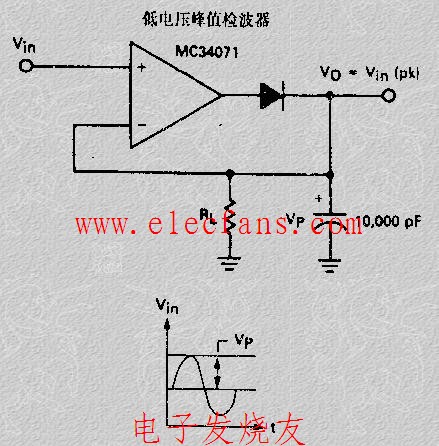

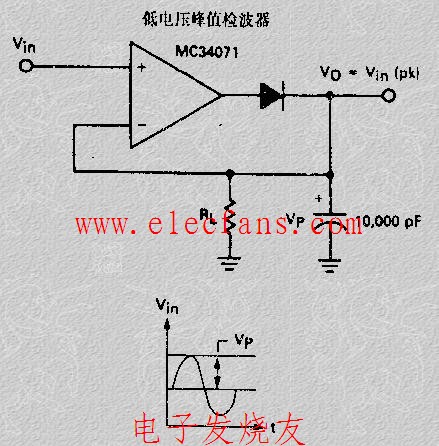

15072 設(shè)定電池低電壓值電路

2009-10-24 16:53:48 1037

1037

電池低電壓檢測(cè)電路

如圖所示,設(shè)R2為33KM則可根據(jù)

2009-10-27 11:34:59 9943

9943

空調(diào)遇低電壓應(yīng)該注意什么

目前我國(guó)部分地區(qū)的電網(wǎng)電壓偏低,空調(diào)在低電壓下運(yùn)行,如果過(guò)載保

2010-02-21 15:09:44 2869

2869 低電壓下工作的LED閃爍器原理

近期發(fā)布的低電壓微處理器監(jiān)控電路可以構(gòu)成低電壓、低功耗LED閃爍器,并能夠調(diào)節(jié)點(diǎn)亮?xí)r間與閃爍速

2010-03-09 16:55:04 2215

2215

低電壓帶隙基準(zhǔn)電壓源技術(shù)解決方案

本文采用一種低電壓帶隙基準(zhǔn)結(jié)構(gòu)。在TSMC0.13μm

2010-04-17 15:41:41 4913

4913

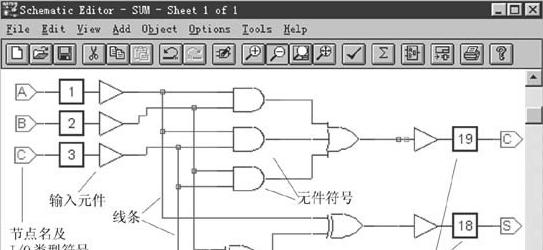

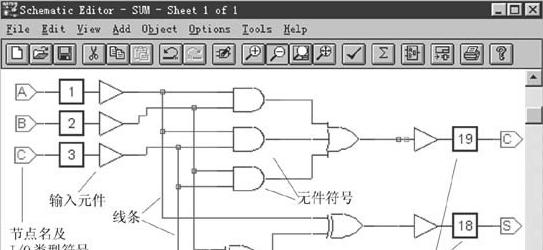

PLD設(shè)計(jì)方法及步驟 1、PLD器件的設(shè)計(jì)步驟

1.電路邏輯功能描述

PLD器件的邏輯功能描述一

2010-09-18 09:08:30 5109

5109

為了能夠?qū)崿F(xiàn)對(duì)低電壓控制電路的連續(xù)無(wú)間斷供電,詳細(xì)介紹了一種基于太陽(yáng)能供電的低電壓供電系統(tǒng)的設(shè)計(jì)方法;系統(tǒng)以充放電控制模塊為核心,采用免維護(hù)鉛酸蓄電池作為備用電源,并在UC3906的控制下使系統(tǒng)實(shí)現(xiàn)無(wú)間斷供電輸出。在完成系統(tǒng)設(shè)計(jì)的同時(shí),還充分考

2011-03-15 01:33:45 316

316 在FPGA設(shè)計(jì)中,為了成功地操作,可靠的時(shí)鐘是非常關(guān)鍵的。設(shè)計(jì)不良的時(shí)鐘在極限的溫度、電壓下將導(dǎo)致錯(cuò)誤的行為。在設(shè)計(jì)PLD/FPGA時(shí)通常采用如下四種類型時(shí)鐘:全局時(shí)鐘、門控時(shí)鐘

2011-09-21 18:38:58 4131

4131

PLD、FPGA優(yōu)秀設(shè)計(jì)的十條戒律, 該文淺顯易懂的介紹了一個(gè)優(yōu)秀設(shè)計(jì)必須考慮的問(wèn)題,給出了設(shè)計(jì)方法和建議。仔細(xì)閱讀和消化本文,對(duì)提高PLD/FPGA設(shè)計(jì)水平大有裨益

2012-01-17 10:32:59 61

61 用 VHDL /VerilogHD語(yǔ)言開(kāi)發(fā)PLD/ FPGA 的完整流程為: 1.文本編輯:用任何文本編輯器都可以進(jìn)行,也可以用專用的HDL編輯環(huán)境。通常VHDL文件保存為.vhd文件,Verilog文件保存為.v文件 2.功能仿真

2012-05-21 12:58:06 1687

1687 。PLD可分為簡(jiǎn)單PLD和復(fù)雜PLD,其中復(fù)雜PLD又包括CPLD和FPGA。在本專題我們將主要介紹CPLD和FPGA的相關(guān)技術(shù)知識(shí)。

2012-06-16 22:13:38

關(guān)于FPGA電源的設(shè)計(jì)與使用,我介紹個(gè)人意見(jiàn)。

2016-05-04 15:59:44 25

25 引言 目前這一代的 FPGA 芯片一般都要在低電壓、高電流的環(huán)境下操作。由于要求的供電電壓比上一代的產(chǎn)品低,而且要輸出更高電流,因此採(cǎi)用的電源供應(yīng)系統(tǒng)便要符合更嚴(yán)格的規(guī)定,一些以前視為可有可無(wú)的功能

2021-11-02 11:36:44 31

31 PLD(Programmable Logic Device)是可編程邏輯器件的總稱。早期的PLD多屬于EEPROM或乘積項(xiàng)(Product Term)結(jié)構(gòu)。FPGA(Field

2017-06-19 09:59:13 5942

5942 很大。 在設(shè)計(jì)PLD/FPGA時(shí)通常采用幾種時(shí)鐘類型。時(shí)鐘可分為如下四種類型:全局時(shí)鐘、門控時(shí)鐘、多級(jí)邏輯時(shí)鐘和波動(dòng)式時(shí)鐘。多時(shí)鐘系統(tǒng)能夠包括上述四種時(shí)鐘類型的任意組合。

2017-11-25 09:16:01 5020

5020

PLD/FPGA 常用開(kāi)發(fā)軟件maxplus2crack。 Altera公司的免費(fèi)PLD開(kāi)發(fā)軟件Altera公司的免費(fèi)PLD開(kāi)發(fā)軟件,界面與標(biāo)準(zhǔn)版的MaxplusII完全一樣,只支持MAX7000

2017-11-26 11:19:26 6

6 PLD/FPGA 常用開(kāi)發(fā)軟件System Generator 9.10。 業(yè)內(nèi)領(lǐng)先的高級(jí)系統(tǒng)級(jí)FPGA開(kāi)發(fā)高度并行系統(tǒng)。

2017-11-26 11:34:56 14

14 PLD介紹 可編程邏輯器件PLD(Programable Logic Device)是允許用戶編程(配置)實(shí)現(xiàn)所需邏輯功能的電路, 它與分立元件相比,具有速度快、容量大、功耗小和可靠性高等優(yōu)點(diǎn)。由于

2017-12-05 10:45:28 21

21 DRV8835 為攝像機(jī)、消費(fèi)類產(chǎn)品、玩具、和其它低電壓或者電池供電的運(yùn)動(dòng)控制類應(yīng)用提供了一個(gè)集成的電機(jī)驅(qū)動(dòng)器解決方案。

2018-05-10 10:27:08 10

10 在本視頻中,凌力爾特聯(lián)合創(chuàng)始人兼首席技術(shù)官 (CTO) Bob Dobkin 論述了低于 0.5V 的低電壓電源。當(dāng)今的大多數(shù)電源具有一個(gè) 0.6V 基準(zhǔn),這意味著輸出電壓必須大于 0.6V。幾年前

2018-06-04 13:47:00 5594

5594 通過(guò)PMBus電源向ASIC、FPGA?以及DDR電壓軌供電設(shè)計(jì)

2018-08-06 00:08:00 5335

5335 高電壓變?yōu)?b class="flag-6" style="color: red">低電壓是一個(gè)非常復(fù)雜的過(guò)程,不能單純的通過(guò)使用“管”來(lái)實(shí)現(xiàn),而且在設(shè)計(jì)技術(shù)方案的時(shí)候需要考慮比較多的技術(shù)需求,如直流、交流、輸入電壓范圍、輸出電壓、輸出電流等。本文主要從交流和直流兩個(gè)角度來(lái)介紹一下高壓如何轉(zhuǎn)化為低電壓。

2019-11-24 10:38:19 30478

30478 本文首先闡述了低電壓保護(hù)的概念,其次介紹了低電壓保護(hù)的應(yīng)用,最后介紹了低電壓保護(hù)裝置的接線要求。

2020-01-15 08:38:50 18928

18928 變頻器低電壓主要是指中間直流回路的低電壓,一般能引起中間直流回路的低電壓的原因來(lái)自兩個(gè)方面:

2020-04-06 16:48:00 9890

9890 在選購(gòu)筆記本的時(shí)候,有的型號(hào)會(huì)標(biāo)注為低電壓的內(nèi)存條或者是后綴帶有L,那么低電壓內(nèi)存和普通內(nèi)存的區(qū)別有哪些,下面就為大家?guī)?lái)相關(guān)的介紹。

2020-05-25 10:14:22 5711

5711 超低電壓處理器,英文全稱『Ultra Low Voltage』又稱為ULV處理器,其結(jié)尾命名通常帶有U結(jié)尾,比如i5-4200U。現(xiàn)在的低電壓處理器主要有T系列,U系列,Y系列。U系列通常是筆記本

2020-06-02 09:14:25 3699

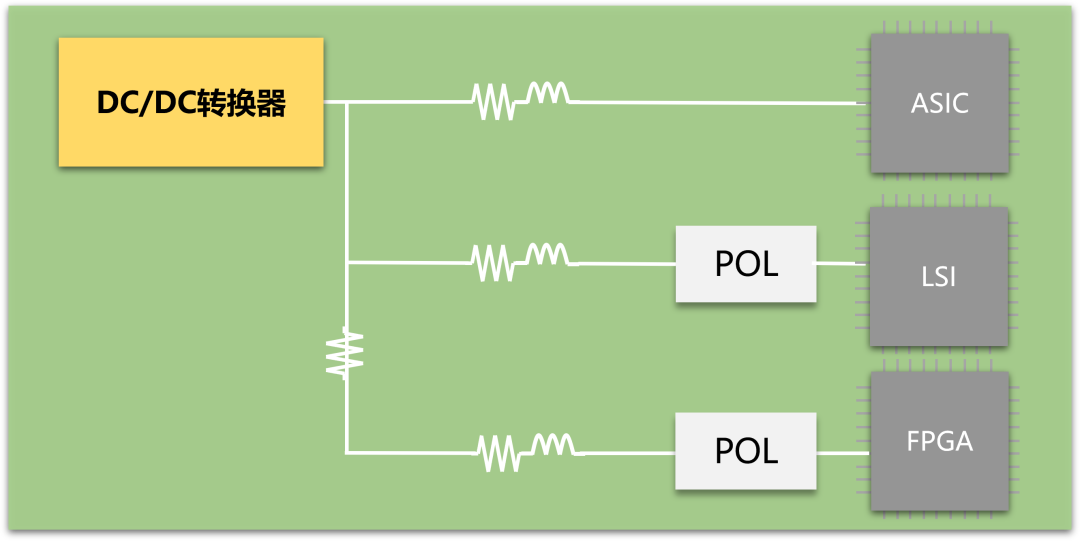

3699 降低從中間總線電壓直接為低電壓處理器和 FPGA 供電的風(fēng)險(xiǎn)

2021-03-20 19:30:18 8

8 MT-098:低電壓邏輯接口

2021-03-21 08:59:53 0

0 器件都會(huì)采用當(dāng)前最新的工藝技術(shù)。不同的功能需求以及集成工藝,使得PLD的供電電壓有所不同。 由于PLD在電路板上擔(dān)當(dāng)?shù)慕巧且粋€(gè)片上系統(tǒng)(SOC),為這些器件供電就相當(dāng)于為整個(gè)系統(tǒng)供電。典型的高端Virtex系列FPGA可能需要10~15路獨(dú)立的供電電壓。另一方面,較低密度的Sp

2021-06-01 10:55:40 2853

2853 編程數(shù)據(jù)存儲(chǔ)單元以陣列形式分布在FPGA中,一般把所有超過(guò)某一集成度PLD器件都稱為CPLD。 編程數(shù)據(jù)流由開(kāi)發(fā)軟件自動(dòng)生成,數(shù)據(jù)以串行方式移入移位寄存器圍繞一個(gè)可編程互連矩陣構(gòu)成,對(duì)于可編程邏輯器件PLD能完成任何數(shù)字器件的功能。

2021-10-01 09:17:00 8125

8125 如何調(diào)節(jié)低電壓隔離電源

2022-11-04 09:52:08 0

0 如何調(diào)節(jié)低電壓非隔離式電源

2022-11-07 08:07:25 3

3 如何調(diào)節(jié)低電壓隔離式電源

2022-11-07 08:07:26 0

0 PowerLab 筆記: 如何使用 Fly-buck? 為低電壓、低功耗工業(yè)應(yīng)用供電

2022-11-07 08:07:28 0

0 變頻器低電壓主要是指中間直流回路的低電壓,一般能引起中間直流回路的低電壓的原因來(lái)自兩個(gè)方面。

2023-01-14 11:30:55 2651

2651 變頻器低電壓主要是指中間直流回路的低電壓,一般能引起中間直流回路的低電壓的原因來(lái)自兩個(gè)方面。

2023-04-08 10:23:37 3667

3667 PLD(Programmable Logic Device)是一種由用戶根據(jù)需要而自行構(gòu)造邏輯功能的數(shù)字集成電路。目前主要有兩大類型:CPLD(Complex PLD)和FPGA(Field Programmable Gate Array)。

2023-04-29 16:46:00 2255

2255 對(duì)于評(píng)估低電壓大電流電源的輸出特性時(shí),應(yīng)該準(zhǔn)備什么樣的電子負(fù)載裝置?另外,當(dāng)POL電源變?yōu)?b class="flag-6" style="color: red">低電壓,超出電子負(fù)載裝置的電壓工作范圍時(shí),又該如何應(yīng)對(duì)呢?

2023-11-15 16:42:38 8270

8270

電子發(fā)燒友網(wǎng)站提供《低電壓邏輯接口設(shè)計(jì).pdf》資料免費(fèi)下載

2023-11-27 09:32:25 0

0 無(wú)功補(bǔ)償設(shè)備在電氣系統(tǒng)中扮演著重要的角色,它能夠提供電力系統(tǒng)所需的無(wú)功功率,以改善功率因數(shù),減少諧波和電壓浮動(dòng),提高電力系統(tǒng)的穩(wěn)定性和可靠性。然而,在實(shí)際應(yīng)用中,是否需要為SVG無(wú)功補(bǔ)償設(shè)備提供低電壓保護(hù)引起了廣泛關(guān)注。

2024-04-09 14:32:14 1858

1858 在電氣工程中,低電壓指的是電壓在1000V以下的電壓等級(jí)。通常,家庭和商業(yè)用電都屬于低電壓范疇。零線是供電系統(tǒng)中的一個(gè)關(guān)鍵組成部分,它提供了電流的回路,確保了電路的完整性和安全性。繼電器是一種用于

2024-09-05 17:00:44 1454

1454 低電壓工作業(yè),特別是在日常電氣安裝和維護(hù)中,通常指的是對(duì) 1千伏(kV)以下 的低壓電器設(shè)備進(jìn)行的一系列操作。這些操作包括但不限于設(shè)備的安裝、調(diào)試、運(yùn)行、維護(hù)、檢修、改造施工和試驗(yàn)等。以下是對(duì)低電壓

2024-09-05 17:07:53 3648

3648 電子發(fā)燒友網(wǎng)站提供《PWM應(yīng)用的低電壓反饋.pdf》資料免費(fèi)下載

2024-10-21 09:23:58 0

0 低電壓冗余電源方案設(shè)計(jì)

2024-12-16 14:47:22 2

2 PLD的定義和應(yīng)用 一、PLD的定義 PLD(Programmable Logic Device)即可編程邏輯器件,是一種能夠根據(jù)用戶的需求和設(shè)計(jì)規(guī)格,通過(guò)內(nèi)部的可編程連接和邏輯門陣列,靈活地組合

2025-02-01 10:35:00 6636

6636 (Design Planning) 選擇PLD類型 :根據(jù)需求選擇合適的PLD類型,如FPGA、CPLD等。 資源評(píng)估 :評(píng)估所需的邏輯資源、

2025-01-20 09:46:33 1979

1979 1. 理解PLD的基本概念 PLD的定義 :PLD是一種可以通過(guò)編程來(lái)配置的集成電路,用于實(shí)現(xiàn)特定的數(shù)字邏輯功能。 PLD的類型 :包括FPGA(Field-Programmable Gate

2025-01-20 09:48:06 1586

1586

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論