資料介紹

描述

目標:該項目的主要目標是展示高級綜合設(shè)計流程在實現(xiàn)數(shù)字系統(tǒng)中的能力和能力。

由于這是我在 hackster 中的第一個項目,因此我嘗試逐步解釋所有細節(jié)。如果您有興趣學習高級合成技術(shù)來設(shè)計數(shù)字系統(tǒng),請參閱此處。

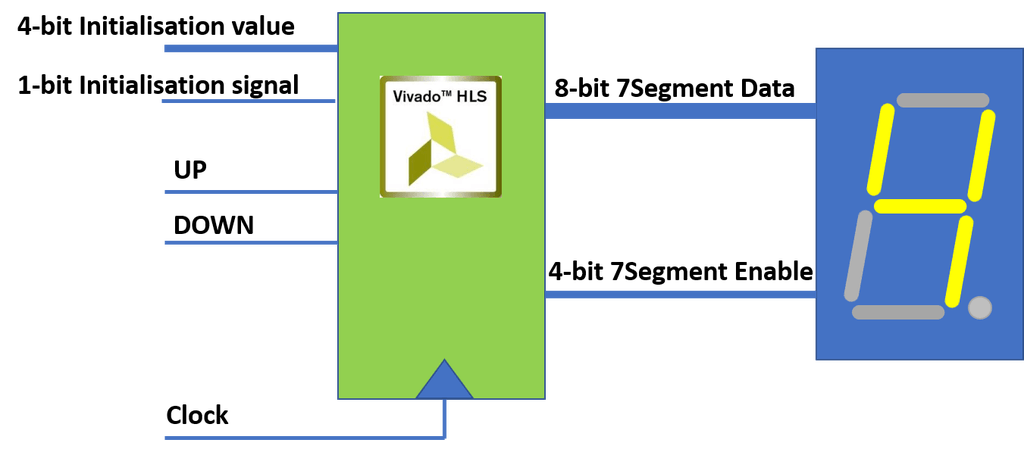

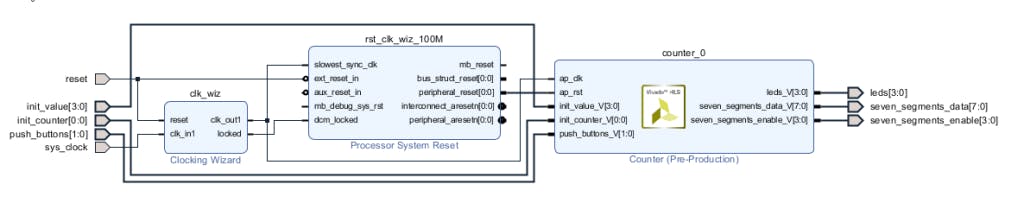

項目描述:在這個項目中,我將設(shè)計一個帶有初始化信號的 0-9 加/減計數(shù)器。圖 1 顯示了該項目的概覽。

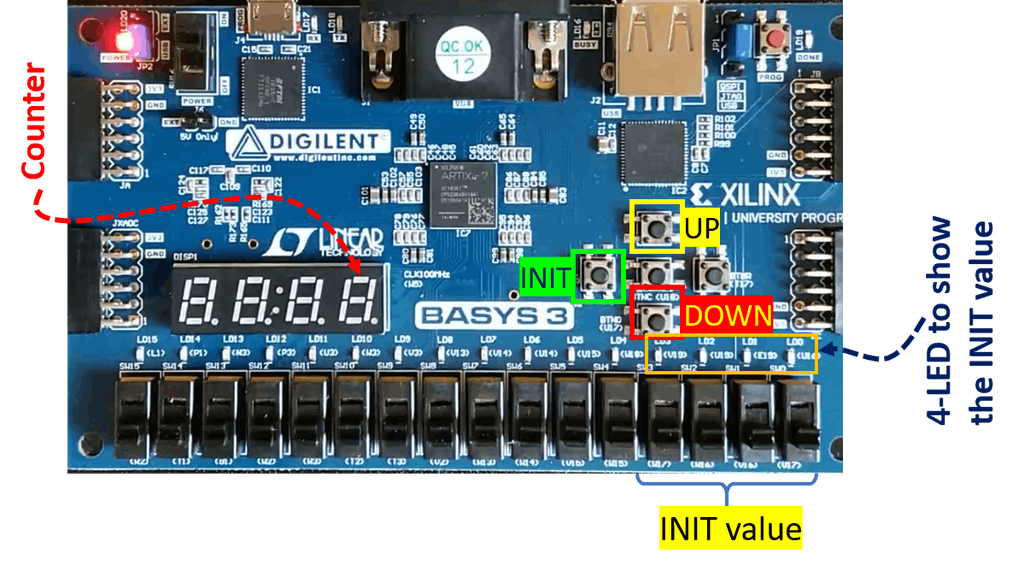

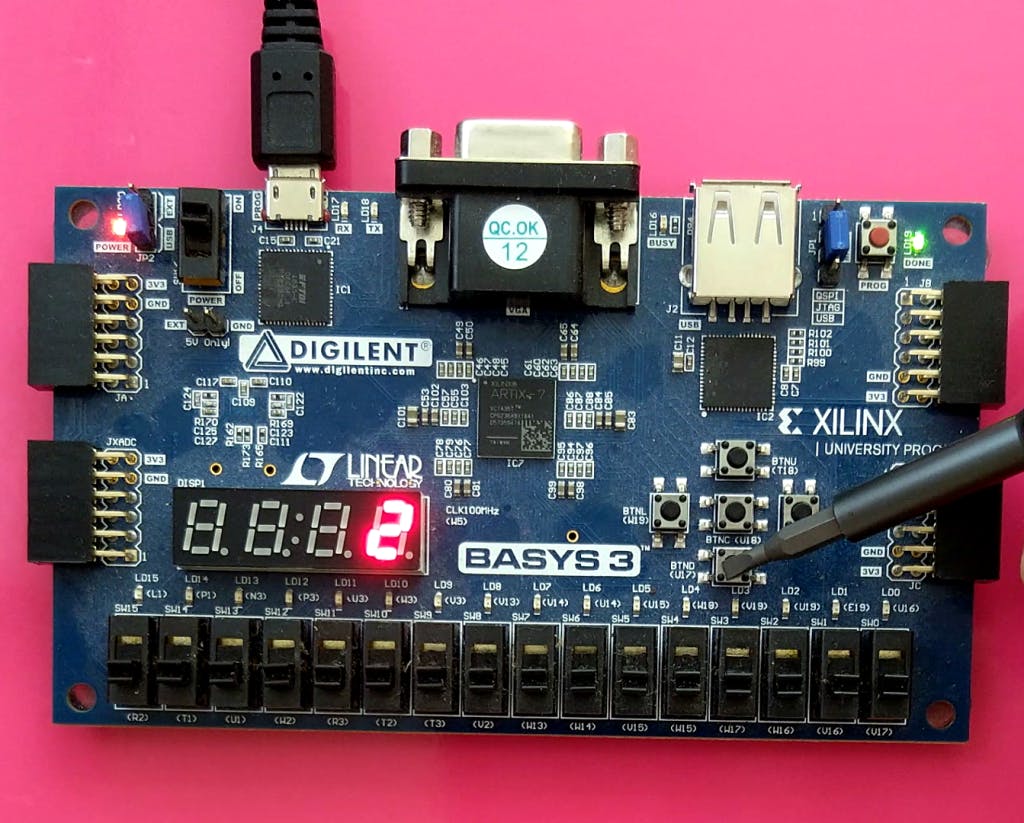

為了實現(xiàn)這個項目,我使用了 Vivado Design Suite – HLx Editions 提供的 Xilinx HLS 平臺。此外,我將使用 Basys 3 評估板作為目標 FPGA 平臺。圖 2 顯示了板上最終遞增/遞減計數(shù)器的布局。右側(cè)的 7 段顯示計數(shù)器。UP 按鈕用于向上計數(shù),DOWN 按鈕用于向下計數(shù)。INIT 按鈕初始化計數(shù)器。用“INIT value”表示的四個滑動開關(guān)用于輸入初始化編號。此外,四個 LED 顯示該值。

我們分三個階段來實施這個項目:C/C++ 描述、邏輯綜合和電路板編程。

第 1 階段:C/C++ 描述(Vivado-HLS 項目)

1- 運行 Vivado-HLS IDE 并創(chuàng)建一個新項目。

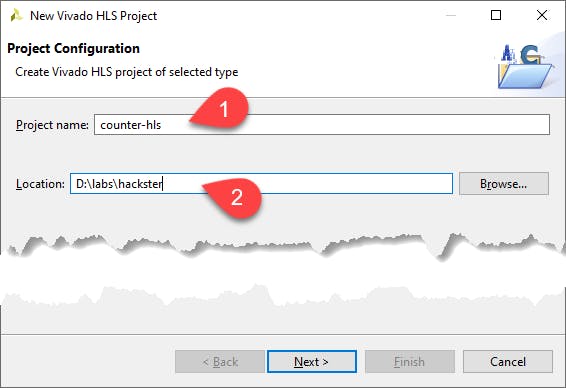

2- 在創(chuàng)建新項目向?qū)У牡谝豁撝校迦搿癱ounter-vhls”作為項目名稱,并為項目文件選擇適當?shù)奈恢谩?/font>

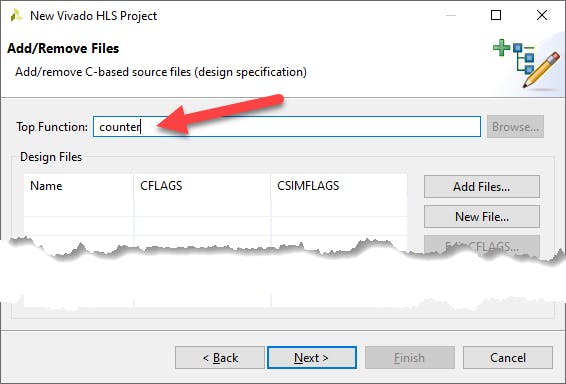

3-選擇“計數(shù)器”作為頂級功能名稱。

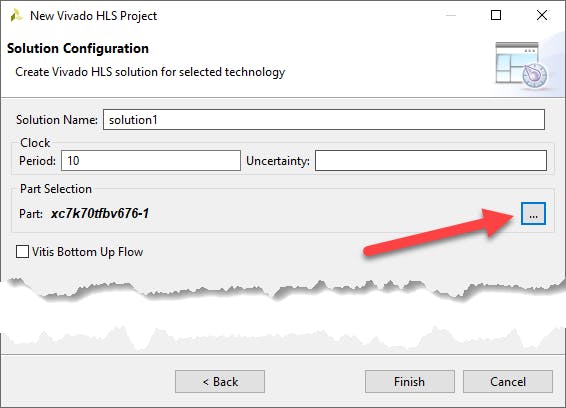

4- 在“解決方案配置”頁面中,單擊省略號按鈕選擇 FPGA 平臺。

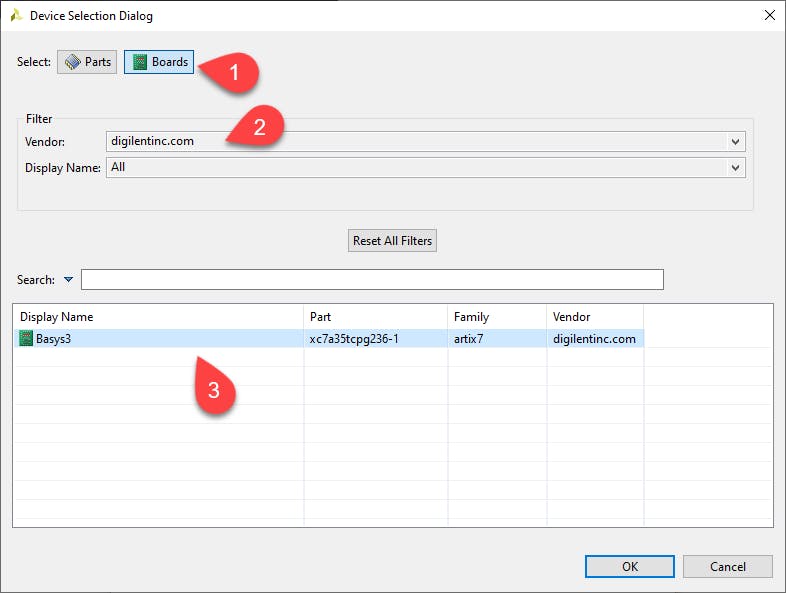

5- 設(shè)備選擇對話框?qū)⒋蜷_。點擊Boards,找到digilent vendor,選擇Basys3 board,點擊OK。

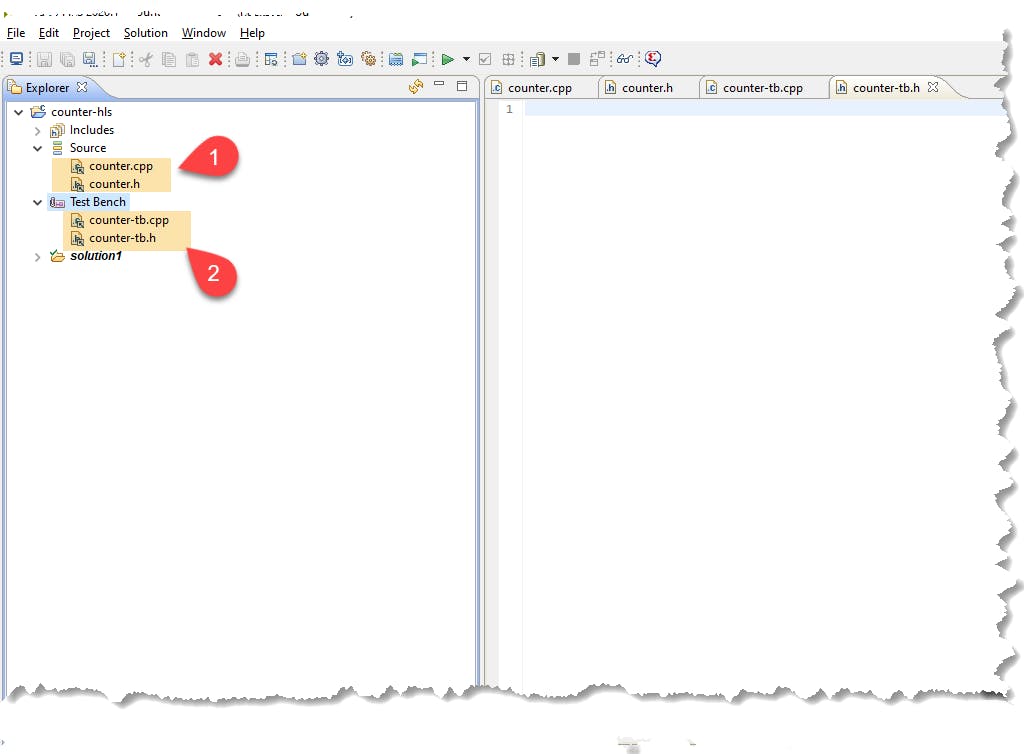

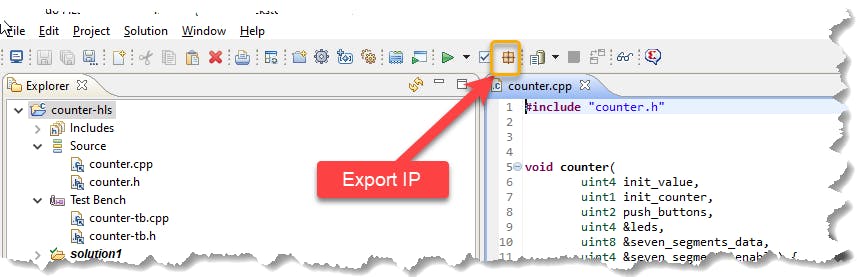

6- 在 Source 文件夾下創(chuàng)建兩個名為“counter.cpp”和“counter.h”的新文件。

7- 在 Test Bench 文件夾下創(chuàng)建兩個名為“counter-tb.cpp”和“counter-tb.h”的新文件。

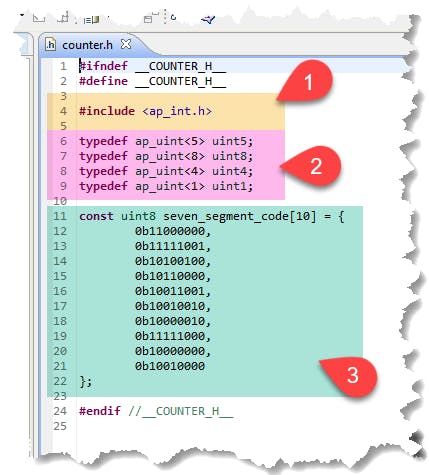

8-讓我們編寫設(shè)計頭文件如下。如下圖所示,該文件中的代碼分為三個部分:

1- 首先,由于我們要使用 HLS 任意精度數(shù)據(jù)類型,我們應(yīng)該包含“ap_int.h”頭文件。2- 其次,我們定義了一些稍后在設(shè)計中使用的數(shù)據(jù)類型 3- 最后,我們定義了一個常量數(shù)組,用于保存對應(yīng)于從 0 到 9 的數(shù)字的 7 段代碼。

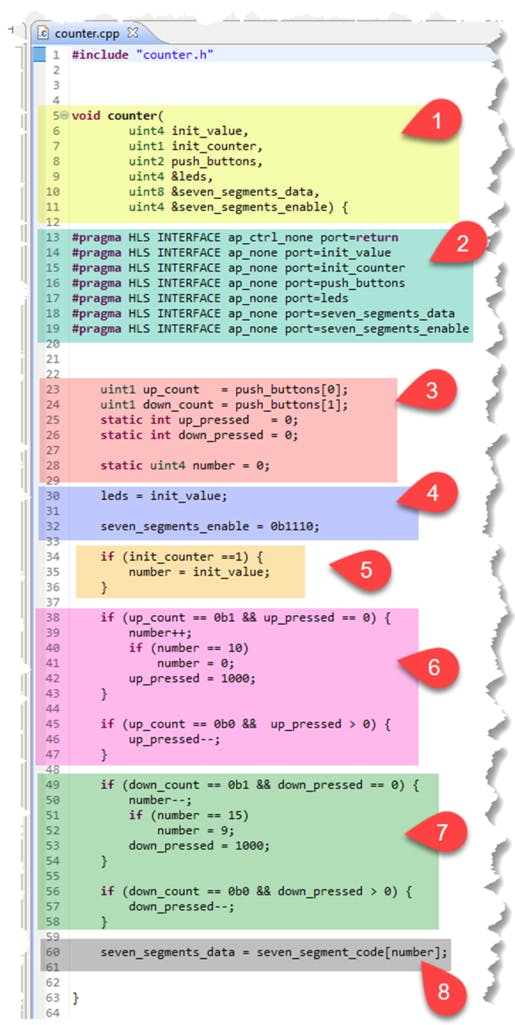

9- 設(shè)計源文件包含頂層功能描述。它由八個部分組成。

1-頂級函數(shù)參數(shù):該函數(shù)包含三個輸入和兩個輸出參數(shù)。

init_value變量包含計數(shù)器初始值。

reset_counter變量確定何時應(yīng)該初始化計數(shù)器。當它為 1 時,計數(shù)器獲取init_value參數(shù)中的值。

push_buttons變量確定向上或向下計數(shù)。

Seven_segments_data變量包含對應(yīng)于計數(shù)器狀態(tài)的 7 段代碼

Seven_segments_enable變量啟用目標 7 段。

2-端口接口:本節(jié)定義與頂級函數(shù)參數(shù)對應(yīng)的端口接口。這些接口定義了實現(xiàn)參數(shù)數(shù)據(jù)事務(wù)的硬件結(jié)構(gòu)。由于我們有一個簡單的設(shè)計,并且我們希望簡單的電線實現(xiàn)參數(shù),我選擇了ap_none作為接口模式。

3-聲明變量:在這里,我聲明了一些要在設(shè)計中使用的變量。如果按下 UP 按鈕,up_count 變量將為1 。如果按下 DOWN 按鈕,則 down_count 將為1 。up_pressed和down_pressed被聲明為靜態(tài)變量以保存按鈕的歷史記錄。number變量保持計數(shù)器狀態(tài),因此定義為靜態(tài)變量。

4-設(shè)置輸出:此部分將 INIT 值發(fā)送到 LED 并啟用右側(cè) 7 段。

5-初始化:如果reset_counter信號被激活,這個if 語句初始化計數(shù)器狀態(tài)。

6-向上計數(shù):這部分由兩個if 語句組成。第一個檢查是否按下了向上按鈕。第二個if檢查 UP 按鈕是否已被釋放。

7-向下計數(shù):這部分與向上計數(shù)部分非常相似。

8- 7 段碼:最后一段發(fā)出計數(shù)器狀態(tài)對應(yīng)的 7 段碼。

10- 現(xiàn)在,我們需要一個 C/C++ 測試平臺來測試設(shè)計。可以在此處找到測試臺文件。測試臺分為三個步驟:

— 生成測試向量, — 將測試向量應(yīng)用于設(shè)計, — 最后,將硬件輸出與黃金模型的輸出進行比較并報告任何差異

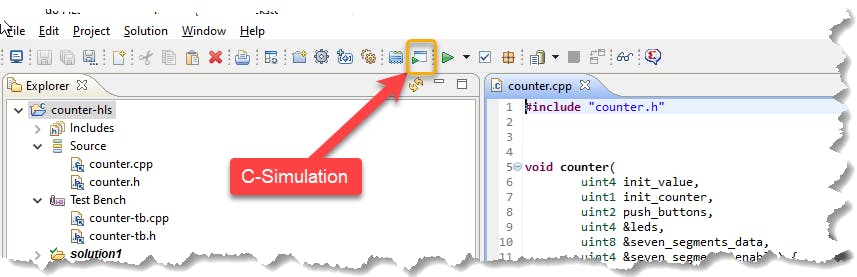

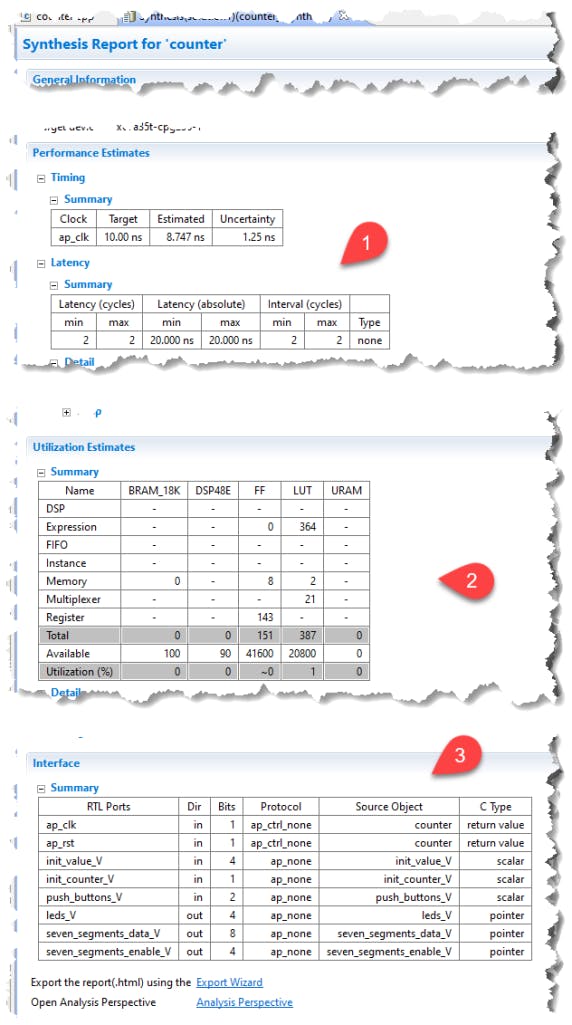

11- 現(xiàn)在我們可以通過單擊工具欄中的圖標來運行 C 模擬。

12-成功完成C-Simulation后,我們可以運行高級綜合。

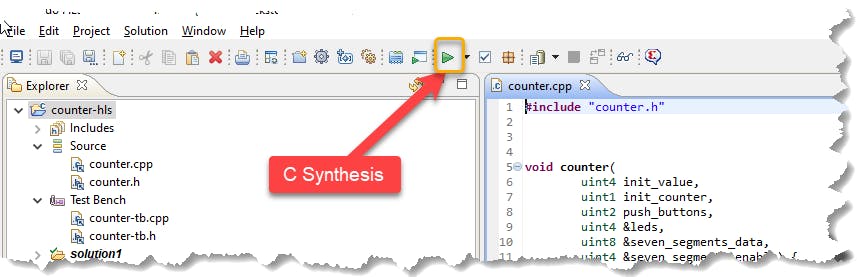

圖 13 顯示了綜合報告的部分內(nèi)容。它有三個主要部分:

1- 時序信息 2- 資源利用 3- 端口接口

13- 最后,我們應(yīng)該通過單擊其圖標來生成和導出設(shè)計 RTL-IP。

第 2 階段:邏輯綜合(Vivado 項目)

現(xiàn)在,我們已準備好進行邏輯綜合和生成 FPGA 比特流。

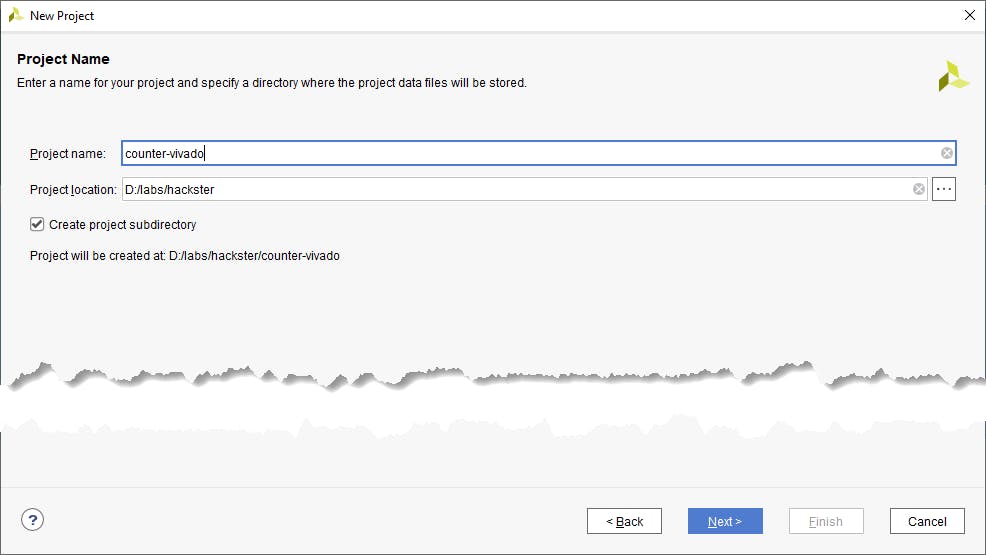

1-創(chuàng)建一個名為counter-vivado的新Vivado項目。請注意,該項目沒有任何源文件。

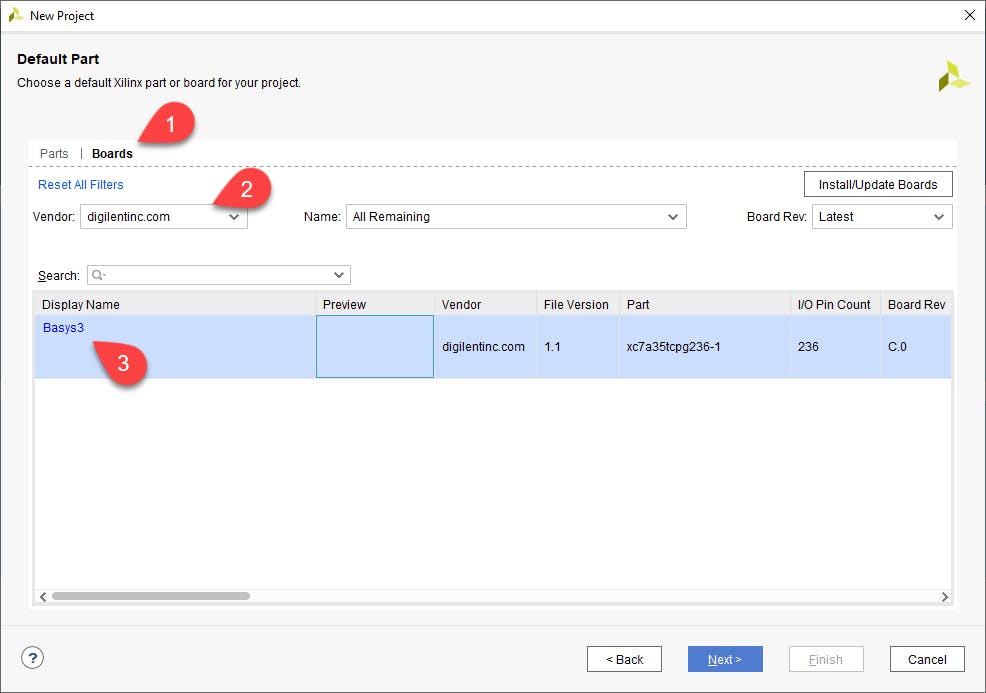

2- 不要忘記選擇 Basys-3 板作為目標 FPGA。

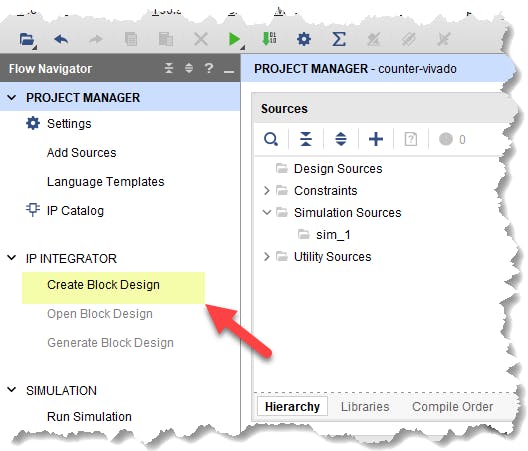

3-創(chuàng)建一個新的塊設(shè)計

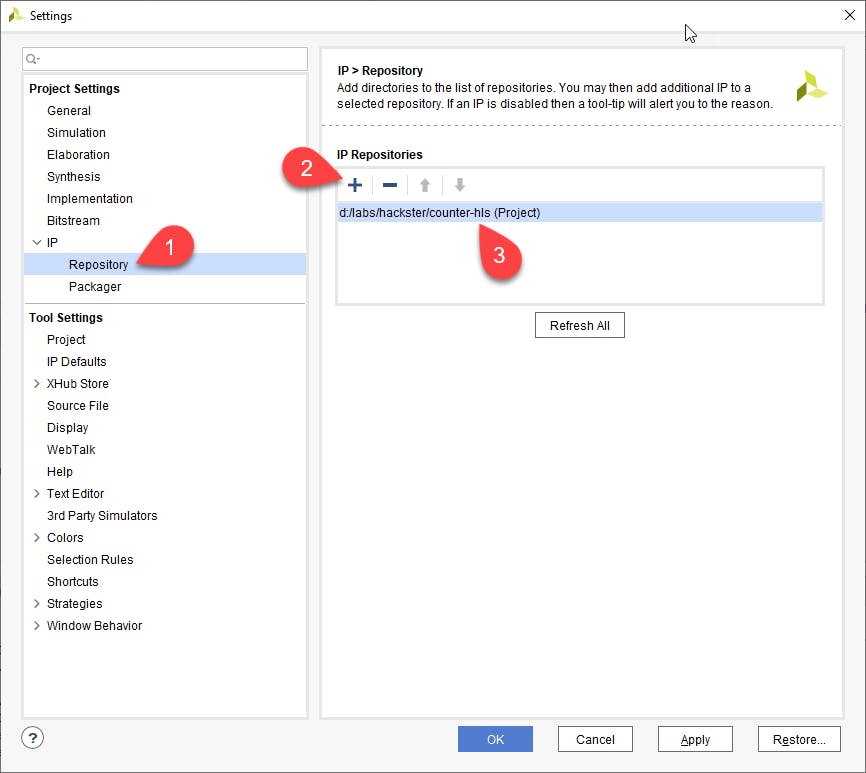

4-右鍵單擊圖表區(qū)域內(nèi)的某處并選擇“IP設(shè)置...”選項

5-然后單擊設(shè)置對話框中IP下的存儲庫選項。然后點擊右側(cè)的加號,瀏覽到counter HLS項目文件夾。Vivado 在文件夾中搜索任何可能的 IP 并將其添加到其存儲庫中。

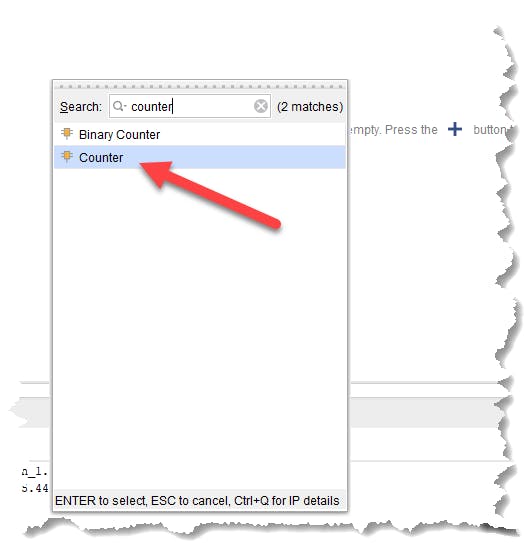

6- 右鍵單擊??圖表區(qū)域內(nèi)的某處并選擇“添加..”選項。然后搜索計數(shù)器 IP 并將其添加到 vivado 項目中。

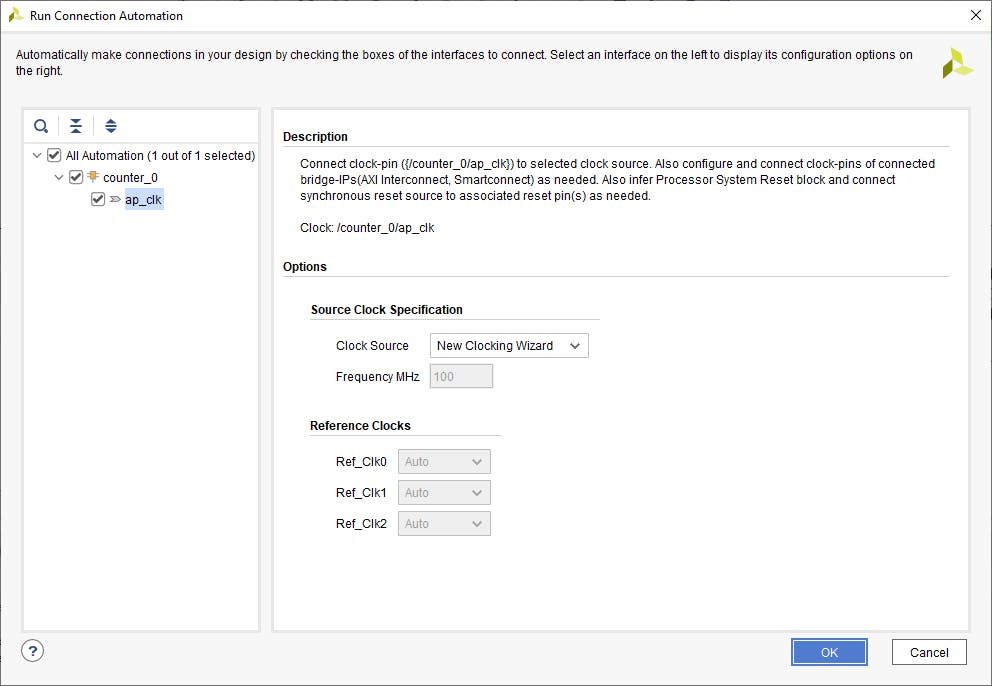

17- 單擊圖表區(qū)域頂部的“運行連接自動化”。

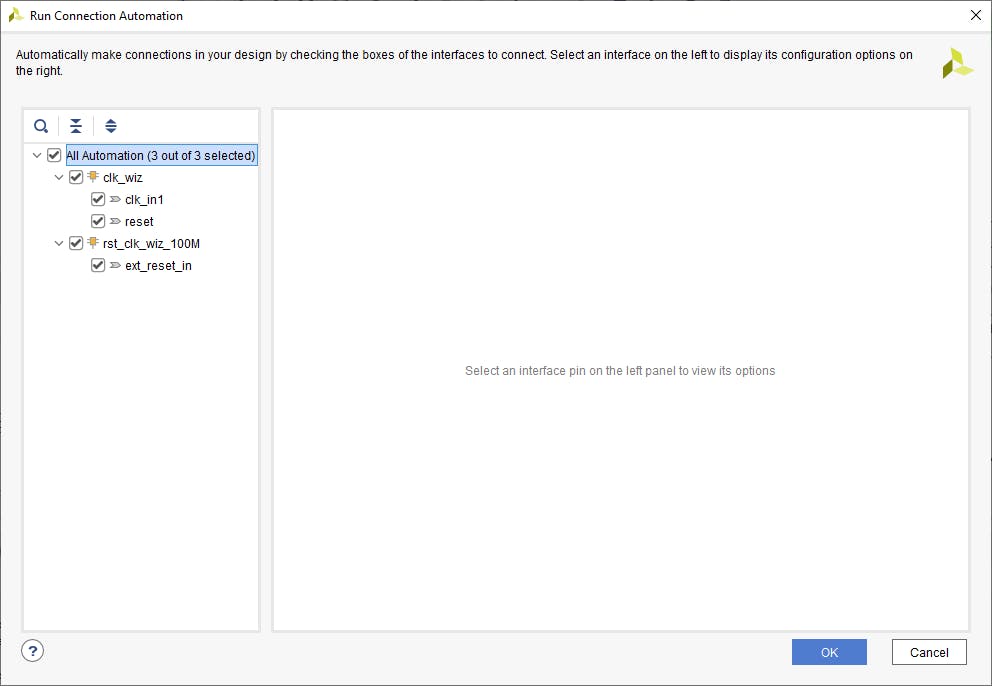

18- 再次單擊圖表區(qū)域頂部的“運行連接自動化”。

9- 在我們的計數(shù)器 IP 上選擇未連接的端口并將它們設(shè)為外部(右鍵單擊端口名稱,您將在下拉菜單中看到“設(shè)為外部”選項)。

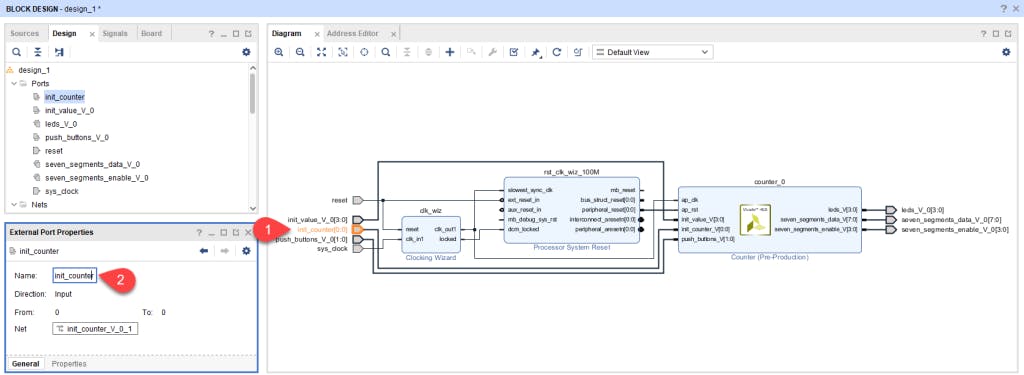

10-您可以通過選擇端口并使用“外部端口屬性”窗口來重命名端口。

init_counter_V_0 -----------> init_counter

push_buttons_V_0------------> push_buttons

init_value_V_0--------------> init_value

init_counter----------------> init_counter

leds_V_0--------------------> leds

seven_segments_data_V_0 ----> seven_segments_data

seven_segments_enable_V_0---> seven_segments_enable

11- 現(xiàn)在創(chuàng)建一個約束文件,并添加以下約束以將 IP 端口連接到具有適當 I/O 標準的 FPGA 引腳。

## Switches

set_property PACKAGE_PIN V17 [get_ports {init_value[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {init_value[0]}]

set_property PACKAGE_PIN V16 [get_ports {init_value[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {init_value[1]}]

set_property PACKAGE_PIN W16 [get_ports {init_value[2]}]?

set_property IOSTANDARD LVCMOS33 [get_ports {init_value[2]}]

set_property PACKAGE_PIN W17 [get_ports {init_value[3]}]?

set_property IOSTANDARD LVCMOS33 [get_ports {init_value[3]}]

# LEDs

set_property PACKAGE_PIN U16 [get_ports {leds[0]}]?

set_property IOSTANDARD LVCMOS33 [get_ports {leds[0]}]

set_property PACKAGE_PIN E19 [get_ports {leds[1]}]?

set_property IOSTANDARD LVCMOS33 [get_ports {leds[1]}]

set_property PACKAGE_PIN U19 [get_ports {leds[2]}]?

set_property IOSTANDARD LVCMOS33 [get_ports {leds[2]}]

set_property PACKAGE_PIN V19 [get_ports {leds[3]}]?

set_property IOSTANDARD LVCMOS33 [get_ports {leds[3]}]

#7 segment display

set_property PACKAGE_PIN W7 [get_ports {seven_segments_data[0]}]?

set_property IOSTANDARD LVCMOS33 [get_ports {seven_segments_data[0]}]

set_property PACKAGE_PIN W6 [get_ports {seven_segments_data[1]}]?

set_property IOSTANDARD LVCMOS33 [get_ports {seven_segments_data[1]}]

set_property PACKAGE_PIN U8 [get_ports {seven_segments_data[2]}]?

set_property IOSTANDARD LVCMOS33 [get_ports {seven_segments_data[2]}]

set_property PACKAGE_PIN V8 [get_ports {seven_segments_data[3]}]?

set_property IOSTANDARD LVCMOS33 [get_ports {seven_segments_data[3]}]

set_property PACKAGE_PIN U5 [get_ports {seven_segments_data[4]}]?

set_property IOSTANDARD LVCMOS33 [get_ports {seven_segments_data[4]}]

set_property PACKAGE_PIN V5 [get_ports {seven_segments_data[5]}]?

set_property IOSTANDARD LVCMOS33 [get_ports {seven_segments_data[5]}]

set_property PACKAGE_PIN U7 [get_ports {seven_segments_data[6]}]?

set_property IOSTANDARD LVCMOS33 [get_ports {seven_segments_data[6]}]

set_property PACKAGE_PIN V7 [get_ports seven_segments_data[7]]?

set_property IOSTANDARD LVCMOS33 [get_ports seven_segments_data[7]]

set_property PACKAGE_PIN U2 [get_ports {seven_segments_enable[0]}]?

set_property IOSTANDARD LVCMOS33 [get_ports {seven_segments_enable[0]}]

set_property PACKAGE_PIN U4 [get_ports {seven_segments_enable[1]}]?

set_property IOSTANDARD LVCMOS33 [get_ports {seven_segments_enable[1]}]

set_property PACKAGE_PIN V4 [get_ports {seven_segments_enable[2]}]?

set_property IOSTANDARD LVCMOS33 [get_ports {seven_segments_enable[2]}]

set_property PACKAGE_PIN W4 [get_ports {seven_segments_enable[3]}]?

set_property IOSTANDARD LVCMOS33 [get_ports {seven_segments_enable[3]}]

#Buttons

set_property PACKAGE_PIN T18 [get_ports push_buttons[0]]?

set_property IOSTANDARD LVCMOS33 [get_ports push_buttons[0]]

set_property PACKAGE_PIN W19 [get_ports init_counter[0]]?

set_property IOSTANDARD LVCMOS33 [get_ports init_counter[0]]

set_property PACKAGE_PIN U17 [get_ports push_buttons[1]]?

set_property IOSTANDARD LVCMOS33 [get_ports push_buttons[1]]

12- 現(xiàn)在右鍵單擊圖表區(qū)域內(nèi)的某處并選擇“驗證設(shè)計”選項。

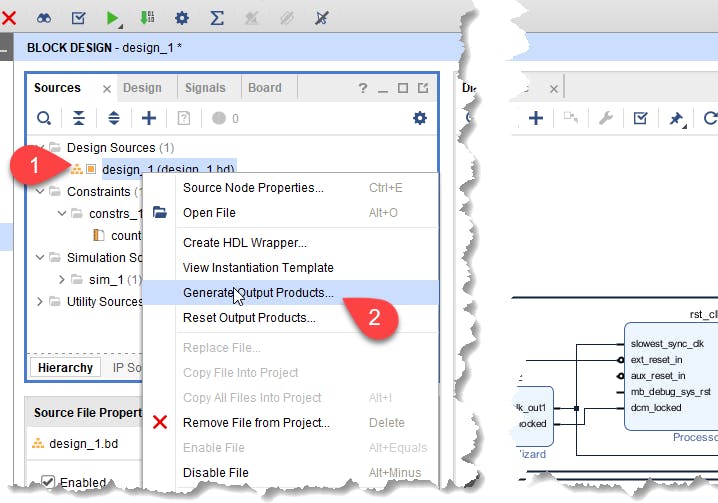

13-成功驗證設(shè)計后,右鍵單擊“Design Sources”文件夾下的“ design_1 ”并選擇“Generate Output Products...”

14- 然后,再次右鍵單擊“Design Sources”文件夾下的“design_1”并選擇“Create HDL Wrapper...”

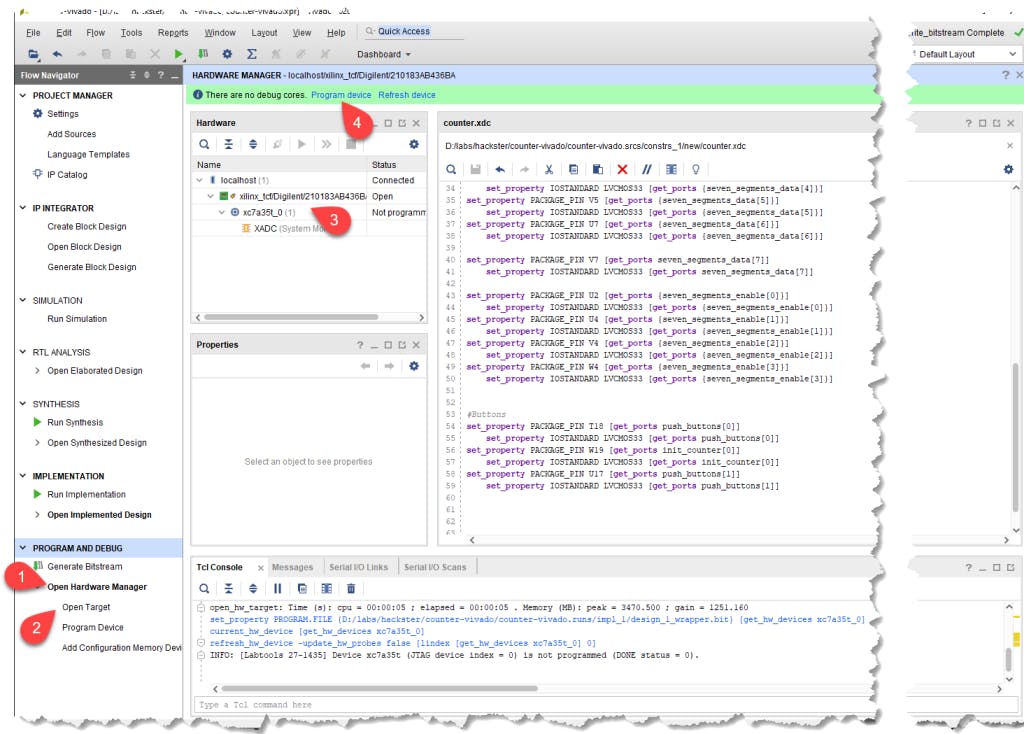

15- 現(xiàn)在單擊左側(cè) Flow Navigator 中 PROGRAM and DEBUG 下的“Generate Bitstream”選項。

第 3 階段:電路板編程

1- 最后,對電路板進行編程并檢查設(shè)計。

如果您對使用 HLS 進行設(shè)計感興趣,請查看具有FPGA 高級合成的數(shù)字系統(tǒng)設(shè)計:組合電路

- 簡單的0至9計數(shù)器開源分享

- 單片機 -定時/計數(shù)器的初始化編程及應(yīng)用

- 51單片機的計時器和計數(shù)器

- 51單片機單個數(shù)碼管0-9循環(huán)秒計數(shù)

- 51單片機定時/計數(shù)器的工作原理

- C51單片機中的定時器和計數(shù)器的詳細介紹

- 在51平臺下初始化文件的引入導致全局變量無法初始化的問題如何解決

- 單片機計數(shù)器的應(yīng)用資料說明

- 使用51單片機的定時器和計數(shù)器T0實現(xiàn)外部計數(shù)proteus仿真實例

- 使用單片機設(shè)計0到9999計數(shù)器并帶有暫停清零功能的程序資料免費下載

- 如何排除代碼編寫器Studio 2和2.10的初始化問題 4次下載

- SEED-DEC2812初始化函數(shù)說明 11次下載

- 定時計數(shù)器初始化 16次下載

- Proteus之定時_計數(shù)器0用于計數(shù)的應(yīng)用 0次下載

- 單片直接驅(qū)動數(shù)碼管的計數(shù)器程序 187次下載

- 同步計數(shù)器和異步計數(shù)器的區(qū)別 7.9k次閱讀

- 字符型、指針型等變量等該如何初始化 2.6k次閱讀

- 計數(shù)器怎么用 計數(shù)器的作用有哪些 9.3k次閱讀

- SIMATIC S7-1500 PLC加減計數(shù)器簡述 9.1k次閱讀

- 什么是指定初始化? 1.7k次閱讀

- 西門子S7-300PLC高速計數(shù)器的計數(shù)方式簡介 8.4k次閱讀

- SCL語言之加計數(shù)-計數(shù)器函數(shù)S_CU 2.8k次閱讀

- RT-Thread自動初始化機制 3.9k次閱讀

- 如何使用SPI總線設(shè)計正交編碼器計數(shù)器 5.7k次閱讀

- 鴻蒙內(nèi)核源碼:內(nèi)核空間是怎么初始化的? 2.6k次閱讀

- 計數(shù)器函數(shù)S_CU的操作步驟 1w次閱讀

- 單片機定時器/計數(shù)器的結(jié)構(gòu) 9.2k次閱讀

- 如何有效地對神經(jīng)網(wǎng)絡(luò)參數(shù)進行初始化 4.8k次閱讀

- PCIe總線必須要先完成Flow Control初始化 8.7k次閱讀

- 8253初始化程序分享_8253應(yīng)用案例 2.3w次閱讀

下載排行

本周

- 1PD取電芯片 ECP5702規(guī)格書

- 0.88 MB | 3次下載 | 免費

- 2氮化鎵GaN FET/GaN HEMT 功率驅(qū)動電路選型表

- 0.10 MB | 2次下載 | 免費

- 3EMC PCB設(shè)計總結(jié)

- 0.33 MB | 2次下載 | 免費

- 4PD取電芯片,可取5/9/12/15/20V電壓ECP5702數(shù)據(jù)手冊

- 0.88 MB | 1次下載 | 免費

- 5飛騰FT2000-4 COM Express核心板技術(shù)手冊0603

- 1.22 MB | 1次下載 | 免費

- 6飛騰S5000C-64雙路服務(wù)器系列應(yīng)用宣傳冊--一乘科技

- 945.81 KB | 1次下載 | 免費

- 7瑞薩系列-米爾RZ/T2H核心板開發(fā)板 高端MPU,驅(qū)控一體單芯片方案

- 3.07 MB | 次下載 | 免費

- 8在應(yīng)用中使用VEML6031X00芯片

- 0.84 MB | 次下載 | 2 積分

本月

- 1美的電磁爐電路原理圖資料

- 4.39 MB | 22次下載 | 10 積分

- 2反激式開關(guān)電源設(shè)計解析

- 0.89 MB | 16次下載 | 5 積分

- 3耗盡型MOS FET產(chǎn)品目錄選型表

- 0.14 MB | 3次下載 | 免費

- 4PD取電芯片 ECP5702規(guī)格書

- 0.88 MB | 3次下載 | 免費

- 5氮化鎵GaN FET/GaN HEMT 功率驅(qū)動電路選型表

- 0.10 MB | 2次下載 | 免費

- 6EMC PCB設(shè)計總結(jié)

- 0.33 MB | 2次下載 | 免費

- 7PC5200 700V_10A GaN HEMT驅(qū)動器數(shù)據(jù)手冊

- 1.63 MB | 1次下載 | 免費

- 81節(jié)電池用電池保護IC S-8261D系列數(shù)據(jù)手冊

- 3.07 MB | 1次下載 | 1 積分

總榜

- 1matlab軟件下載入口

- 未知 | 935137次下載 | 10 積分

- 2開源硬件-PMP21529.1-4 開關(guān)降壓/升壓雙向直流/直流轉(zhuǎn)換器 PCB layout 設(shè)計

- 1.48MB | 420064次下載 | 10 積分

- 3Altium DXP2002下載入口

- 未知 | 233095次下載 | 10 積分

- 4電路仿真軟件multisim 10.0免費下載

- 340992 | 191457次下載 | 10 積分

- 5十天學會AVR單片機與C語言視頻教程 下載

- 158M | 183360次下載 | 10 積分

- 6labview8.5下載

- 未知 | 81605次下載 | 10 積分

- 7Keil工具MDK-Arm免費下載

- 0.02 MB | 73831次下載 | 10 積分

- 8LabVIEW 8.6下載

- 未知 | 65991次下載 | 10 積分

電子發(fā)燒友App

電子發(fā)燒友App

創(chuàng)作

創(chuàng)作 發(fā)文章

發(fā)文章 發(fā)帖

發(fā)帖  提問

提問  發(fā)資料

發(fā)資料 發(fā)視頻

發(fā)視頻 上傳資料賺積分

上傳資料賺積分

評論