引言

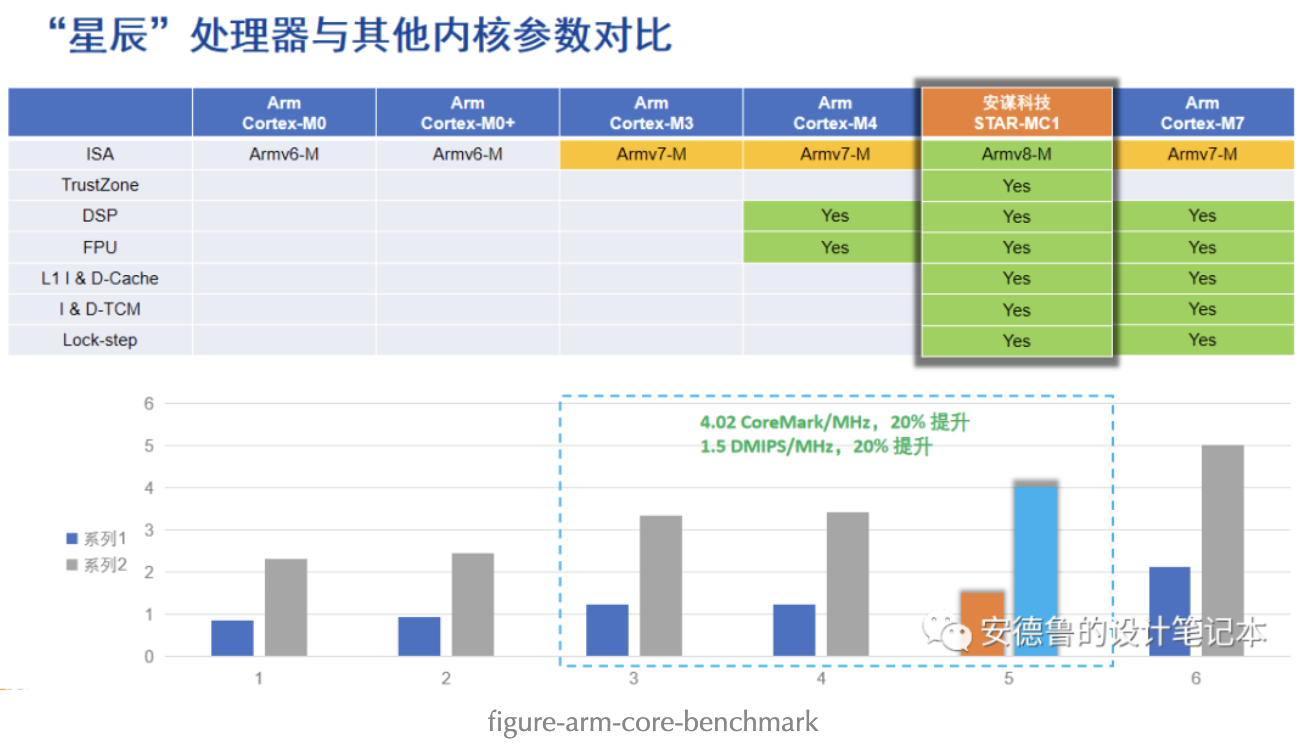

目前,靈動微控制器產品體系中,適配了MicroPython的,有MM32F3(MM32F3273G9P,Arm Cortex-M3)和MM32F5(MM32F5277E9P,ArmChina STAR-MC1),從官方數據來看,使用星辰處理器(STAR-MC1)的MM32F5對指令的處理效率要高于使用Cortex-M3處理器的MM32F3。如圖x所示。

圖x 星辰處理器同其他Arm處理器內核對比

然而,同一份MicroPython的啟動過程,在使用同樣主頻(120MHz)的情況下,在MM32F5平臺上運行,總是莫名其妙地慢好多。。。昨天跟同事Hao聊SDK的樣例工程對Cache問題的處理策略時,偶然意識到,早期為MM32F5適配MicroPython的時候沒有考慮過Cache,隨即趕緊翻出來MicroPython的代碼,果然沒開。好吧,更新MicroPython項目下MM32F5平臺的啟動代碼,替換來自于SDK中的system_mm32f5277e.c和system_mm32f5277e.h文件。

/*

* Copyright 2022 MindMotion Microelectronics Co., Ltd.

* All rights reserved.

*

* SPDX-License-Identifier: BSD-3-Clause

*/

#include "hal_device_registers.h"

#if defined (__VTOR_PRESENT) && (__VTOR_PRESENT == 1U)

extern uint32_t __VECTOR_TABLE;

#endif

void SystemInit(void)

{

#if defined (__FPU_PRESENT ) && (__FPU_PRESENT == 1U)

#if defined(__FPU_USED) && (__FPU_USED == 1u)

SCB- >CPACR |= (SCB_CPACR_CP10_MASK | SCB_CPACR_CP11_MASK); /* set CP10, CP11 Full Access */

#endif

#endif /* __FPU_PRESENT */

#if defined (__ICACHE_PRESENT )&& (__ICACHE_PRESENT == 1U)

#ifndef ICACHE_DISABLED

if (SCB- >CLIDR & SCB_CLIDR_IC_Msk)

{

SCB_EnableICache();

}

#endif /* DCACHE_DISABLED */

#endif /* __ICACHE_PRESENT */

#if defined (__DCACHE_PRESENT) && (__DCACHE_PRESENT == 1U)

#ifndef DCACHE_DISABLED

if (SCB- >CLIDR & SCB_CLIDR_IC_Msk)

{

SCB_EnableDCache();

}

#endif /* DCACHE_DISABLED */

#endif /* __DCACHE_PRESENT */

}

/* EOF. */

其中,如果沒有調用SCB_EnableICache()和SCB_EnableDCache()函數,默認關閉ICache和DCache,配置宏__ICACHE_PRESENT和__DCACHE_PRESENT來自于MM32F5270的芯片頭文件mm32f5277e.h。

#define __STAR_REV 0x0100U /* Core revision r1p0 */

#define __SAUREGION_PRESENT 0U /* SAU regions present */

#define __MPU_PRESENT 1U /* MPU present */

#define __VTOR_PRESENT 1U /* VTOR present */

#define __NVIC_PRIO_BITS 3U /* Number of Bits used for Priority Levels */

#define __Vendor_SysTickConfig 0U /* Set to 1 if different SysTick Config is used */

#define __FPU_PRESENT 1U /* FPU present */

#define __DSP_PRESENT 1U /* DSP extension present */

#define __ICACHE_PRESENT 1U /* Define if an ICACHE is present or not */

#define __DCACHE_PRESENT 1U /* Define if an DCACHE is present or not */

編譯,驗證。找來兩塊之前下載了MicroPython固件的MM32F5開發板,向其中一塊板子下載啟用ICache和DCache之后的新固件。運行程序后,同使用之前版本固件的程序相比,果然有明顯的提升。

圖中板子運行程序啟動MicroPython啟動流程后,執行文件系統中Python源文件,閃爍小燈。圖中下方的板子使用了啟用Cache的程序,明顯先完成MicroPython啟動過程,先開始執行閃爍小燈的程序。

提交更新到代碼倉庫。Bingo!

commit 46372ed15d5769b25775a209c56d62c4cfc3ac5d (HEAD - > master, origin/master, origin/HEAD)

Author: Andrew SU < suyong_yq@126.com >

Date: Wed Jun 14 11:02:06 2023 +0800

update the startup code to enable the icache for mm32f5.

- this fix would accelerate the speed of running the instruction

sequence on mm32f5, which has the icache and dcache integrated.

Signed-off-by: Andrew SU < suyong_yq@126.com >

啟用Cache后,之前在MM32F5微控制器平臺上運行MicroPython小概率會出現hardfault的問題也得到的緩解,頗有“治好了某人多年老寒腿”的趕腳。^v^。

Cache的工作原理

Cache主要解決高速的CPU訪問低速的存儲器均衡速度差的問題,Cache通過預取數據/命令的機制,低速但整塊地從低速存儲器中取數據塊,然后快速但串行地向CPU送數據流。高速的處理器大多使用哈佛結構,即使用指令總線和數據總線分別取指令和數據,對應有ICache和DCache。

Cache能夠有效工作基于幾個基本前提:

- 空間局部性:在最近的未來,使用到的信息和當前使用的信息在空間上會是鄰近的。這個因為數據大部分都是連續存儲的。所以主存當中的數據都是成塊傳輸到Cache當中。

- 時間局部性:在最近的未來,使用到的信息可能是當前正在使用的信息。由于CPU本質上一個死循環,里面還有很多小循環的運行和操作,所以當前使用到的數據很可能會在循環當中,這樣當前的數據有可能會在將來在再被調用一次。

另外,關于Cache還有其余部分需要了解:

- Cache與主存的映射方式:解決主存內數據塊和Cache當中數據塊的對應關系。

- 替換算法:Cache小,主存大。如果Cache中數據存滿了之后,如何操作。

- Cache寫策略:如果CPU修改了Cache中的副本,如何確保Cache中的數據和主存中的母本數據保持一致。

關于Cache的工作原理,以及設計機制,可參考計算機專業考研四大專業課之《計算機體系結構》,以及參考文獻中的《一文搞懂Cache基本原理》。

需要關閉DCache的情況

在微控制器系統中,有時會需要直接使用內存里的數據同外設交互,而不進入CPU,例如使用DMA(另一個總線主機AHB Master,但不需要Cache功能)相關,這種場景下,使用Cache的意義就不大了,甚至可能會出現數據不一致的風險,此時,就需要關閉Cache才能讓系統正常工作。具體來說,ICache可以繼續啟用,畢竟指令都是送到CPU中執行,但DCache需要關掉,否則通過CPU寫入到內存的數據未能及時同步物理內存時(基于Cache的寫策略),啟動DMA時搬運的數據不一定是實際需要傳送的數據。另外,所有使用到“內嵌”DMA的外設模塊的工程中,也需要小心謹慎地使用DCache,例如一些USB外設、ENET外設、顯示加速器、以數據塊為操作單元的加速計算模塊等。

關ICache的情況雖然不多,但也存在,例如在涉及IAP應用中,從存放指令的介質中擦除指令、寫入新指令后,再讀指令,實際的新指令可能尚未替換到ICache中存放的舊指令,導致程序執行錯誤。

魚和熊掌都想要

關閉DCache之后,CPU讀數據的速度會明顯慢很多,例如本文一開始展現的情況。怎樣才能提升訪問訪問速度的同時,又能確保數據一致性呢?總不會人為頻繁地開關Cache吧(很多微控制器對啟動Cache的時機也有特別要求,需要在運行應用程序的一開始就要開啟)。這里有兩種可能的思路,供大家參考:

- 使用內存保護單元MPU

- 使用內存隔離/同步指令

這兩種方法,分別是在空間上和時間上對數據進行隔離,控制僅在必要的空間上或時間上啟用和關閉Cache。

使用內存保護單元MPU

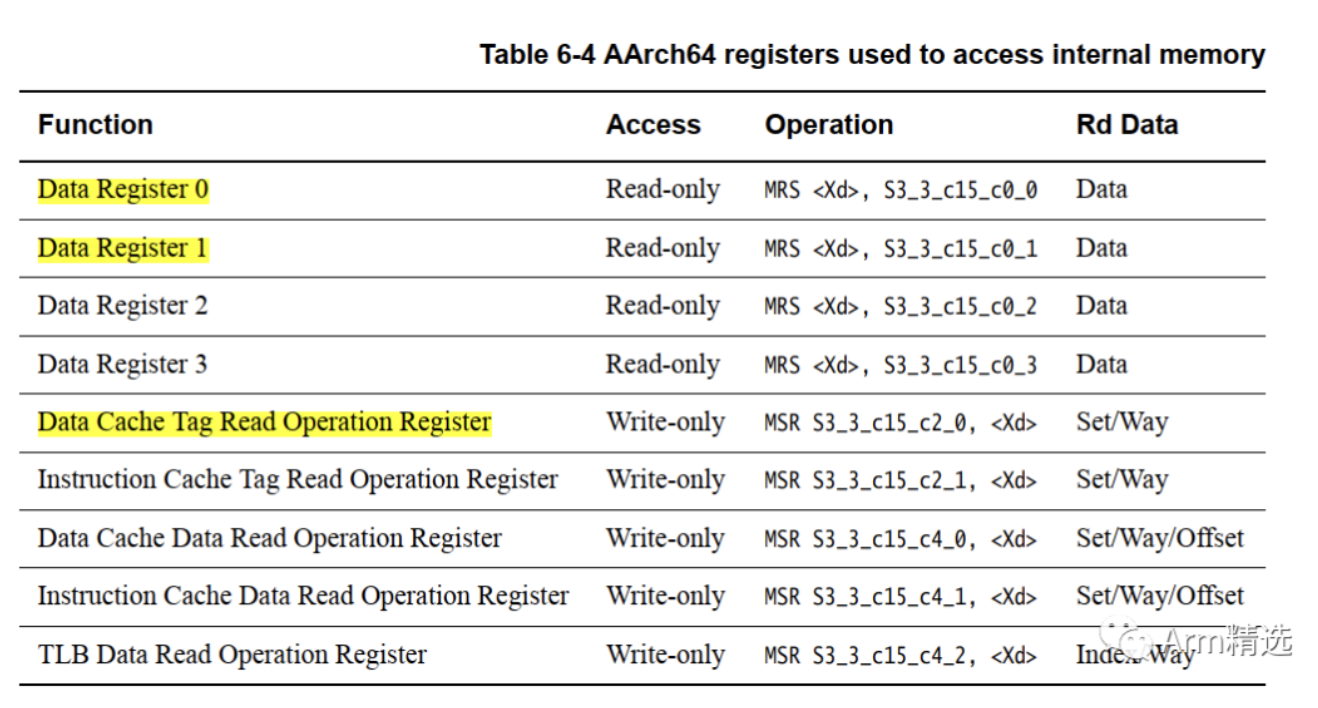

MPU(Memory Protection Unit)內存保護單元在ARMv7-M架構下被引入。在 ARMv7-M架構下,Cortex-M3和Cortex-M4處理器對 MPU 都是選配的,不是必須的。ARMv8-M架構下繼續沿用了MPU,星辰處理器STAR-MC1就使用了ARMv8-M。

MPU是一個可以編程的設備模塊,可用來定義內存空間的屬性,比如特權指令和非特權指令,以及Cache是否可訪問。ARMv7-M通常支持8個region,每個region 代表一段連續的區域。

關于MPU的用法,可參見參考文獻中的《ARM-MPU內存保護單元詳解》和《Armv8-M Architecture Reference Manual》。

使用內存隔離/同步指令

ARM的指令集中,有內存隔離指令DMB(Data Memory Barrier)、DSB(Data Synchronization Barrier)和ISB(Instruction Synchronization Barrier):

- 數據存儲器隔離。DMB 指令保證: 僅當所有在它前面的存儲器訪問操作都執行完畢后,才提交(commit)在它后面的存儲器訪問操作。

- 數據同步隔離。比 DMB 嚴格: 僅當所有在它前面的存儲器訪問操作都執行完畢后,才執行在它后面的指令(亦即任何指令都要等待存儲器訪問操作——譯者注)。

- 指令同步隔離。最嚴格:它會清洗流水線,以保證所有它前面的指令都執行完畢之后,才執行它后面的指令。

在一些ARM程序代碼中,會用到__DSB() 指令,特別是在一些中斷處理函數中。例如:

//中斷定時器PIT中斷處理函數

void PIT_LED_HANDLER(void)

{

/* Clear interrupt flag.*/

PIT_ClearStatusFlags(PIT, kPIT_Chnl_0, kPIT_TimerFlag);

pitIsrFlag = true;

__DSB();

}

程序通過中斷信號進入中斷處理函數時,首先應當清除相應的中斷標志位,但有些CPU的時鐘太快,快于中斷使用的時鐘,就會出現清除中斷標志的動作還未完成,CPU就又一次重新進入同一個中斷處理函數,導致死循環,__DSB() 指令的作用就是避免上述情況的發生。

總結

本文從修復MicroPython啟動程序在MM32F5微控制器上比較慢的問題,體驗了星辰處理器中Cache的作用。簡單介紹了Cache的工作原理和機制,重點介紹了使用Cache可能存在的風險,并進一步探討了如何能用到Cache高速存取的同時避免數據不一致的情況。

電子發燒友App

電子發燒友App

評論