1.引言

本文針對紅外圖像處理系統(tǒng)的實(shí)時(shí)性要求,提出了基于DSP+FPGA+ASIC的圖像處理架構(gòu)。

隨著紅外焦

2010-07-22 15:18:50 1160

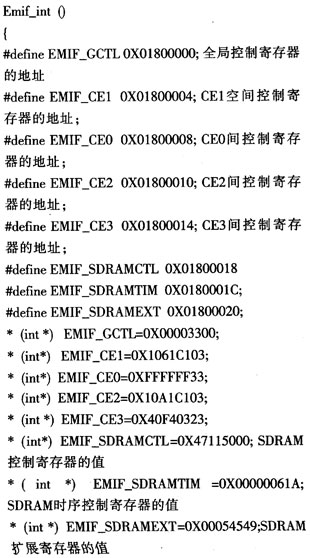

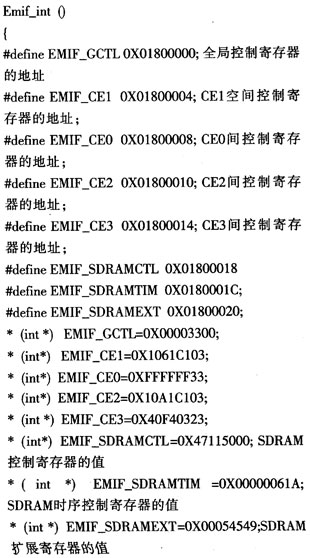

1160 高頻脈沖噪聲對數(shù)字信號處理系統(tǒng)危害性最大。為了提高系統(tǒng)的抗干擾性能,在數(shù)字信號處理系統(tǒng)中可

2010-12-17 11:00:34 4996

4996 什么是DSP圖像處理系統(tǒng)?DSP圖像處理系統(tǒng)中信號完整性的問題是什么?有哪些解決方案?

2021-06-01 06:40:35

接下來,我會開一系列學(xué)習(xí)使用MATLAB來設(shè)計(jì)FPGA為DSP的過程實(shí)時(shí)信號處理系統(tǒng)要求必須具有處理大數(shù)據(jù)量的能力,以保證系統(tǒng)的實(shí)時(shí)性;其次對系統(tǒng)的體積、功耗、穩(wěn)定性等也有較嚴(yán)格的要求。實(shí)時(shí)信號處理

2015-06-01 11:47:36

ADSP2106x SHARC是一個(gè)適用于語音、通信和圖像處理的高速32位數(shù)字信號處理器。該芯片是基于ADSP21000系列DSP芯片發(fā)展起來的一個(gè)完整的單片系統(tǒng),增加了一個(gè)雙口片內(nèi)SRAM,并集成

2019-07-19 08:16:35

和科研單位尚未見有自主知識產(chǎn)權(quán)的研究成果或產(chǎn)品出現(xiàn),本文討論了以DSP為核心構(gòu)建數(shù)字音頻處理系統(tǒng)時(shí)需注意的幾個(gè)問題,分析自行研制的以DSP56364為核心的吉他音效處理系統(tǒng).

2011-03-06 22:28:27

為解決高速數(shù)字圖像處理系統(tǒng)和實(shí)時(shí)性相沖突的要求,設(shè)計(jì)了以多DSP(數(shù)字信號處理器TMS320C6416)和現(xiàn)場可編程門陣列(FPGA)相結(jié)合的實(shí)時(shí)圖像處理系統(tǒng)。重點(diǎn)介紹了該系統(tǒng)的硬件資源選擇、基本組

2021-04-28 06:14:48

在現(xiàn)代戰(zhàn)爭模式中,導(dǎo)彈定向爆破能大幅提高作用于目標(biāo)方向的殺傷能量,使導(dǎo)彈獲得更大的命中和毀傷概率、作戰(zhàn)能力。引信作為導(dǎo)彈的重要組成部件,具有方位識別能力是實(shí)現(xiàn)導(dǎo)彈定向爆破的前提條件。信號處理系統(tǒng)作為

2020-04-20 07:24:20

處理數(shù)字信號不僅造成處理速度慢,影響PC機(jī)對數(shù)據(jù)的管理,還會影響信號處理系統(tǒng)的實(shí)時(shí)性。因此,提出一種方案把數(shù)字信號處理部分從PC機(jī)軟件中分離出來交給DSP處理,DSP處理完畢后再把數(shù)據(jù)交還PC機(jī)進(jìn)行

2018-12-17 11:29:06

基于DSP的圖像處理系統(tǒng)的應(yīng)用研究摘要 本文介紹了一種基于FPGA+DSP結(jié)構(gòu)的具有通用性、可擴(kuò)充性的高速數(shù)字圖像處理系統(tǒng)硬件平臺。重點(diǎn)介紹了以高速數(shù)字信號處理器TMS320DM642

2012-12-19 11:05:08

基于DSP的通用語音信號處理系統(tǒng)的設(shè)計(jì)

2020-05-28 09:15:53

基于C55x DSP核芯片實(shí)現(xiàn)基帶信號處理系統(tǒng)的設(shè)計(jì)

2020-12-21 06:19:01

圖像數(shù)據(jù)處理的工作原理是什么?基于FPGA+DSP的圖像處理系統(tǒng)待如何去設(shè)計(jì)?

2021-06-02 06:54:28

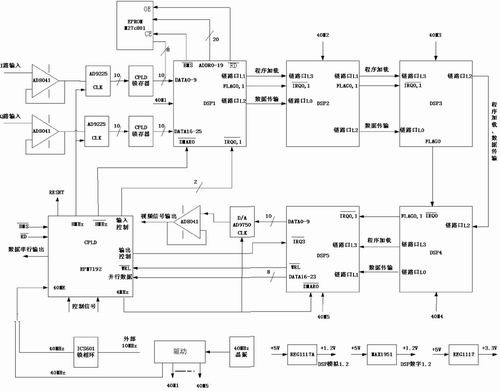

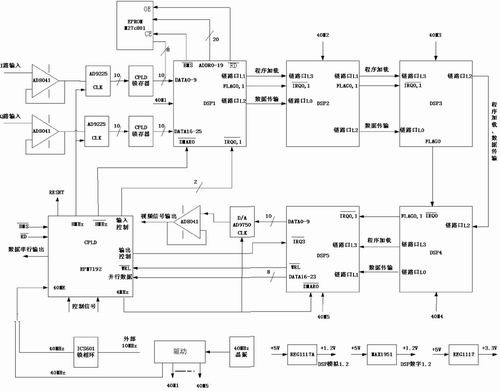

DSP并行處理系統(tǒng)的原理圖如圖1所示。整個(gè)雷達(dá)信號處理系統(tǒng)以高可靠性CPCI工控機(jī)為平臺,內(nèi)置不同功能的信號處理板。板間的數(shù)據(jù)傳輸通過CPCI接口完成。根據(jù)雷達(dá)信號處理系統(tǒng)的任務(wù)分 配,本系統(tǒng)負(fù)責(zé)完成

2019-05-21 05:00:19

基于GPS的無人機(jī)自動(dòng)著陸控制系統(tǒng)設(shè)計(jì)與實(shí)現(xiàn)

2013-09-26 13:28:36

基于labview的虛擬信號處理系統(tǒng)

2012-05-07 16:21:11

各位燒友,,有沒有關(guān)于 基于labview語音信號處理系統(tǒng)的資料呢!!跪求啊!!!在此先謝過!676248796@qq.com

2012-10-20 09:39:36

隨著紅外探測技術(shù)迅猛的發(fā)展,當(dāng)今紅外實(shí)時(shí)圖像處理系統(tǒng)所要處理的數(shù)據(jù)量越來越大,速度要求也越來越快,利用目前主流的單DSP+ FPGA硬件架構(gòu)進(jìn)行較為復(fù)雜的圖像處理算法運(yùn)算時(shí),有時(shí)就顯得有些捉襟見肘了

2019-11-08 06:31:26

本文設(shè)計(jì)了一套基于DSP的陣列聲波信號采集與處理系統(tǒng),此系統(tǒng)將作為正在研制的陣列聲波測井儀中的一部分,應(yīng)用于油田勘探中。

2021-05-31 06:26:35

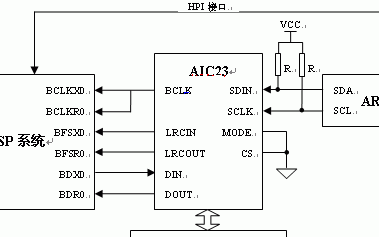

本文闡述了基于信號處理和嵌入式應(yīng)用的音頻處理系統(tǒng)的設(shè)計(jì)和實(shí)現(xiàn)。

2021-06-08 07:07:19

隨著紅外探測技術(shù)迅猛的發(fā)展,當(dāng)今紅外實(shí)時(shí)圖像處理系統(tǒng)所要處理的數(shù)據(jù)量越來越大,速度要求也越來越快,利用目前主流的單DSP+ FPGA硬件架構(gòu)進(jìn)行較為復(fù)雜的圖像處理算法運(yùn)算時(shí),有時(shí)就顯得有些捉襟見肘了

2019-08-23 08:29:27

怎樣去設(shè)計(jì)音頻信號采集與處理系統(tǒng)的硬件電路?怎樣去設(shè)計(jì)音頻信號采集與處理系統(tǒng)的軟件程序?

2021-06-08 06:51:40

為什么要設(shè)計(jì)激光多譜勒信號處理系統(tǒng)?激光多譜勒信號處理系統(tǒng)有哪些優(yōu)點(diǎn)?怎樣去設(shè)計(jì)激光多譜勒信號處理系統(tǒng)?如何去驗(yàn)證激光多譜勒信號處理系統(tǒng)?

2021-04-15 06:25:40

傳感可在無人機(jī)著陸時(shí)的探測距離、方案成本以及不同表面的可靠性方面良好運(yùn)行。無人機(jī)地面跟蹤和著陸的共同要求是能夠可靠地檢測到距離地面 5 米高的距離。假設(shè)信號調(diào)節(jié)和處理正確,40-60kHz 范圍內(nèi)

2020-02-21 09:46:17

基于VxWorks的多DSP并行處理系統(tǒng)的實(shí)現(xiàn)

2009-03-29 12:31:18 17

17 介紹一種基于DSP和以太網(wǎng)的數(shù)據(jù)采集處理系統(tǒng)。論述數(shù)據(jù)采集處理系統(tǒng)中的以太網(wǎng)應(yīng)用,分析系統(tǒng)的硬件設(shè)計(jì)方案,提出基于實(shí)時(shí)操作系統(tǒng)DSP/BIOS 進(jìn)行軟件設(shè)計(jì)的思路和實(shí)現(xiàn)方法。

2009-04-16 09:56:45 24

24 介紹一種基于DSP和以太網(wǎng)的數(shù)據(jù)采集處理系統(tǒng)。論述數(shù)據(jù)采集處理系統(tǒng)中的以太網(wǎng)應(yīng)用,分析系統(tǒng)的硬件設(shè)計(jì)方案,提出基于實(shí)時(shí)操作系統(tǒng)DSP/BIOS 進(jìn)行軟件設(shè)計(jì)的思路和實(shí)現(xiàn)方法。

2009-05-15 14:19:19 23

23 根據(jù)電力監(jiān)控系統(tǒng)的要求,提出一種基于FPGA技術(shù)的多路交流信號采集與處理系統(tǒng)的設(shè)計(jì)方法。分析整個(gè)系統(tǒng)的結(jié)構(gòu),并討論FPGA內(nèi)部硬件資源的劃分和軟件的設(shè)計(jì)方案,以及各個(gè)功能

2009-05-16 14:47:58 27

27 本文研究了一種基于TMS320C5402 芯片的數(shù)字圖像處理硬件系統(tǒng),并使用VB 進(jìn)行可視化的處理。在該圖像處理系統(tǒng)中,利用DSP 上的鍵盤模塊將各種圖像處理方法結(jié)合起來,利用DSP 串

2009-06-06 13:36:50 26

26 設(shè)計(jì)了一種基于FPGA 和DSP 的光纖信號實(shí)時(shí)處理系統(tǒng),介紹了系統(tǒng)的硬件組成和工作原理。該系統(tǒng)采用FPGA 實(shí)現(xiàn)數(shù)據(jù)的高速采集和邏輯控制,用DSP 實(shí)現(xiàn)傳感信號的全數(shù)字解調(diào),分析了載

2009-06-19 11:17:43 24

24 以DSP TMS320C6416 為核心處理器, 設(shè)計(jì)了一種通用的MPEG-4實(shí)時(shí)圖象處理系統(tǒng)。文中對系統(tǒng)的硬件系統(tǒng)及軟件設(shè)計(jì)進(jìn)行了詳細(xì)的介紹。其中視頻采集、運(yùn)動(dòng)估計(jì)算法和軟件的優(yōu)化是保證本

2009-08-21 11:07:29 15

15 本文介紹了腦電信號處理的兩種基本方法及其優(yōu)缺點(diǎn), 分析了DSP 尤其是TMS320LF2407 的主要特點(diǎn),闡述了基于TMS320LF2407DSP 的16 通道腦電信號處理系統(tǒng)的硬件和軟件的實(shí)現(xiàn)方法。

2009-08-31 08:32:11 45

45 簡要分析了DSP+FPGA系統(tǒng)的特點(diǎn)和優(yōu)越性,并且結(jié)合一個(gè)實(shí)時(shí)信號處理板的開發(fā),提出在此類系統(tǒng)中,F(xiàn)PGA設(shè)計(jì)的幾個(gè)關(guān)鍵問題,并且給出了詳實(shí)的分析和解決方案。

2009-09-02 17:44:44 24

24 本文研究了基于DSP 的語音信號處理系統(tǒng),分析了TI 公司的信號處理器TMS320VC5402 與音頻模擬芯片TLC320AC01(以下簡稱AC01)的結(jié)構(gòu)特點(diǎn),描述了兩者之間的多通道緩沖串口的硬件

2009-12-14 11:17:13 73

73 基于DSP和DSP/BIOS的實(shí)時(shí)雷達(dá)信號采集與處理系統(tǒng):介紹了一種在實(shí)時(shí)操作系統(tǒng)DSP和DSP/BIOS 平臺下的雷達(dá)信號實(shí)時(shí)采集" 處理與傳輸系統(tǒng)的設(shè)計(jì)和實(shí)現(xiàn)! 利用Tms320c6416DSP強(qiáng)大的數(shù)據(jù)處理

2010-01-16 16:59:46 25

25 介紹了數(shù)字水準(zhǔn)儀數(shù)據(jù)采集和處理系統(tǒng)的原理與設(shè)計(jì),設(shè)計(jì)一種基于定點(diǎn)DSP TMS320VC5402的信號采集與處理系統(tǒng),該系統(tǒng)應(yīng)用了美國德州儀器(TI)公司生產(chǎn)的8位半閃速結(jié)構(gòu)模數(shù)轉(zhuǎn)換器,采用FI

2010-07-17 17:40:28 9

9 摘 要:本文是基于ADSP-TS101S的多芯片數(shù)字信號處理系統(tǒng)的實(shí)現(xiàn)方案。該系統(tǒng)應(yīng)用于某雷達(dá)的信號處理機(jī)。文中首先介紹了多片TigerSHARC DSP芯片構(gòu)成的信號處理系統(tǒng)組成;其次估計(jì)系統(tǒng)的運(yùn)算量,所需計(jì)算時(shí)間;最后具體說明了CPLD產(chǎn)生復(fù)位信號及并-串轉(zhuǎn)換功能實(shí)現(xiàn)的方法。

2006-03-11 13:17:45 1220

1220

基于DSP的圖象采集與處理系統(tǒng)的設(shè)計(jì)

圖像處理系統(tǒng)的一個(gè)關(guān)鍵問題就是數(shù)據(jù)量龐大,數(shù)據(jù)處理相關(guān)性高,實(shí)時(shí)實(shí)現(xiàn)比較困難。即使采用高速單片機(jī)也無法

2009-04-22 20:01:19 1658

1658

摘要:簡要敘述了常用的信號處理系統(tǒng)的類型與處理機(jī)結(jié)構(gòu),介紹了正逐步得到廣泛應(yīng)用的DSP+FPGA處理機(jī)結(jié)構(gòu),在此基礎(chǔ)上提出了一種實(shí)時(shí)信號處理的線性流水陣列,

2009-06-20 14:26:40 1015

1015

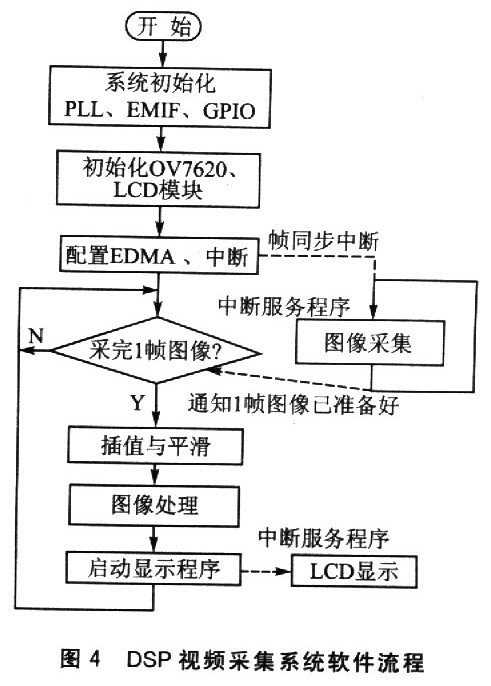

基于DSP的實(shí)時(shí)圖像處理系統(tǒng)

引言

本文設(shè)計(jì)了基于TMS320C6000系列DSP的MPEG-4編碼器。將攝像頭獲取的圖像以MPEG-4標(biāo)準(zhǔn)進(jìn)行實(shí)時(shí)壓縮并通過VGA實(shí)時(shí)顯示,

2009-11-23 17:26:40 5344

5344

基于雙DSP的實(shí)時(shí)圖像處理系統(tǒng)

介紹了基于雙DSP的實(shí)時(shí)圖像處理系統(tǒng)。該系統(tǒng)通過兩片TMS320C6201作為系統(tǒng)計(jì)算中心,通過可重構(gòu)成的FPGA計(jì)算系統(tǒng)獲得系

2009-12-08 14:25:35 1215

1215

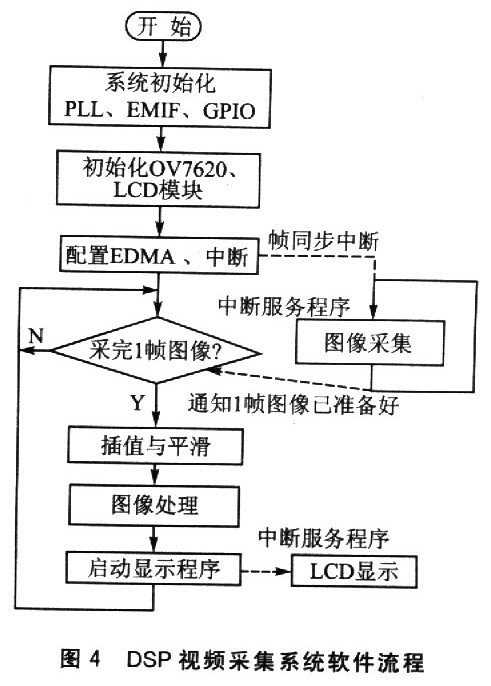

基于DSP的最小圖像采集處理系統(tǒng)設(shè)計(jì)

采用TI公司的TMS320C6713,通過地址譯碼和總線隔離,直接將數(shù)字圖像傳感器芯片OV7620接入;利用EDMA獨(dú)立傳送的特點(diǎn),在不增加DSP軟

2010-01-12 10:44:03 1277

1277

摘要:介紹了基于浮點(diǎn)DSP處理器與雙CMOS頭的數(shù)字圖像采集處理系統(tǒng),探討了系統(tǒng)的基本原理和設(shè)計(jì)方法,并給出了系統(tǒng)的實(shí)現(xiàn)方案。在該系統(tǒng)中,數(shù)據(jù)采集由兩個(gè)相互獨(dú)立的CMOS攝像頭完成,并由DSP進(jìn)行圖像處理,F(xiàn)PGA協(xié)同DSP完成時(shí)序邏輯控制和組合邏輯控制。處理

2011-02-24 23:23:41 491

491 摘要:數(shù)字視頻信號處理涉及對高速實(shí)時(shí)視頻信號的傳輸和處理,要求相關(guān)電路系統(tǒng)具有強(qiáng)大的數(shù)據(jù)處理能力。介紹一種以DSP和FPGA器件為核心構(gòu)建的場發(fā)射平板顯示器視頻信號處理系統(tǒng)方案,并以,11公司的DSP芯片TMS320C6713和Xilinx公司的FPGA芯片XC3S200一PQ208

2011-02-25 16:39:19 53

53 嵌入式處理系統(tǒng) 嵌入式系統(tǒng)概述 嵌入式處理系統(tǒng)設(shè)計(jì) 并行計(jì)算機(jī)的組織結(jié)構(gòu)模型 嵌入式處理系統(tǒng)互連技術(shù) 嵌入式處理系統(tǒng)軟件 多DSP處理器系統(tǒng)

2011-02-25 16:53:57 43

43 摘要:以開發(fā)的實(shí)際系統(tǒng)為背景,論述了基于PCI總線和DSP的實(shí)時(shí)圖像采集與處理系統(tǒng)的硬件及軟件設(shè)計(jì)方案和實(shí)現(xiàn)方法。系統(tǒng)以數(shù)字CCD相機(jī)為圖像采集設(shè)備,利用PCI總線的高速數(shù)據(jù)傳輸能力和DSP強(qiáng)大的數(shù)據(jù)處理能力,實(shí)現(xiàn)了圖像的實(shí)時(shí)采集、處理和傳輸。 關(guān)鍵詞:C

2011-02-25 23:24:41 40

40 本文提出一種方案把數(shù)字信號處理部分從PC機(jī)軟件中分離出來交給DSP處理,DSP處理完畢后再把數(shù)據(jù)交還PC機(jī)進(jìn)行管理。這樣充分利用DSP對數(shù)字信號高速處理的優(yōu)勢,提高信號處理系統(tǒng)的實(shí)

2011-08-04 10:56:57 1835

1835

本文介紹了基于DSP/BIOS的外設(shè)驅(qū)動(dòng)程序模型,并針對基于F2812DSP的視頻處理系統(tǒng)這一具體的硬件平臺,重點(diǎn)介紹了開發(fā)GIO/FVID設(shè)備驅(qū)動(dòng)的流程和針對低端處理器系統(tǒng)的視頻驅(qū)動(dòng)模型裁減方

2011-08-20 15:19:04 2147

2147

本文提出了用DSP5402進(jìn)行語音處理的方法,詳細(xì)介紹了系統(tǒng)的軟硬件結(jié)構(gòu)與原理。該語音處理系統(tǒng)已安裝于某監(jiān)獄監(jiān)控系統(tǒng)中,實(shí)際運(yùn)行效果良好

2011-09-08 15:47:49 115

115 針對水下聲探測系統(tǒng)的要求, 利用AD 公司最新推出的超低功耗器件AD7980 與數(shù)字信號處理器TMS320VC5509A 設(shè)計(jì)了一種水下信號采集存儲處理系統(tǒng)。可同步采集存儲和處理多路水下信號,系統(tǒng)

2011-09-13 17:39:15 87

87 在以DSP為核心的視頻處理系統(tǒng)中,視頻采集的方法通常可以分為兩大類:自動(dòng)的視頻采集和基于DSP的視頻采集。前者通常采用CPLD/FPGA控制視頻解碼芯片,通過FIFO或者雙口RAM向DSP傳送數(shù)據(jù)

2011-09-14 17:05:31 2658

2658

針對圖像處理要求運(yùn)行復(fù)雜靈活的圖像處理算法和大數(shù)據(jù)量的數(shù)據(jù)傳輸處理的要求,提出了一種基于DSP和FPGA架構(gòu)的嵌入式圖像處理系統(tǒng),簡要介紹了系統(tǒng)的工作原理,詳細(xì)介紹了系統(tǒng)硬

2011-12-05 14:12:28 63

63 介紹了一種基于多DSP的并行處理系統(tǒng)設(shè)計(jì)與實(shí)現(xiàn),以及其在分布式雷達(dá)組網(wǎng)航跡融合中的實(shí)際應(yīng)用。重點(diǎn)介紹了該系統(tǒng)由1塊系統(tǒng)主板和4塊TS201處理板卡組成的原理和結(jié)構(gòu),即系統(tǒng)內(nèi)主板

2012-09-25 14:33:48 30

30 基于FPGA的雷達(dá)信號處理系統(tǒng)設(shè)計(jì)的論文

2015-10-30 10:38:12 6

6 基于LabVIEW的虛擬信號處理系統(tǒng),參考下。

2016-01-20 16:28:14 46

46 基于TMS320VC5409_DSP的音頻信號處理系統(tǒng).

2016-01-22 14:03:06 15

15 地面脈沖多普勒雷達(dá)信號處理系統(tǒng)方案,下來看看

2016-12-26 17:19:11 8

8 基于FPGA+DSP實(shí)時(shí)圖像采集處理系統(tǒng)設(shè)計(jì)

2017-01-03 11:41:35 9

9 語音采集、處理系統(tǒng)

2017-02-27 16:18:02 10

10 基于ADSP21060的并行信號處理系統(tǒng)設(shè)計(jì)_邵禎

2017-03-19 11:31:31 1

1 基于LabVIEW的信號采集處理系統(tǒng)_金愛娟

2017-03-18 09:38:39 29

29 基于雙DSP和雙FPGA的高速圖像處理系統(tǒng)設(shè)計(jì)_吳雷

2017-03-16 09:28:51 2

2 基于DSP_FPGA的LFMCW雷達(dá)測距信號處理系統(tǒng)設(shè)計(jì)_陳林軍

2017-03-19 19:07:17 4

4 基于FPGA和DSP的高速圖像處理系統(tǒng)

2017-10-19 13:43:31 20

20 基于DSP的數(shù)字信號采集處理系統(tǒng)設(shè)計(jì)

2017-10-19 15:10:22 25

25 采用DSP處理器的甚高頻全向信標(biāo)_儀表著陸系統(tǒng)標(biāo)準(zhǔn)信號源

2017-10-20 08:56:15 10

10 基于DSP和FPGA的模塊化實(shí)時(shí)圖像處理系統(tǒng)設(shè)計(jì)

2017-10-23 14:09:42 9

9 基于雙DSP的全方位視覺圖像處理系統(tǒng)硬件設(shè)計(jì)與研究

2017-10-23 14:16:16 11

11 多DSP的高速通用并行處理系統(tǒng)研究與設(shè)計(jì)

2017-10-23 15:19:06 6

6 1 引言 1.1 DSP簡介及基本特點(diǎn) 數(shù)字信號的處理離不開算法和實(shí)現(xiàn)手段。數(shù)字信號處理器(digital signal processor簡稱DSP)。是在模擬信號變換成數(shù)字信號以后進(jìn)行高速

2017-10-24 16:57:52 0

0 典型的DSP(數(shù)字信號處理器)內(nèi)部采用改進(jìn)的哈佛結(jié)構(gòu)和流水線技術(shù),可以在單指令周期內(nèi)完成乘加運(yùn)算,具有較高的處理能力。一個(gè)典型的基于DSP的信號采集處理系統(tǒng),通常由DSP、A/D轉(zhuǎn)換器、存儲器和相應(yīng)

2017-11-03 15:37:23 1

1 在圖像數(shù)據(jù)處理系統(tǒng)中,常常需要對高速信號進(jìn)行采集與處理。例如,在光傳感技術(shù)中對光脈沖散射信號的測量,在雷達(dá)工程中對電磁脈沖信號的測量等,都需要對高速信號進(jìn)行采集與運(yùn)算,而且此類高速信號的測量,往往

2017-11-06 14:58:00 16

16 在振動(dòng)信號采集和處理系統(tǒng)設(shè)計(jì)中,信號的處理時(shí)間與可靠性決定著系統(tǒng)應(yīng)用的可行性。本文設(shè)計(jì)了一種基于FPGA的振動(dòng)信號采集處理系統(tǒng),該系統(tǒng)通過振動(dòng)信號采集電路、抗混疊濾波電路、AD采樣電路將電荷信號轉(zhuǎn)化

2017-11-18 05:26:02 4815

4815

為解決高速數(shù)字圖像處理系統(tǒng)和實(shí)時(shí)性相沖突的要求,設(shè)計(jì)了以多DSP(數(shù)字信號處理器TMS320C6416)和現(xiàn)場可編程門陣列(FPGA)相結(jié)合的實(shí)時(shí)圖像處理系統(tǒng)。重點(diǎn)介紹了該系統(tǒng)的硬件資源選擇、基本組

2017-11-18 12:34:02 4704

4704

了滿足儀表著陸系統(tǒng)機(jī)載設(shè)備檢測系統(tǒng)的軟硬件平臺。解決了基于DSP和DAC的多種高精度低頻調(diào)制信號產(chǎn)生、基于鎖相式多波段頻率合成、基于矢量調(diào)制技術(shù)的射頻信號產(chǎn)生、基于數(shù)據(jù)庫技術(shù)的專家系統(tǒng)的構(gòu)建等關(guān)鍵問題。經(jīng)測試,系

2017-11-23 16:28:27 0

0 引言 ARM和DSP作為嵌入式技術(shù)應(yīng)用在地震信號處理系統(tǒng)中,能很好地滿足地震加速度計(jì)對實(shí)時(shí)性、高精度以及網(wǎng)絡(luò)化的要求,因此,利用光線傳感基于ARM 和DSP雙核微處理器的嵌入式系統(tǒng)設(shè)計(jì)方案,一方面

2017-12-01 12:29:02 1014

1014

在對儀表著陸系統(tǒng)(ILS)的數(shù)字化改造中,針對儀表著陸系統(tǒng)采用振幅式測角體制,對發(fā)射信號的幅度失真敏感的問題,提出了一種數(shù)字化儀表著陸系統(tǒng)發(fā)射通道校準(zhǔn)算法。首先,建立了儀表著陸系統(tǒng)發(fā)射端的數(shù)學(xué)模型

2017-12-05 11:52:16 1

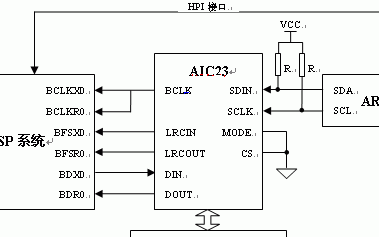

1 DSP強(qiáng)大的數(shù)字信號處理能力和ARM處理器良好的實(shí)時(shí)性能,結(jié)合音頻編解碼芯片TLV320AIC23的接口特點(diǎn),本文闡述了由三者組成的音頻處理系統(tǒng)的硬件接口設(shè)計(jì)和軟件編程,提供了有效和實(shí)用的音頻處理系統(tǒng)方案。

2018-02-11 05:07:00 2718

2718

FPGA+DSP的數(shù)字硬件系統(tǒng)正好結(jié)合了兩者的優(yōu)點(diǎn),兼顧了速度和靈活性。本文以導(dǎo)引頭信號處理系統(tǒng)為例說明FPGA+DSP系統(tǒng)中FPGA的關(guān)鍵技術(shù)。

2019-01-08 08:36:00 3788

3788

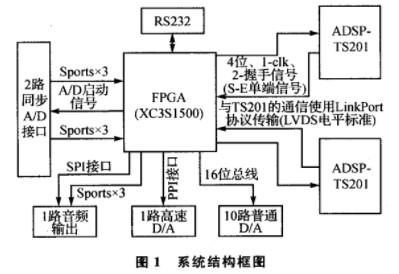

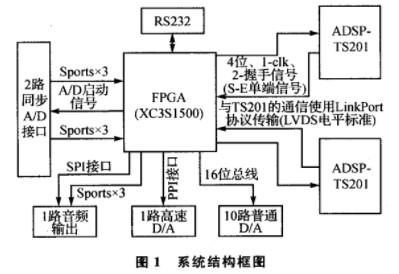

本系統(tǒng)以FPGA作為高性能實(shí)時(shí)信號處理系統(tǒng)的數(shù)據(jù)采集和控制中心,2片DSP為數(shù)據(jù)處理中心,主要包括4個(gè)功能模塊——數(shù)據(jù)采集模塊、FPGA數(shù)據(jù)控制模塊、DSP處理模塊和通信模塊,系統(tǒng)結(jié)構(gòu)框圖如圖1所示。

2019-04-23 08:29:00 4860

4860

現(xiàn)代雷達(dá)特別是機(jī)載雷達(dá)數(shù)字信號處理機(jī)的特點(diǎn)是輸入數(shù)據(jù)多,工作模式復(fù)雜,信息處理量大。因此,在一個(gè)實(shí)時(shí)信號處理系統(tǒng)中,雷達(dá)信號處理系統(tǒng)要同時(shí)進(jìn)行高速數(shù)據(jù)分配、處理和大量的數(shù)據(jù)交換

2018-10-14 08:27:00 3129

3129

強(qiáng)大的數(shù)字信號處理能力和ARM處理器良好的實(shí)時(shí)性能,結(jié)合音頻編解碼芯片TLV320AIC23的接口特點(diǎn),本文闡述了由三者組成的音頻處理系統(tǒng)的硬件接口設(shè)計(jì)和軟件編程,提供了有效和實(shí)用的音頻處理系統(tǒng)方案。

2019-02-26 15:07:37 3554

3554

本文檔的主要內(nèi)容詳細(xì)介紹的是數(shù)字信號處理系統(tǒng)設(shè)計(jì)與實(shí)踐教程之DSP系統(tǒng)設(shè)計(jì)的詳細(xì)資料說明包括了:1. 電源、復(fù)位和時(shí)鐘電路,2.系統(tǒng)自舉,3.系統(tǒng)設(shè)計(jì),4.小結(jié)

2019-03-20 17:15:19 16

16 討論了 以數(shù)字信號處理器(DSP)和復(fù)雜可編程邏輯器件(CPLD)為核心的語音處理系統(tǒng)的設(shè)計(jì),介紹了該系統(tǒng)的框圖和詳細(xì)的硬件設(shè)計(jì)方案.調(diào)試結(jié)果表明該系統(tǒng)工作穩(wěn)定,性能良好,可用于語音信號編解碼和處理算法的設(shè)計(jì)與開發(fā)

2019-05-28 16:25:18 6

6 目前的信號處理系統(tǒng)一般需要混合信號器件, 例如模數(shù)轉(zhuǎn)換器(ADC)、數(shù)模轉(zhuǎn)換器(DAC)和快速數(shù)字信號處理器(DSP)。由于需要處理寬動(dòng)態(tài)范圍的模擬信號, 因此擁有高性能ADC和DAC顯得更加

2021-05-29 11:19:14 5

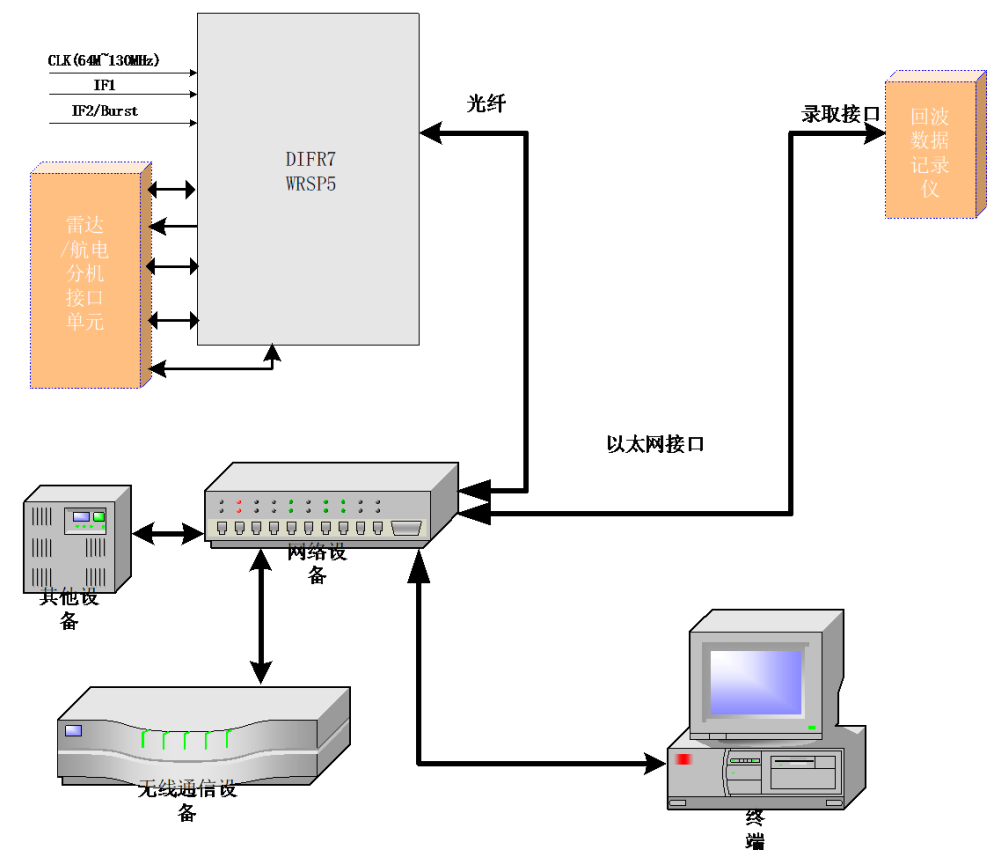

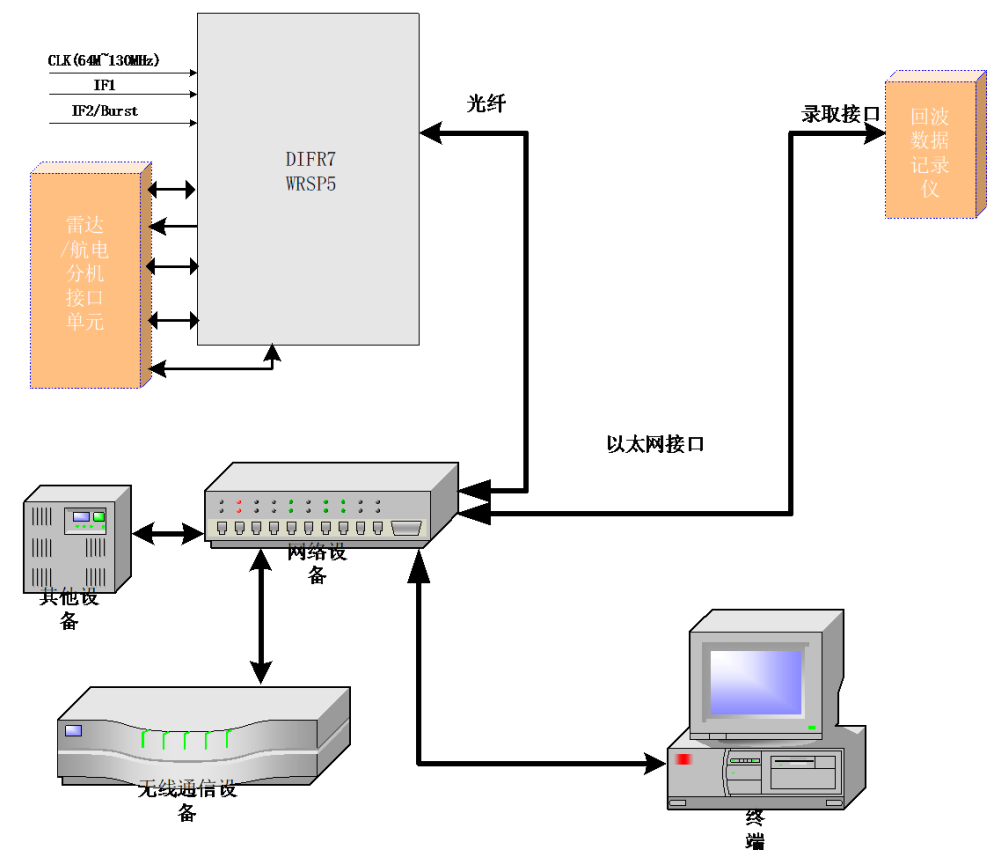

5 毫米波雷達(dá)信號處理系統(tǒng)(WRSP)是杭州淞柏科技公司研制的全功能高端雷達(dá)信號處理器,該處理器采用了脫機(jī)運(yùn)行、網(wǎng)絡(luò)接口,采用 DIFR硬件平臺,為機(jī)載、艦載船載、車載等各種平臺雷達(dá)。在設(shè)計(jì)上采用高集成方案,高速DSP+FPGA 完成雷達(dá)信號處理模式,可支持各種不同方式的脈沖壓縮和補(bǔ)盲。

2021-11-24 15:26:28 1826

1826

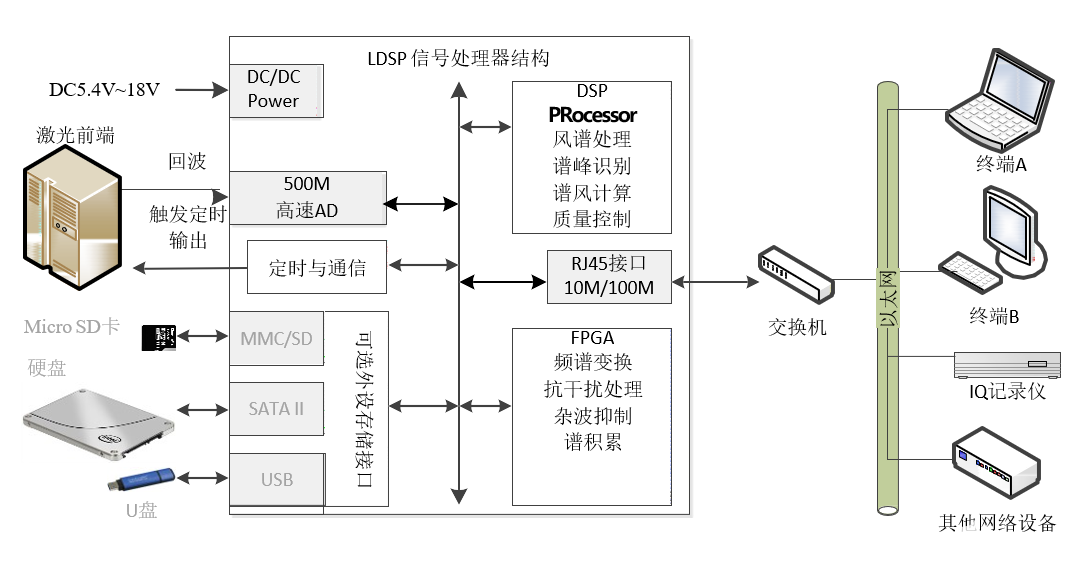

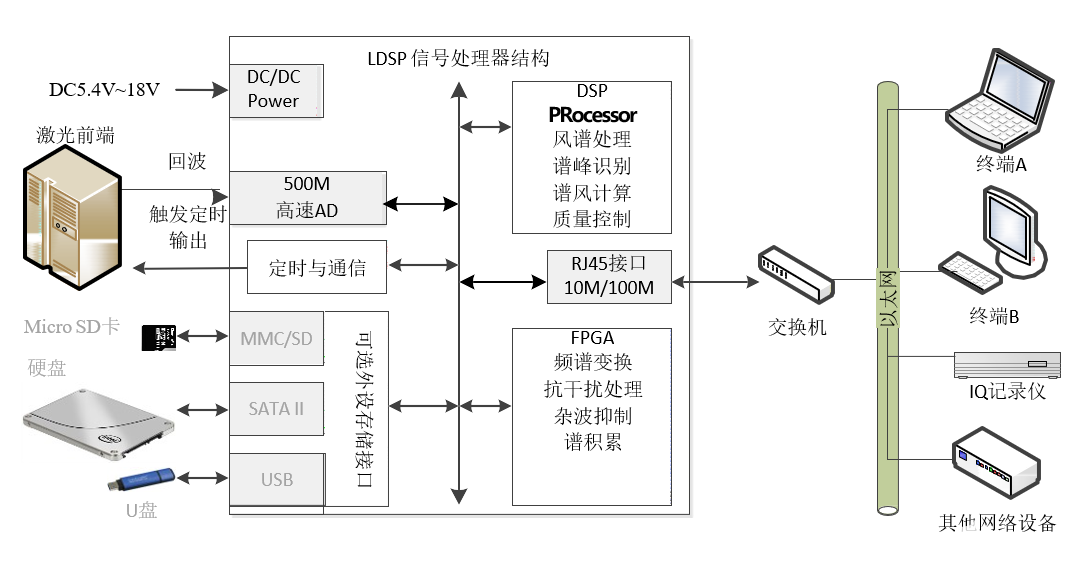

激光雷達(dá)信號處理系統(tǒng)(LDSP )是專為激光雷達(dá)研發(fā)的高性能、高集成、低功耗數(shù)字信號處理器。該信號處理器采用高速高精度 ADC、大規(guī)模 FPGA及高速 DSP等處理芯片,處理功能強(qiáng)大、速度高、功耗低

2021-11-24 15:24:20 3169

3169

基于FPGA+DSP彈載SAR信號處理系統(tǒng)設(shè)計(jì)

2021-12-27 18:58:51 21

21 基于MATLAB的信號處理系統(tǒng)與分析,包括信號的導(dǎo)入、預(yù)處理、分析、特征提取以及頻譜分析等關(guān)鍵步驟,并通過實(shí)例展示MATLAB在信號處理與分析中的強(qiáng)大功能。

2024-05-17 14:24:03 2367

2367 信號采集與處理系統(tǒng)是一種廣泛應(yīng)用于工業(yè)、科研、醫(yī)療等領(lǐng)域的電子系統(tǒng),它能夠?qū)Ω鞣N類型的信號進(jìn)行采集、處理和分析。一個(gè)完整的信號采集與處理系統(tǒng)通常由以下幾個(gè)模塊組成: 信號源模塊 信號源模塊是信號采集

2024-07-15 14:12:38 3651

3651

電子發(fā)燒友App

電子發(fā)燒友App

評論