高頻脈沖噪聲對數字信號處理系統危害性最大。為了提高系統的抗干擾性能,在數字信號處理系統中可

2010-12-17 11:00:34 4996

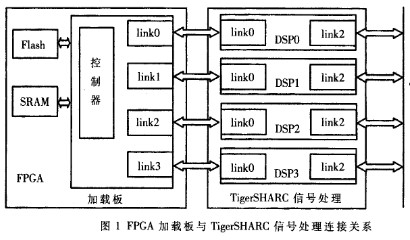

4996 由于本系統是由多片ADSP-TS101組成的系統,所以由40 MHz晶振產生的時鐘信號不能直接接到各DSP和FPGA,而應該通過驅動后再接到各DSP,且時鐘信號到各DSP的距離應該盡可能接近。本系統

2020-11-02 10:36:31 3461

3461

用于多處理TigerSHARC系統的集群總線通信的詳細信號完整性和時序分析。該系統由8個ADSP-TS101S器件,一個主處理器和SDRAM組成,其集群總線運行頻率為100MHz。包括仿真結果和物理

2019-08-30 09:24:28

大規模集成電路技術的發展,作為數字信號處理的核心數字信號處理器(DSP)得到了快速的發展和應用。ADSP-TS201DSP是美國模擬器件(ADD公司繼TSl01之后推出的一款高性能處理器。此系列DSP性價比很高

2019-04-12 07:00:11

電平敏感中斷;低功耗空閑指令;PGA、PLCC、PQFP和TQFP包;提供MIL-STD-883B版本。 一般說明 ADSP-2100系列處理器是為數字信號處理(DSP)和其他高速數字處理應用而優化

2020-07-17 14:23:24

ADSP系列數字信號處理器原理介紹,一共7個部分

2016-05-28 09:22:40

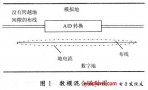

具有各種功能的信號處理系統,可以使系統做到更加經濟和小型化,進而有可能實現過去用模擬技術難以實現的各種功能。

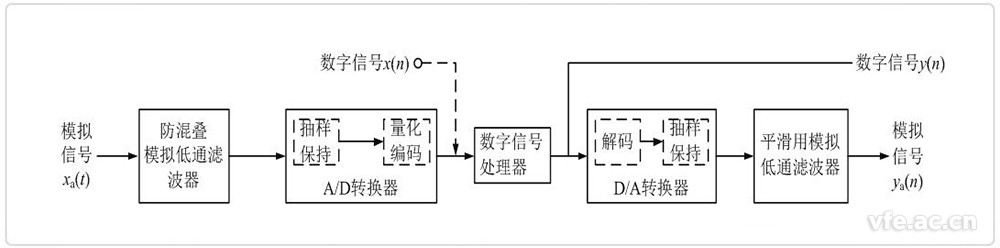

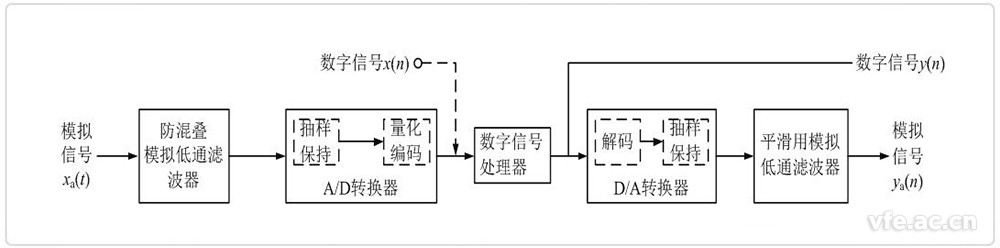

圖1-1給出了模擬信號數宇化處理系統的簡化框圖。此系統先將模擬信號變換為數字信號,經

2023-09-28 06:34:08

強 模擬信號處理系統調試和修改不便,而數字處理系統的系統參數一般保 存在寄存器或存儲器中,修改這些參數對系統進行調試非常簡單,軟件實現時尤其如此。由于數字器件以及軟件的特點,數字信號處理系統的復制也

2020-12-09 14:01:39

【PDF】數字信號處理系統及其應用附件列表:

2011-02-24 10:28:14

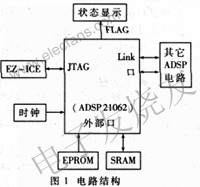

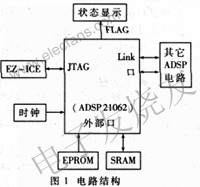

ADSP2106x SHARC是一個適用于語音、通信和圖像處理的高速32位數字信號處理器。該芯片是基于ADSP21000系列DSP芯片發展起來的一個完整的單片系統,增加了一個雙口片內SRAM,并集成

2019-07-19 08:16:35

應用。TigerSHARC DSP有兩個獨立的32位處理器核,或者多指令多數據流(MIMD)結構。每個處理單元都能在單周期執行一次乘法,以及加法,對于300 MHz的ADSP TS101S,每個周期能產生6個

2019-07-22 06:29:35

DSP技術廣泛應用于各個領域,但傳統的數字信號處理器由于以順序方式工作使得數據處理速度較低,且在功能重構及應用目標的修改方面缺乏靈活性。而使用具有并行處理特性的FPGA實現數字信號處理系統,具有很強的實時性和靈活性,因此利用FPGA實現數字信號處理成為數字信號處理領域的一種新的趨勢。

2019-10-17 08:12:27

本帖最后由 午夜的沉默 于 2015-3-14 22:14 編輯

哪位有ADSP TS101S 芯片的Cadence原理圖封裝啊跪求 ..

2015-03-14 22:13:20

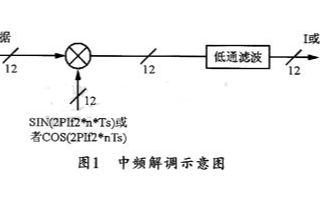

在信號處理系統中一般采用數據采集卡實現數據采集,采用微機軟件處理的方法實現數據處理,采用PC機實現數據管理。由于PC機的CPU采用的是馮?諾依曼存儲器結構,并不適用于數字信號的運算,若完全使用PC機

2018-12-17 11:29:06

和可編程邏輯器件XC2S300E為核心的圖象處理系統的硬件實現方案以及通過DSP對FPGA芯片的動態配置來實現軟件控制的設計思路。 關鍵詞:可編程邏輯器件;數宇信號處理器;數字圖象處理;動態配置dsp 可編程邏輯器件 數宇信號處理器 數字圖象處理 動態配置

2012-12-19 11:05:08

摘要:介紹了可編程邏輯器件在數字信號處理系統中的應用。并運用VHDL語言對采用Lattice公司的ispLSI1032E可編程邏輯器件所構成的乘法器的結構、原理及各位加法器的VHDL作了詳細的描述

2019-06-28 06:14:11

。2 DSP芯片選型根據系統的性能要求,通過比較各種高性能DSP處理器,并著重對構成并行處理系統的性能和便捷性進行分析,確定選用AD公司的ADSP Tiger SHARC系列處理器中的TS201S組成多

2019-05-21 05:00:19

在雷達信號處理、數字圖像處理等領域中,信號處理的實時性至關重要。由于FPGA芯片在大數據量的底層算法處理上的優勢及DSP芯片在復雜算法處理上的優勢,DSP+FPGA的實時信號處理系統的應用越來越廣泛。那么,我們該怎么利用FPGA與ADSP TS201設計總線接口呢?

2019-08-09 06:56:11

求一個解決系統中主處理器在較高工作頻率300 MHz下穩定工作的問題,以及在兩個主芯片之間和主芯片與數據存儲芯片之間數據高速互聯的問題,提高系統的性能,滿足設計要求的基于ADSP-TS101高速信號處理系統。

2021-04-12 06:39:56

數字電路的常見干擾噪聲有哪幾種?抑制干擾噪聲的措施有哪些?數字信號處理系統的抗干擾設計

2021-05-12 07:01:58

硬件系統的設計思路是什么基于ADSP21160的數字信號處理系統設計

2021-04-22 06:47:12

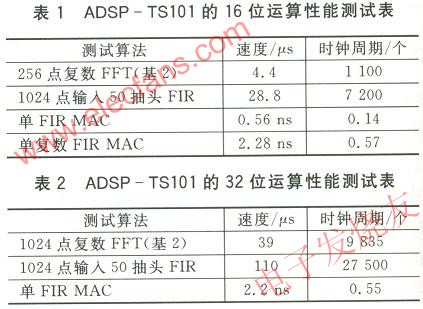

ADSP-TS101S是美國ADI公司推出的一款具有極高性能的數字信號處理器(DSP)芯片,其專為大信號處理任務和通信應用進行了結構上的優化設計,在嵌人式信號處理中得到廣泛應用

2019-08-23 07:59:39

為什么要設計激光多譜勒信號處理系統?激光多譜勒信號處理系統有哪些優點?怎樣去設計激光多譜勒信號處理系統?如何去驗證激光多譜勒信號處理系統?

2021-04-15 06:25:40

介紹了一種基于CPCI總線并采用TS201,stratix和GA3816作為系統信號的高速信號處理平臺。同時簡單介紹了GA3816芯片的一些特點,詳細說明了該信號處理系統的結構和功能,給出了系統

2009-03-07 10:01:32 4

4 使用PSD311和高速ADSP-2105 數字信號處理器芯片進行設計

2009-05-13 14:13:30 26

26 對AD 公司的TigerSHARC DSP(ADSP-TS101S) 和摩托羅拉公司的具有AltiVec 矢量處理器核的PowerPC 系列MPC7410 和MPC7455 處理器,在連續實時信號處理領域的應用進行了評估。

2009-05-18 13:25:50 12

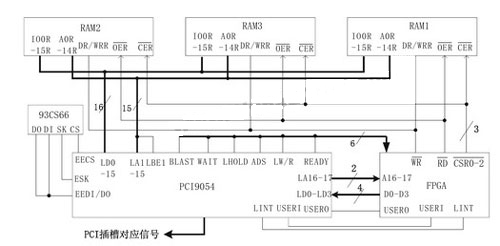

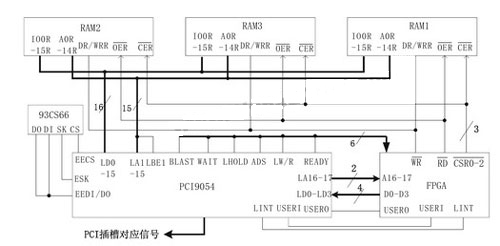

12 ADSP-TS101 是ADI 公司新一代高性能浮點DSP,開始應用在高速數據采集和處理系統中。TS101 外部總線接口可編程,方便和各種總線外設接口。本文結合TS101 與同步FIFO、SDRAM 和FPGA 的接

2009-08-11 09:49:31 28

28 以雷達信號處理領域中的應用為例,介紹了基于ADSP2106X的高速并行數字信號處理系統的設計方法。ADSP2106X本身的特點使其非常適合于高速實時處理的場合,與可編程邏輯器件的組成

2009-11-30 13:22:52 19

19 總體描述ADSP-TS101S TigerSHARC處理器是一款超高性能、靜態超標量處理器,針對大型信號處理任務和通信基礎設施進行了優化。DSP將非常寬的存儲器寬度與雙計算模塊相結合,支持32/40

2023-03-07 18:24:07

:本文介紹了基于SharcFIN 芯片的數字接收機ICS554 在軟件高頻雷達上與通用信號處理平臺之間的接口實現,給出了ADSP-TS101S 通過該接口實現雷達信號處理系統與ICS554 之間實時通

2009-12-16 12:38:57 16

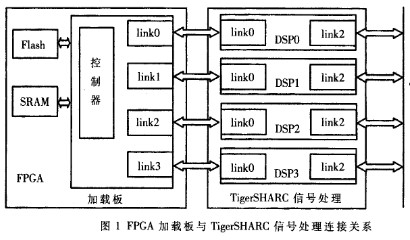

16 為了滿足干涉超光譜復原處理系統對數據及實時性要求,本文提出了一種基于多ADSP-TS101 的FPGA+DSP[1]的并行圖像處理系統的解決方案,并給出了具體硬件實現。目前,該系統能夠滿

2010-01-06 15:31:32 8

8 ADSP-TS101S TigerSHARC?處理器是一款高性能、靜態Superscalar?處理器,針對大型信號處理任務和通信基礎設施進行了優化。DSP集成了非常寬的存儲器寬度和雙通道計算模塊

2023-07-14 16:20:50

為了滿足干涉超光譜復原處理系統對數據及實時性要求,本文提出了一種基于多ADSP-TS101的FPGA+DSP[1]的并行圖像處理系統的解決方案,并給出了具體硬件實現。目前,該系統能夠滿足超光

2010-07-17 17:31:35 7

7 微弱地低速運動目標信號,是一個頻率極低,準周期,低信噪比,多諧波組合的信號,如何更加有效準確地檢測目標信號是信號處理領域的難點和熱點。本文提出了基于ADI公司高性能的ADSP-T

2010-08-05 11:37:30 22

22 ADSP-21060LCW-160:高性能數字信號處理器在數字信號處理領域,處理器的性能和效率對系統的整體表現至關重要。ADSP-21060LCW-160是亞德諾半導體(Analog Devices

2024-03-03 12:51:11

采用ADSP-TS201S芯片的圖像采集處理系統

隨著人們對實時信號處理要求的不斷提高和大規模集成電路的迅速發展,作為數字信號處理核心和標志的數字

2009-03-30 12:19:18 1450

1450

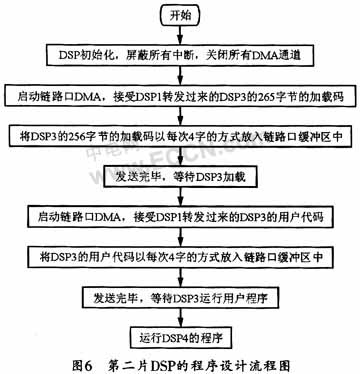

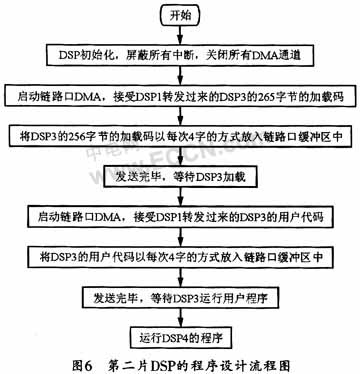

多片TS101S的加載引導設計分析及實現

0 引言ADSP-TS101S數字信號處理器是美國ADI公司推出的TigerSHARC系列中的一款具有極高性能的靜態超標量處理器。該處理器已

2010-03-31 10:20:26 1791

1791

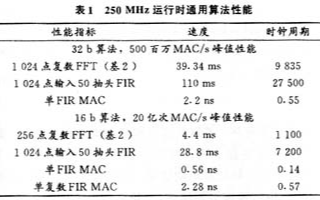

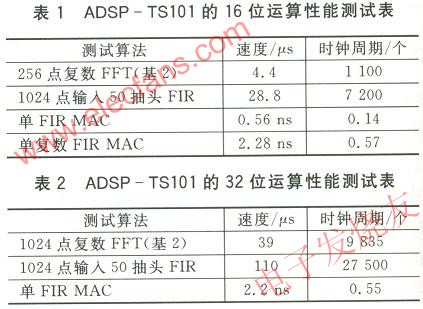

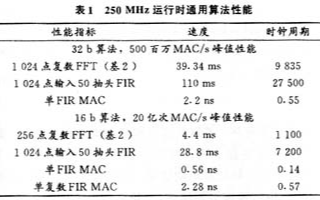

Adsp-TS101性能比ADSP21160有顯著提高,且與之兼容,使得以ADSP21160開發的產品升級快速、簡捷。Adsp-TS101是64位處理器,工作在250 MHz時鐘下,可進行32位定點和32位或40位浮點運算,

2010-09-23 09:57:25 2059

2059

ADSP2106x SHARC是一個適用于語音、通信和圖像處理的高速32位數字信號處理器。該芯片是基于ADSP21000系列DSP芯片發展起來的一個完整的單片系統,增加了一個雙口片內SRAM.

2010-09-26 10:48:22 1596

1596

基于開放式的標準,以及最新的DVB和IP數字技術和相關應用,SUNNISKY TS2000-S2 DVB-S2衛星數字信號處理器,能夠有效的接收DVB-S DVB-S2衛星標清SD和高清HD數字電視信號,經過一系列數字信號的

2011-04-11 12:11:39 72

72 本文提出一種方案把數字信號處理部分從PC機軟件中分離出來交給DSP處理,DSP處理完畢后再把數據交還PC機進行管理。這樣充分利用DSP對數字信號高速處理的優勢,提高信號處理系統的實

2011-08-04 10:56:57 1835

1835

設計并實現了一種基于ADSP TS201的組網雷達數據融合實時處理系統。主要闡述了雙ADSP TS201并行處理系統的結構、算法量的估計與結果分析。系統可滿足集中式組網融合和分布式組網融合

2011-10-09 10:49:40 30

30 為了滿足水聲通信以及水下信號處理和目標識別等方面對高速實時并行處理系統的要求,文章設計并研制了一種基于ADSP21160和多通道同步采樣ADC芯片的多處理器并行數字信號處理系統,

2011-10-10 15:10:27 55

55 介紹了一種基于DSP芯片ADSP-TS101S的圖像采集和處理系統,應用于復雜條件下目標的檢測,并著重于硬件系統的分析

2011-10-11 15:08:06 75

75 本文使用ADI 公司的ADSP21160為主處理器搭建了信號處理硬件平臺,給出了對系統的構思及具體電路設計。

2012-02-09 10:46:44 2619

2619

在DSP系統上運行的程序,系統上電復位后需要加載程序到DSP的程序存儲器內。這是使用外部加載模式時的系統開發不可缺少的環節。針對實際需求,提出了一種使用USB對ADSP_TS101S進行鏈

2012-06-08 08:51:08 0

0 本文基于ADSP-TS101高速信號處理系統采用了集成系統設計,硬件部分引入信號完整性分析的設計方法進行高速數字電路的設計,解決系統中主處理器在較高工作頻率300 MHz下穩定工作的問題

2012-09-06 17:15:51 7970

7970

內容簡介 本書以數字信號處理基礎內容為主,同時也介紹了有關數字信號處理實現與應用。書中 以主要篇幅討論了離散時間信號與系統的基本概念,離散傅里葉變換及其快速算法,數字濾 波器的結構與各種設計方法

2015-11-17 15:22:48 25

25 基于ADSP_TS201S的多DSP并行系統設計

2015-12-29 17:33:04 22

22 基于ADSP21060的并行信號處理系統設計_邵禎

2017-03-19 11:31:31 1

1 基于DSP的數字信號采集處理系統設計

2017-10-19 15:10:22 25

25 ADSP-TS101S是美國ADI公司推出的一款具有極高性能的數字信號處理器(DSP)芯片,其專為大信號處理任務和通信應用進行了結構上的優化設計,在嵌人式信號處理中得到廣泛應用

2017-10-21 10:26:04 0

0 ADSP-TS101S是美國ADI公司推出的一款具有極高性能的數字信號處理器(DSP)芯片,其專為大信號處理任務和通信應用進行了結構上的優化設計,在嵌人式信號處理中得到廣泛應用

2017-10-21 10:46:43 1

1 ADSP2106x SHARC是一個適用于語音、通信和圖像處理的高速32位數字信號處理器。該芯片是基于ADSP21000系列DSP芯片發展起來的一個完整的單片系統,增加了一個雙口片內SRAM,并集成

2017-10-24 15:45:33 7

7 ADSP2106x SHARC是一個適用于語音、通信和圖像處理的高速32位數字信號處理器。該芯片是基于ADSP21000系列DSP芯片發展起來的一個完整的單片系統,增加了一個雙口片內SRAM,并集成

2017-10-25 10:04:46 0

0 ,選用ISSI公司的IS42S16400高速SDRAM芯片,詳細論述在基于TMS320C6201(簡稱C6201)的數字信號處理系統中此設計方法的具體實現。 1 IS42S16400芯片簡介

2017-10-25 11:23:43 1

1 共享與鏈路口混合耦合的多DSP并行處理系統方案。在設計中,利用FPGA實現數據傳輸和CPCI接口的邏輯控制。經驗證,該系統具有運算能力強、片間通信靈活、并行處理效率高等優點。 關鍵詞:多DSP并行系統;ADSP-TS201S;FPGA;CPCI接口 0 引言 在寬帶雷達信號處理中,存在諸如回波

2017-10-31 16:41:04 0

0 ADI公司的高性能數字信號處理器Tiger-SHARC系歹0包括ADSP-TS101S、ADSP-TS201S、ADSP-TS202S和ADSP-TS203S等芯片。它們被廣泛應用于視頻和通信市場

2017-11-03 15:12:51 1

1 DSP強大的數字信號處理能力和ARM處理器良好的實時性能,結合音頻編解碼芯片TLV320AIC23的接口特點,本文闡述了由三者組成的音頻處理系統的硬件接口設計和軟件編程,提供了有效和實用的音頻處理系統方案。

2018-02-11 05:07:00 2718

2718

TigerSHARC系列處理器是ADI公司推出的高性能數字信號處理器,包含ADSP TS101、ADSP TS201、ADSP TS202、ADSP TS203。TigerSHARC系列處理

2019-04-19 08:05:00 2768

2768

現代雷達特別是機載雷達數字信號處理機的特點是輸入數據多,工作模式復雜,信息處理量大。因此,在一個實時信號處理系統中,雷達信號處理系統要同時進行高速數據分配、處理和大量的數據交換

2018-10-14 08:27:00 3129

3129

電子發燒友網為你提供ADI(ti)ADSP-TS101S相關產品參數、數據手冊,更有ADSP-TS101S的引腳圖、接線圖、封裝手冊、中文資料、英文資料,ADSP-TS101S真值表,ADSP-TS101S管腳等資料,希望可以幫助到廣大的電子工程師們。

2019-02-22 15:01:34

本文檔的主要內容詳細介紹的是數字信號處理系統設計與實踐教程之DSP系統設計的詳細資料說明包括了:1. 電源、復位和時鐘電路,2.系統自舉,3.系統設計,4.小結

2019-03-20 17:15:19 16

16 數字信號處理就是用一些數學算法對數字信號進行分析、變換、綜合、估值和識別。作為數字信號處理核心和標志的數字信號處理器(DSP)芯片自問世以來得到了快速的發展,廣泛應用于通信系統、圖形/圖像處理、雷達

2021-03-26 09:21:12 3369

3369

ADSP-TS101S IBIS數據文件BGA包

2021-04-12 16:11:10 4

4 ADSP-TS101S EZ-KIT有限公司設計數據表(1.3版)

2021-04-13 15:14:10 0

0 EE-208型:考慮ADSP-21262 SHARC?數字信號處理器

2021-04-15 21:36:36 11

11 EE-176:ADSP-TS101S老虎SHARC高級Processor硬件設計檢查表

2021-04-16 08:51:20 0

0 EE-205:將代碼從ADSP-TS101S TigerSHARC?處理器移植到ADSP-TS201S TigerSHARC處理器的注意事項

2021-04-16 13:54:51 9

9 EE-217:更新ADSP-TS101S老虎SHARC-ZEZ-KIT有限公司

2021-04-16 18:18:12 5

5 EE-143:了解ADSP-TS101上的DMA

2021-04-24 11:29:52 7

7 EE-174:ADSP-TS101S虎-SHARC高級ProcessLuter加載內核手術

2021-04-25 10:17:06 9

9 ADSP-21160M/ADSP-21160N:SHARC數字信號處理器數據表

2021-04-30 19:33:43 1

1 ADSP-21990:混合信號數字信號處理器數據表

2021-05-07 15:22:06 10

10 EE-169:ADSP-TS101S的功耗估算

2021-05-10 09:55:06 8

8 ADSP-21991:混合信號數字信號處理器數據表

2021-05-13 13:00:10 6

6 ADSP-TS101 TigerSHARC處理器編程參考

2021-05-13 17:11:14 9

9 ADSP-TS101S TigerSHARC版本0.2、0.4異常列表

2021-05-14 15:46:33 0

0 用于ADSP-TS101S TigerSHARC處理器的EZ套件精簡版產品亮點

2021-05-17 17:33:44 0

0 ADSP-218x 16位數字信號處理器

2021-05-17 17:43:40 7

7 ADSP-TS101S EZ套件精簡版?SUP_

2021-05-17 20:10:12 0

0 ADSP-TS101S EZ-KIT Lite評估系統手冊(1.1版,2004年3月)

2021-05-18 17:38:05 0

0 ADSP-TS101 TigerSHARC處理器硬件參考

2021-05-22 10:59:30 4

4 EE-178:ADSP-TS101S TigerSHARC?片上SDRAM控制器

2021-05-27 18:03:52 14

14 ADSP-TS101S IBIS數據文件BGA包

2021-06-16 08:36:40 11

11 電子發燒友網站提供《ADSP-21160M/ADSP-21160N:SHARC數字信號處理器數據手冊.pdf》資料免費下載

2025-01-03 15:39:44 0

0 電子發燒友網站提供《EE-217:更新ADSP-TS101S TigerSHARC EZ-KIT Lite固件.pdf》資料免費下載

2025-01-14 16:39:56 0

0 電子發燒友網站提供《EE-176:ADSP-TS101S TigerSHARC處理器硬件設計核對表.pdf》資料免費下載

2025-01-14 16:27:23 0

0 電子發燒友網站提供《EE-205:將代碼從ADSP-TS101S TigerSHARC處理器移植到ADSP-TS201S TigerSHARC處理器的注意事項.pdf》資料免費下載

2025-01-14 15:15:24 0

0 電子發燒友網站提供《EE-169:估算ADSP-TS101S的功耗.pdf》資料免費下載

2025-01-14 15:11:34 0

0 電子發燒友網站提供《EE-178:ADSP-TS101S TigerSHARC片上SDRAM控制器.pdf》資料免費下載

2025-01-14 15:00:14 0

0 電子發燒友網站提供《EE-174:ADSP-TS101S TigerSHARC處理器引導加載程序內核操作.pdf》資料免費下載

2025-01-15 15:35:09 0

0 的以數字信號處理器為核心部件的數字信號處理系統框圖,此系統既可處理數字信號,也可處理模擬信號。 圖1數字信號處理系統框圖 一 數字信號處理的基本組成? 當用此系統處理數字信號時,如圖1所示,可直接將輸入數字信號x(n)送入數字信

2025-06-18 09:02:21 983

983

電子發燒友App

電子發燒友App

評論