基于FPGA的數(shù)據(jù)采集控制模塊設(shè)計

0 引 言

數(shù)據(jù)采集和控制系統(tǒng)是對生產(chǎn)過程或科學(xué)實驗中各種物理量進(jìn)行實時采集、測試和反饋控制的

2010-02-08 10:00:28 1809

1809

使用XINTF總線進(jìn)行通訊進(jìn)行數(shù)據(jù)傳輸,DSP,FPGAIO全部引出 這樣就可以很容易的將主控板融入到嵌入式系統(tǒng)中,需要什么外設(shè)可以直接裝在主控板上,可以用來控制電機(jī),可以用來做數(shù)據(jù)采集系統(tǒng)。將外部

2016-07-18 16:59:22

DSP28335+FPGA+AD7606的數(shù)據(jù)采集系統(tǒng),DSP采用TI公司的TMS320F28335,FPGA使用 ALTERA的Cyclone3 的 EP3C5E144C8N在設(shè)計的過程中遇到

2016-07-18 16:53:28

DSP28335+FPGA+AD7606的數(shù)據(jù)采集系統(tǒng),DSP采用TI公司的TMS320F28335,FPGA使用 ALTERA的Cyclone3 的 EP3C5E144C8N在設(shè)計的過程中遇到

2016-07-18 17:13:01

DSP的FPGA的高速數(shù)據(jù)采集系統(tǒng)的研究與設(shè)計,大家可以看看

2015-04-03 21:23:48

基于DSP5509 的數(shù)據(jù)采集系統(tǒng)系統(tǒng)采用了DSP + FPGA 的雙核結(jié)構(gòu),由CMOS 感光芯片OV7620 采集圖像,得到數(shù)據(jù)源, FPGA 作為輔助處理器,控制部分外圍器件并協(xié)助采集數(shù)據(jù)

2009-04-28 10:47:02

申請理由:我是一名在讀研究生,目前在做數(shù)據(jù)采集系統(tǒng),采用的是STM32,做成之后感覺系統(tǒng)不是很穩(wěn)定,精度也不高,后來查了資料,原來DSP更適合做信號處理分析這一類別,所以申請一下。項目描述

2015-09-10 11:18:52

申請理由:使用TI的片子感覺不錯,CCS的例程很豐富,自己有一塊C2000的板子,但是是最小系統(tǒng),想做一個數(shù)據(jù)采集系統(tǒng),需要一塊好的開發(fā)板做研發(fā)。項目描述:設(shè)計基于DSP的高速數(shù)據(jù)采集系統(tǒng)嗎,打算采用C6000的FIFO解決DSP芯片與A/D工作速率不匹配的問題,有效避免數(shù)據(jù)丟失

2015-10-29 14:13:45

TMS320C6748的使用,了解其新特性。2、學(xué)習(xí)利用dsp實現(xiàn)一些高級濾波算法。3、將dsp與fpga結(jié)合實現(xiàn)高速數(shù)據(jù)采集。4、分享5篇左右的開發(fā)板使用心得。

2015-10-09 15:10:00

對數(shù)據(jù)采集與處理系統(tǒng)提出了新的更高的要求,即高速度、高精度和高實時性。對數(shù)據(jù)采集與處理系統(tǒng)的設(shè)計,有以下3種方案可供選擇:(1)A/D+DSP方案在傳統(tǒng)的高速信號處理中,大多采用這種方案。將A/D、D

2019-07-05 06:41:27

基于DSP和現(xiàn)場總線的數(shù)據(jù)采集系統(tǒng)設(shè)計在電力系統(tǒng)的生產(chǎn)過程中,生產(chǎn)運(yùn)行部門通常有兩方面的考慮:一方面盡量提高設(shè)備與線路的利用率,實現(xiàn)系統(tǒng)的經(jīng)濟(jì)性;同時保證電力系統(tǒng)的安全、可靠運(yùn)行,提供高質(zhì)量的電能

2009-12-08 10:28:19

基于FPGA+DSP的高速數(shù)據(jù)采集系統(tǒng)設(shè)計

2012-06-27 17:23:53

基于FPGA 的DSP 數(shù)據(jù)采集分析系統(tǒng)設(shè)計

2012-08-20 15:35:41

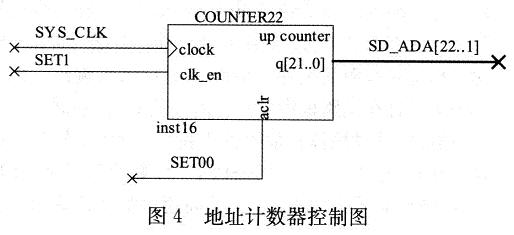

。為了實現(xiàn)高速、連續(xù)采樣的數(shù)據(jù)采集系統(tǒng),本文介紹了一種基于 FPGA +AD7609的數(shù)據(jù)采集系統(tǒng)的構(gòu)成及技術(shù)實現(xiàn)。采用 FPGA 作為主模塊,AD7609為數(shù)據(jù)采集模塊,并設(shè)計了硬件實現(xiàn)電路。實驗測試

2018-08-09 14:28:00

24期摘 要:傳統(tǒng)的數(shù)據(jù)采集系統(tǒng)大都是由ARM+DSP實現(xiàn)的,雖然DSP的優(yōu)勢在于數(shù)據(jù)處理,但是隨著FPGA技術(shù)的發(fā)展,很多FPGA已經(jīng)可以取代DSP的作用了。尤其是在高速實時的數(shù)據(jù)采集領(lǐng)域,采集

2018-05-09 12:09:43

基于FPGA的數(shù)據(jù)采集系統(tǒng)IEE ... 介紹了數(shù)據(jù)采集系統(tǒng)中以FPGA為處理核心、采用TI公司接口芯片的IEEE1394接口設(shè)計,給出了系統(tǒng)硬件設(shè)計和FPGA邏輯設(shè)計,討論了IEEE1394總線

2012-08-11 15:43:47

設(shè)計高溫環(huán)境下(最高120°)基于FPGA的數(shù)據(jù)采集存儲系統(tǒng),就是通過傳感器采集數(shù)據(jù),通過FPGA來控制,把數(shù)據(jù)存儲到存儲芯片上,回頭可以通過接口讀取數(shù)據(jù)顯示在計算機(jī)上,求大師給我指導(dǎo),我急需整個系統(tǒng)的protel原理圖,請各位幫忙,我將感激不盡。最好有附件畫出整個原理圖,謝謝!

2012-10-29 21:37:12

目前,在數(shù)據(jù)采集系統(tǒng)的硬件設(shè)計方案中,有采用通用單片機(jī)和USB相結(jié)合的方案,也有采用DSP和USB相結(jié)合的方案,前者雖然硬件成本低,但是時鐘頻率較低,難以滿足數(shù)據(jù)采集系統(tǒng)對速度要求;后者雖然可以實現(xiàn)

2019-09-05 07:22:57

基于FPGA的高速實時數(shù)據(jù)采集系統(tǒng)設(shè)計

2012-08-20 20:00:14

不能時刻停留的地方偶爾采集一些現(xiàn)場數(shù)據(jù),因而不但需 要花費(fèi)大量的人力、物力和財力進(jìn)行設(shè)備的維護(hù),同時給采集帶來很多不必要的麻煩。為了解決上述問題,本文提出了一種基于ARM 的藍(lán)牙實時數(shù)據(jù)采集系統(tǒng)。采用

2021-10-26 06:30:00

哪位大神可以指導(dǎo)一下基于ARM的藍(lán)牙數(shù)據(jù)采集系統(tǒng)的設(shè)計與實現(xiàn)的電路圖與代碼。可以私聊

2016-04-02 23:08:21

基于ARM的藍(lán)牙實時數(shù)據(jù)采集系統(tǒng)

2015-03-26 17:41:52

本帖最后由 eehome 于 2013-1-5 10:11 編輯

基于labview與dsp串口的數(shù)據(jù)采集系統(tǒng)

2012-05-10 15:28:18

高速連續(xù)數(shù)據(jù)采集系統(tǒng)的背景及功能是什么?如何利用FPGA實現(xiàn)高速連續(xù)數(shù)據(jù)采集系統(tǒng)設(shè)計?FPGA在高速連續(xù)數(shù)據(jù)采集系統(tǒng)中的應(yīng)用有哪些?

2021-04-08 06:19:37

數(shù)據(jù)采集和控制系統(tǒng)是對生產(chǎn)過程或科學(xué)實驗中各種物理量進(jìn)行實時采集、測試和反饋控制的閉環(huán)控制,它在工業(yè)控制、軍事電子設(shè)備、醫(yī)學(xué)監(jiān)護(hù)等許多領(lǐng)域發(fā)揮著重要作用。其中,數(shù)據(jù)采集部分尤為重要,而傳統(tǒng)的數(shù)據(jù)采集

2019-11-05 07:25:07

我正在學(xué)習(xí)基于FPGA的數(shù)據(jù)采集系統(tǒng)的設(shè)計,請各位大神提供些有關(guān)這方面的資料,最好是Verilog HDL代碼!謝謝!

2015-07-16 09:23:32

`求基于XILINX的FPGA數(shù)據(jù)采集系統(tǒng),感激不盡!`

2015-06-29 22:13:07

綜合考慮到圖像采集系統(tǒng)所要求的實時性,可靠性,以及FPGA在數(shù)字電路的設(shè)計中的優(yōu)勢,為此本文討論如何利用FPGA設(shè)計基于LVDS的圖像數(shù)據(jù)采集傳輸系統(tǒng)?

2021-04-08 06:48:28

介紹一種基于DSP和以太網(wǎng)的數(shù)據(jù)采集處理系統(tǒng)。論述數(shù)據(jù)采集處理系統(tǒng)中的以太網(wǎng)應(yīng)用,分析系統(tǒng)的硬件設(shè)計方案,提出基于實時操作系統(tǒng)DSP/BIOS 進(jìn)行軟件設(shè)計的思路和實現(xiàn)方法。

2009-04-16 09:56:45 24

24 基于DSP和CAN總線的機(jī)車故障數(shù)據(jù)采集系統(tǒng)設(shè)計

2009-05-08 17:19:01 16

16 介紹一種基于DSP和以太網(wǎng)的數(shù)據(jù)采集處理系統(tǒng)。論述數(shù)據(jù)采集處理系統(tǒng)中的以太網(wǎng)應(yīng)用,分析系統(tǒng)的硬件設(shè)計方案,提出基于實時操作系統(tǒng)DSP/BIOS 進(jìn)行軟件設(shè)計的思路和實現(xiàn)方法。

2009-05-15 14:19:19 23

23 介紹一種利用TMS320F240數(shù)字處理芯片(DSP)集成的片內(nèi)A/D轉(zhuǎn)換器實現(xiàn)數(shù)據(jù)采集,LABVIEW作為開發(fā)平臺,兩者之間通過串口實現(xiàn)數(shù)據(jù)通訊的數(shù)據(jù)采集系統(tǒng),詳細(xì)介紹了軟、硬件設(shè)計方案。

2009-07-31 08:26:42 489

489 本文提出了一種用于雷達(dá)回波信號采集的高速數(shù)據(jù)采集系統(tǒng)。該系統(tǒng)實現(xiàn)了對數(shù)十兆赫的回波信號進(jìn)行連續(xù)的采樣和存儲。系統(tǒng)通過FPGA控制數(shù)據(jù)連續(xù)采集、緩沖,通過PCI9056將緩沖區(qū)

2009-08-15 11:45:53 23

23 本文介紹一種基于FPGA 和DSP 的高性能PCI 數(shù)據(jù)采集處理卡的電路原理設(shè)計和PCI接口軟件設(shè)計。該數(shù)據(jù)采集處理卡主要采用TI 公司的TMS320C6416 數(shù)字信號處理器和XILINX公司VIRTEX2 系列的

2009-08-24 10:55:32 34

34 介紹了CAN 總線在航天領(lǐng)域的應(yīng)用狀況,在對CAN 總線技術(shù)和DSP 芯片功能研究的基礎(chǔ)上,設(shè)計了基于CAN 總線和DSP 的雙層數(shù)據(jù)采集系統(tǒng),本數(shù)據(jù)采集系統(tǒng)對于CAN 總線技術(shù)在航天領(lǐng)域

2009-09-26 09:11:39 23

23 本文提出了一種基于ARM 的藍(lán)牙無線數(shù)據(jù)采集系統(tǒng)。結(jié)合嵌入式技術(shù)與藍(lán)牙技術(shù)的優(yōu)勢,解決了傳統(tǒng)工業(yè)現(xiàn)場數(shù)據(jù)采集系統(tǒng)中無法同時滿足低功耗、低價格與高性能,并受到電纜布

2010-01-20 14:12:33 69

69 設(shè)計了基于Matlab 和VC 混合編程的DSP 數(shù)據(jù)采集系統(tǒng),實現(xiàn)了在Matlab 平臺上控制和操作DSP 目標(biāo)板進(jìn)行數(shù)據(jù)采集,并把采集的數(shù)據(jù)上傳到Matlab 平臺進(jìn)行實時分析處理和圖形顯示,然

2010-01-25 14:43:13 50

50 基于DSP的線列陣流噪聲數(shù)據(jù)采集系統(tǒng),針對拖曳線列陣聲吶的特點,為了能測試到對其性能影響最大的流噪聲,采用先進(jìn)的DSP+CPLD結(jié)構(gòu),實現(xiàn)對多通道聲吶信號的檢測并對其分時采樣,然后

2010-07-21 17:11:49 18

18 數(shù)據(jù)采集儀F9164-DZ200產(chǎn)品是集傳統(tǒng)數(shù)據(jù)采集器與3G/4G/5G、以太網(wǎng)、LoRa、藍(lán)牙、GNSS等多種通信功能與一體

2024-03-27 14:33:28

設(shè)計一種基于FPGA的多通道同步數(shù)據(jù)采集存儲系統(tǒng),分為多通道同步數(shù)據(jù)采集模塊和數(shù)據(jù)存儲模塊。系統(tǒng)設(shè)計采用多通道數(shù)據(jù)的同步實時采集以及壞塊檢測技術(shù)。多通道同步數(shù)據(jù)采集

2010-12-27 15:31:33 70

70 銀河數(shù)據(jù)采集分析系統(tǒng)——軟件介紹 數(shù)據(jù)采集系統(tǒng)主要是通過以太網(wǎng)對WP4000變頻功率分析儀、DP1000直流功率表、VFE2000數(shù)據(jù)采集儀、EV

2024-10-08 13:33:21

采用FPGA的高速數(shù)據(jù)采集系統(tǒng)

隨著科學(xué)技術(shù)的發(fā)展,數(shù)據(jù)采集技術(shù)進(jìn)入到越來越多的領(lǐng)域。目前,已廣泛應(yīng)用于通信,圖像處理,軍事應(yīng)用,消費(fèi)電子,智能控制等方面

2009-04-20 11:03:13 2320

2320

基于USB2.0與FPGA技術(shù)的高速數(shù)據(jù)采集系統(tǒng)的設(shè)計

基于USB2.0與FPGA技術(shù)的高速數(shù)據(jù)采集系統(tǒng)的設(shè)計

近年來筆記本電腦迅速普及和更新,其中大部分已經(jīng)

2009-04-22 19:56:15 1960

1960

基于A/D和DSP的高速數(shù)據(jù)采集技術(shù)

中頻信號分為和差兩路,高速A/D與DSP組成的數(shù)據(jù)采集系統(tǒng)要分別對這兩路信號進(jìn)行采集。對于兩路數(shù)據(jù)采集電路,A/

2009-10-17 10:17:41 1546

1546

基于DSP和MAX1420的高速數(shù)據(jù)采集系統(tǒng)設(shè)計

1 引言

數(shù)據(jù)采集系統(tǒng)是通信與信息技術(shù)領(lǐng)域中重要的功能模塊,應(yīng)用廣泛。

2009-12-21 17:07:15 1165

1165

基于CPLD/FPGA高速數(shù)據(jù)采集系統(tǒng)的設(shè)計

0 引 言 傳統(tǒng)的數(shù)據(jù)采集系統(tǒng)一般采用單片機(jī),系統(tǒng)大多通過PCI總線完成數(shù)據(jù)的傳輸。其缺點是數(shù)學(xué)運(yùn)算能力差;

2010-01-27 09:35:01 792

792

基于ARM的藍(lán)牙實時數(shù)據(jù)采集系統(tǒng)的設(shè)計

摘要:本文提出了一種基于ARM的藍(lán)牙無線數(shù)據(jù)采集系統(tǒng)。結(jié)合嵌入式技術(shù)與藍(lán)牙技術(shù)的優(yōu)勢,解決了傳統(tǒng)工業(yè)現(xiàn)場數(shù)據(jù)采集系統(tǒng)中

2010-02-02 11:27:03 1375

1375

利用DSP和USB的三維感應(yīng)測井數(shù)據(jù)采集系統(tǒng)

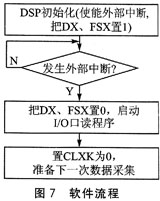

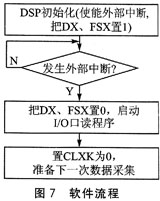

數(shù)據(jù)采集是DSP最基本的應(yīng)用領(lǐng)域,本文設(shè)計的數(shù)據(jù)采集系統(tǒng)利用TI公司的TMS320F2812 DSP芯片。該芯片的主要特點有:150 MI/s(百萬

2010-03-04 10:10:44 960

960

FPGA芯片在高速數(shù)據(jù)采集緩存系統(tǒng)中的應(yīng)用

概 述在高速數(shù)據(jù)采集方面,FPGA有單片機(jī)和DSP無法比擬的優(yōu)勢。FPGA的時鐘頻率高,內(nèi)部時延小,全部控制邏輯都可由硬

2010-03-30 10:51:15 1179

1179

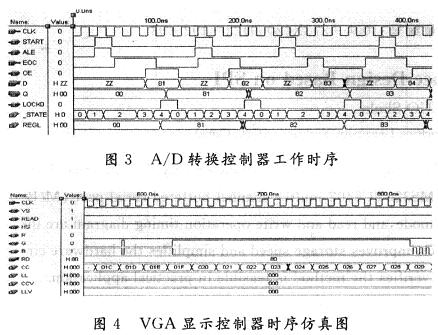

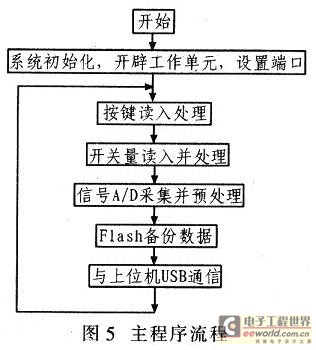

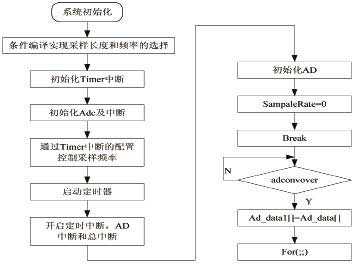

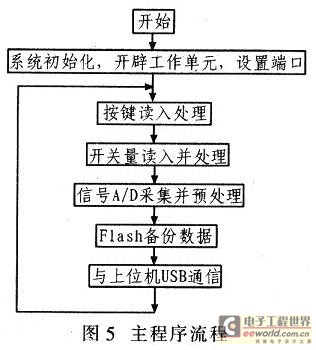

摘要:為準(zhǔn)確地分析工業(yè)生產(chǎn)中的各種數(shù)據(jù)參數(shù),結(jié)合高速DSP和FPGA的特點,設(shè)計一套數(shù)據(jù)采集系統(tǒng),應(yīng)用FPGA的內(nèi)部邏輯實現(xiàn)時序控制,以DSP作為采集系統(tǒng)的核心,對采集到的數(shù)據(jù)進(jìn)行濾波等處理,并將處理后的結(jié)果通過USB口傳輸?shù)接嬎銠C(jī)。設(shè)計中還采用ADC0809模數(shù)轉(zhuǎn)換

2011-02-27 23:04:00 96

96 摘要:隨著數(shù)字信號處理技術(shù)和計算機(jī)技術(shù)的不斷發(fā)展,基于DSP的PCI總線數(shù)據(jù)采集系統(tǒng)將會得到越來越廣泛的應(yīng)用。以實際開發(fā)的系統(tǒng)為背景,詳細(xì)論述了基于DSP的PCI總線結(jié)構(gòu)的數(shù)據(jù)采集系統(tǒng)硬件及軟件設(shè)計方案和實現(xiàn)方法。 關(guān)鍵詞:DSP;PCI總線;驅(qū)動模型;數(shù)字

2011-02-28 00:36:31 119

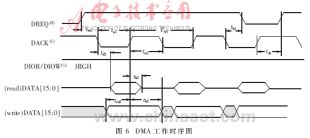

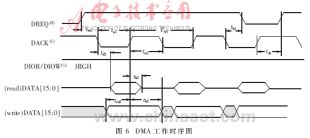

119 摘要:在介紹電容層析成像系統(tǒng)組成原理的基礎(chǔ)上,重新構(gòu)建了一套數(shù)字化的數(shù)據(jù)采集系統(tǒng),它具有較高的采集速度和分辨率真,著重分析了FPGA控制A/D采集和DSP響應(yīng)中斷進(jìn)行DMA傳輸?shù)挠嘘P(guān)問題。 關(guān)鍵詞:DSP DMA 中斷服務(wù)程序 ECT

2011-02-28 12:36:44 50

50 摘要:在FPGA+DSP構(gòu)建的便件平臺上,以鏈路口(LINKPORT)通信協(xié)議為根據(jù),實現(xiàn)紅外圖像數(shù)據(jù)采集與顯示。重點描述紅外圖像數(shù)據(jù)采集與經(jīng)過LINKPORT傳入DSP,圖像壓縮與經(jīng)過LINKPORT傳出DSP以及圖像數(shù)據(jù)緩存與顯示,最后介紹了程序高度過程中的方法。樣機(jī)在實

2011-03-01 00:11:12 89

89 文章介紹了一種基于DSP爭FPGA結(jié)構(gòu)的高精度測井數(shù)據(jù)采集系統(tǒng)的設(shè)計方法,包括信號調(diào)理、數(shù)據(jù)采集、數(shù)據(jù)處理等。整個系統(tǒng)使用16位高精度A/D轉(zhuǎn)換芯片AD974。數(shù)字電路部分采用Xilinx公司

2011-09-08 17:46:55 71

71 針對數(shù)據(jù)采集系統(tǒng)有信號形式多樣、實時傳輸和靈活配置的要求,介紹了一種基于FPGA的數(shù)據(jù)采集和傳輸系統(tǒng),以及系統(tǒng)數(shù)字電路的程序設(shè)計。該系統(tǒng)以現(xiàn)場可編程邏輯陣列(FPGA)作為

2011-09-29 17:31:04 54

54 中頻信號分為和差兩路,高速A/D與DSP組成的數(shù)據(jù)采集系統(tǒng)要分別對這兩路信號進(jìn)行采集。對于兩路數(shù)據(jù)采集電路,A/D與DSP的接口連接是一樣的。兩個A/D同時將和路與差路信號采

2012-03-28 10:41:38 6328

6328

設(shè)計了一個基于FPGA的數(shù)據(jù)采集系統(tǒng),并用Verilog HDL語言作為描述語言實現(xiàn)了對TLC0820的采樣控制和FPGA的數(shù)據(jù)處理等過程的控制,以Xilinx ISE 9.1i軟件為平臺,進(jìn)行了設(shè)計輸入、分析與綜合、

2012-05-08 15:17:06 80

80 通道數(shù)據(jù)采集系統(tǒng)。所設(shè)計的系統(tǒng)通過PCI9054 橋接芯片實現(xiàn)FPGA 局部總線到PMC/PCI總線的轉(zhuǎn)換,而后再通過PMC/PCI總線完成數(shù)據(jù)采集系統(tǒng)與上層母板的連接和通訊。

2015-12-18 15:48:43 138

138 基于LABVIEW與DSP串口的數(shù)據(jù)采集系統(tǒng)。

2016-01-20 16:26:53 45

45 高速數(shù)據(jù)采集系統(tǒng)中的FPGA的設(shè)計,下來看看

2016-05-10 11:24:33 15

15 基于FPGA的AD73360數(shù)據(jù)采集方法

2016-05-10 11:24:33 30

30 基于FPGA的PXI數(shù)據(jù)采集系統(tǒng)設(shè)計,下來看看

2016-05-10 13:45:28 36

36 于FPGA的高速多路數(shù)據(jù)采集系統(tǒng)的設(shè)計。

2016-05-10 13:45:28 41

41 基于FPGA的多通道數(shù)據(jù)采集系統(tǒng)設(shè)計,下來看看。

2016-05-10 13:45:28 64

64 基于FPGA的高速數(shù)據(jù)采集硬件系統(tǒng)設(shè)計.

2016-05-10 17:06:40 48

48 基于FPGA的高速數(shù)據(jù)采集系統(tǒng)接口設(shè)計.

2016-05-10 17:06:40 27

27 基于FPGA的高速數(shù)據(jù)采集系統(tǒng)的設(shè)計,下來看看

2016-05-10 17:06:40 21

21 基于FPGA的數(shù)據(jù)采集及顯示,下來看看。

2016-05-10 17:46:07 30

30 基于FPGA的數(shù)據(jù)采集系統(tǒng)IEEE1394接口設(shè)計

2016-05-10 17:46:07 12

12 基于FPGA的高速數(shù)據(jù)采集系統(tǒng)設(shè)計,用ad芯片和sdram構(gòu)成高速數(shù)據(jù)采集系統(tǒng)。

2016-05-17 09:49:51 35

35 基于DSP和FPGA技術(shù)的細(xì)胞圖像采集系統(tǒng)設(shè)計

2016-08-26 12:57:52 16

16 基于FPGA的新型高速CCD圖像數(shù)據(jù)采集系統(tǒng)

2016-09-22 13:05:38 22

22 根據(jù)實時監(jiān)控中數(shù)據(jù)采集和計算量繁重的特點,給出了以單片機(jī)和DSP相結(jié)合的雙CPU硬件設(shè)計方案,充分利用了DSP運(yùn)算能力強(qiáng)和單片機(jī)控制能力強(qiáng)的優(yōu)點,實現(xiàn)了系統(tǒng)的快速運(yùn)算和實時控制功能。

2017-09-21 10:01:43 4

4 中低速數(shù)據(jù)采集系統(tǒng)設(shè)計,DSP嵌入式系統(tǒng)開發(fā)典型案例

2017-10-19 10:28:42 17

17 高速數(shù)據(jù)采集系統(tǒng)設(shè)計,DSP嵌入式系統(tǒng)開發(fā)典型案例

2017-10-19 13:29:25 14

14 基于ARM與DSP的聲頻數(shù)據(jù)采集系統(tǒng)設(shè)計

2017-10-20 08:34:12 6

6 基于Matlab和VC混合編程的DSP數(shù)據(jù)采集系統(tǒng)

2017-10-20 09:31:09 4

4 DSP多路同步數(shù)據(jù)采集板設(shè)計

2017-10-20 10:50:01 12

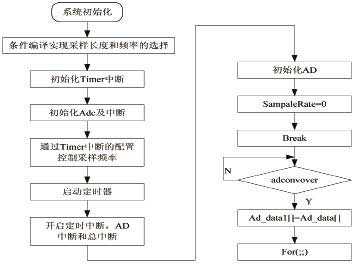

12 設(shè)計方法是應(yīng)用MCU或DSP通過軟件控制數(shù)據(jù)采集的A/D轉(zhuǎn)換,這樣必將頻繁中斷系統(tǒng)的運(yùn)行,從而減弱系統(tǒng)的數(shù)據(jù)運(yùn)算能力,數(shù)據(jù)采集的速度也將受到限制。本文采用DSP+FPGA的方案,由硬件控制A/D轉(zhuǎn)換和數(shù)據(jù)存儲,最大限度地提高系統(tǒng)的信號采集和處

2017-10-23 11:24:18 5

5 FPGA和UART的MCU總線數(shù)據(jù)采集系統(tǒng)設(shè)計

2017-10-31 15:20:51 8

8 設(shè)計采用了DSP與FPGA協(xié)同控制處理,并用藍(lán)牙傳輸代替有線電纜傳輸,有效地解決了DSP和FPGA單獨(dú)處理的不足與有線電纜傳輸?shù)谋锥耍蟠筇岣吡?b class="flag-6" style="color: red">數(shù)據(jù)采集處理能力,拓寬了系統(tǒng)在環(huán)境較為惡劣或特殊場所的應(yīng)用。 1 系統(tǒng)硬件設(shè)計 1.1 系統(tǒng)總體設(shè)計

2017-10-31 15:53:46 5

5 基于DSP與FPGA的藍(lán)牙數(shù)據(jù)采集系統(tǒng)設(shè)計,數(shù)據(jù)采集系統(tǒng)廣泛地應(yīng)用于工業(yè)、國防、圖像處理、信號檢測等領(lǐng)域。DSP處理器是一種高速的數(shù)字信號處理器 數(shù)據(jù)采集系統(tǒng)廣泛地應(yīng)用于工業(yè)、國防、圖像處理、信號

2017-11-24 20:22:01 2494

2494

本文介紹了一種基于藍(lán)牙技術(shù)的無線數(shù)據(jù)采集系統(tǒng)。該系統(tǒng)核心采用TI公司的超低功耗MSP430系列單片機(jī),利用單片機(jī)內(nèi)部自帶的12住AD和DMA進(jìn)行數(shù)據(jù)的采集,并通過藍(lán)牙模塊將采集的數(shù)據(jù)以無線電波的方式發(fā)送到終端設(shè)備。

2018-04-25 15:08:05 19

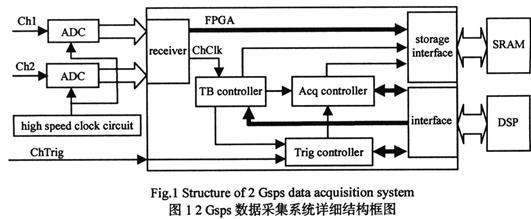

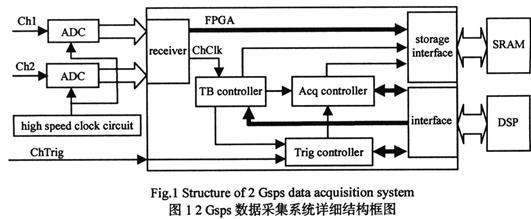

19 本文采用ADC+高頻時鐘電路+FPGA+DSP的結(jié)構(gòu)模式,設(shè)計了一種實時采樣率為2 Gsps的數(shù)字存儲示波器數(shù)據(jù)采集系統(tǒng),為國內(nèi)高速高分辨率的數(shù)據(jù)采集系統(tǒng)的研制提供了一個參考方案。

2019-05-03 09:19:00 7267

7267

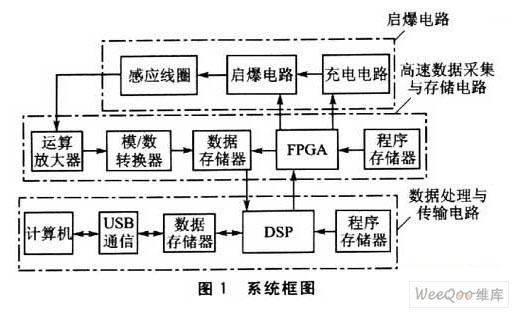

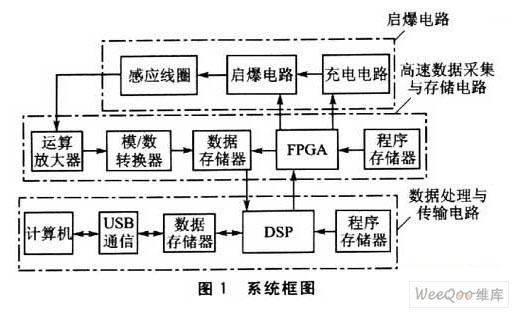

整個系統(tǒng)的組成如圖1所示。當(dāng)啟爆電路在DSP和FPGA的控制下啟爆時,感應(yīng)線圈取出啟爆電流,首先是高速數(shù)據(jù)采集與存儲電路,以FPGA為核心,對數(shù)據(jù)進(jìn)行高速采集與存儲。數(shù)據(jù)存儲完畢,FPGA發(fā)信號告知DSP采集完畢,開始對采集的數(shù)據(jù)進(jìn)行相關(guān)的處理。

2018-10-07 12:03:03 3814

3814

介紹了1種基于FPGA和DSP的高速數(shù)據(jù)采集系統(tǒng)的設(shè)計和實現(xiàn),其FPGA采用Altera公司ACEX 1K系列的EPIK50Tcl443器件,DSP芯片采用TI公司TMs320系列

2018-11-07 17:18:24 20

20 提出了一種新的基于FPGA+DSP的高精度數(shù)字化電源的數(shù)據(jù)采集方案。詳細(xì)闡述了FPGA與DSP之.間vXSPI接口進(jìn)行同步通信,以及用DSP作為控制器并通過PI調(diào)節(jié)產(chǎn)生PWM波形來控制數(shù)字化電源穩(wěn)定性的具體方法。

2018-11-07 17:18:30 23

23 本文介紹了一種基于DSP和FPGA結(jié)構(gòu)的高精度數(shù)據(jù)采集卡的設(shè)計方法,包括數(shù)據(jù)采集、數(shù)據(jù)處理和PCL總線接口設(shè)計。數(shù)據(jù)采集卡使用16位高精度A/D轉(zhuǎn)換芯片AD7676,數(shù)字電路部分采用Altera公司

2019-02-21 15:33:26 14

14 基于FPGA 在高速數(shù)據(jù)采集方面有單片機(jī)和DSP 無法比擬的優(yōu)勢, FPGA 具有時鐘頻率高,內(nèi)部延時小, 全部控制邏輯由硬件完成, 速度快,效率高,組成形式靈活等特點。因此,本文研究并開發(fā)了一個

2020-08-21 16:16:00 32

32 基于FPGA+DSP的高精度數(shù)字電源數(shù)據(jù)采集系統(tǒng)設(shè)計(開關(guān)電源技術(shù)發(fā)展綜述)-該文檔為基于FPGA+DSP的高精度數(shù)字電源數(shù)據(jù)采集系統(tǒng)設(shè)計講解文檔,是一份不錯的參考資料,感興趣的可以下載看看,,,,,,,,,,,,,,,,,

2021-09-24 11:32:01 36

36 FPGA+DSP的高精度數(shù)字電源數(shù)據(jù)采集系統(tǒng)設(shè)計(電源技術(shù)是什么檔次的期刊)-為基于FPGADSP的高精度數(shù)字電源數(shù)據(jù)采集系統(tǒng)設(shè)計講解文檔摘 要:提出了一種新的基于FPGA+DSP的高精度數(shù)字化電源

2021-09-27 11:16:45 19

19 電子發(fā)燒友網(wǎng)站提供《基于DSP的數(shù)據(jù)采集系統(tǒng)開發(fā)與實現(xiàn).pdf》資料免費(fèi)下載

2023-10-07 11:10:58 5

5 點擊上方 藍(lán)字 關(guān)注我們 目前,在數(shù)據(jù)采集系統(tǒng)的硬件設(shè)計方案中,有采用通用單片機(jī)和USB相結(jié)合的方案,也有采用DSP和USB相結(jié)合的方案,前者雖然硬件成本低,但是時鐘頻率較低,難以滿足數(shù)據(jù)采集系統(tǒng)

2023-10-06 14:55:02 2957

2957

一、系統(tǒng)總體方案設(shè)計 為了滿足油田增壓站對數(shù)據(jù)采集的需求,我們設(shè)計了一套基于FPGA的多通道數(shù)據(jù)采集與傳輸系統(tǒng)。系統(tǒng)以FPGA作為主控制器,利用外部ADC芯片完成模擬信號的采集,通過以太網(wǎng)實現(xiàn)與上位

2024-12-09 10:45:02 1311

1311

電子發(fā)燒友App

電子發(fā)燒友App

評論