DSP28335+FPGA+AD7606的數(shù)據(jù)采集系統(tǒng),DSP采用TI公司的TMS320F28335,FPGA使用 ALTERA的Cyclone3 的 EP3C5E144C8N在設(shè)計(jì)的過程中遇到

2016-07-18 16:53:28

DSP28335+FPGA+AD7606的數(shù)據(jù)采集系統(tǒng),DSP采用TI公司的TMS320F28335,FPGA使用 ALTERA的Cyclone3 的 EP3C5E144C8N在設(shè)計(jì)的過程中遇到

2016-07-18 17:13:01

DSP的FPGA的高速數(shù)據(jù)采集系統(tǒng)的研究與設(shè)計(jì),大家可以看看

2015-04-03 21:23:48

在高速數(shù)據(jù)采集方面,FPGA有單片機(jī)和DSP無法比擬的優(yōu)勢。FPGA的時(shí)鐘頻率高,內(nèi)部時(shí)延小,全部控制邏輯都可由硬件完成,而且速度快,組成形式靈活,并可以集成外圍控制、譯碼和接口電路。更最主要

2019-11-01 07:40:10

每日開講---學(xué)習(xí)STM32不得不看的剖析(詳細(xì)分析stm32f10x.h)摘要: 學(xué)習(xí)STM32不得不看的剖析(詳細(xì)分析stm32f10x.h)。/**這里是STM32比較重要的頭文件***************************************************************************

2021-08-05 07:44:05

本文跟大家一起詳細(xì)分析一下USB協(xié)議。

2021-05-24 06:16:36

上一篇文章中,我們詳細(xì)分析了VTIM和VMIN的功能,《嵌入式Linux 串口編程系列2--termios的VMIN和VTIME深入理解》 也明白了這兩個(gè)參數(shù)設(shè)計(jì)的初衷和使用方法,接下來我們 就詳細(xì)

2021-11-05 07:09:55

在嵌入式Linux專題(一)中已經(jīng)對嵌入式Linux系統(tǒng)的架構(gòu)及啟動(dòng)流程有了初步的介紹,本文將詳細(xì)分析嵌入式Linux系統(tǒng)啟動(dòng)流程。

2021-11-05 09:25:29

基于DSP5509 的數(shù)據(jù)采集系統(tǒng)系統(tǒng)采用了DSP + FPGA 的雙核結(jié)構(gòu),由CMOS 感光芯片OV7620 采集圖像,得到數(shù)據(jù)源, FPGA 作為輔助處理器,控制部分外圍器件并協(xié)助采集數(shù)據(jù)

2009-04-28 10:47:02

DVI接口詳細(xì)分析DVI 接口規(guī)格和定義 DVI 有DVI 1.0 和DVI 2.0 兩種標(biāo)準(zhǔn),其中 DVI 1.0 僅用了其中的一組信號傳輸信道(data0-data2 ),傳輸圖像的最高像素時(shí)鐘

2012-08-11 09:51:00

:基于LabVIEW 的語音數(shù)據(jù)采集與分析系統(tǒng)設(shè)計(jì)要求利用聲卡的DSP技術(shù)和LabVIEW多線程技術(shù),設(shè)計(jì)一種基于聲卡的數(shù)據(jù)采集與分析系統(tǒng),在LabVIEW環(huán)境中實(shí)現(xiàn)音頻信號的采集分析及數(shù)據(jù)存盤重載。

2009-05-24 14:16:04

[url=]uboot代碼詳細(xì)分析[/url]

2016-01-29 13:51:41

優(yōu)勢。項(xiàng)目描述:而要做高速信號處理,不得不借助于FPGA或DSP。最近在研究基于FPGA的數(shù)據(jù)采集系統(tǒng),鑒于fpga在復(fù)雜時(shí)序上難以實(shí)現(xiàn)的瓶頸,故結(jié)合嵌入式的多媒體優(yōu)勢,來實(shí)現(xiàn)FPGA采集信號,嵌入式驅(qū)動(dòng)液晶以及其他多媒體設(shè)備的響應(yīng)輸出。

2015-12-02 16:06:25

申請理由:我是一名在讀研究生,目前在做數(shù)據(jù)采集系統(tǒng),采用的是STM32,做成之后感覺系統(tǒng)不是很穩(wěn)定,精度也不高,后來查了資料,原來DSP更適合做信號處理分析這一類別,所以申請一下。項(xiàng)目描述

2015-09-10 11:18:52

的接口功能,可以對采樣數(shù)據(jù)做進(jìn)一步的處理,并方便與上位機(jī)接口。這樣FPGA和DSP相互配合,各司其職,更能發(fā)揮系統(tǒng)在在數(shù)據(jù)采集和處理上的優(yōu)勢。高速數(shù)據(jù)采集系統(tǒng)主要分作五個(gè)模塊:(1)電源監(jiān)測管理模塊

2015-11-06 10:01:48

對數(shù)據(jù)采集與處理系統(tǒng)提出了新的更高的要求,即高速度、高精度和高實(shí)時(shí)性。對數(shù)據(jù)采集與處理系統(tǒng)的設(shè)計(jì),有以下3種方案可供選擇:(1)A/D+DSP方案在傳統(tǒng)的高速信號處理中,大多采用這種方案。將A/D、D

2019-07-05 06:41:27

三極管特性曲線詳細(xì)分析,特性曲線看不懂,

2015-06-29 16:34:40

基于DSP和現(xiàn)場總線的數(shù)據(jù)采集系統(tǒng)設(shè)計(jì)在電力系統(tǒng)的生產(chǎn)過程中,生產(chǎn)運(yùn)行部門通常有兩方面的考慮:一方面盡量提高設(shè)備與線路的利用率,實(shí)現(xiàn)系統(tǒng)的經(jīng)濟(jì)性;同時(shí)保證電力系統(tǒng)的安全、可靠運(yùn)行,提供高質(zhì)量的電能

2009-12-08 10:28:19

基于FPGA+DSP的高速數(shù)據(jù)采集系統(tǒng)設(shè)計(jì)

2012-06-27 17:23:53

基于FPGA 的DSP 數(shù)據(jù)采集分析系統(tǒng)設(shè)計(jì)

2012-08-20 15:35:41

24期摘 要:傳統(tǒng)的數(shù)據(jù)采集系統(tǒng)大都是由ARM+DSP實(shí)現(xiàn)的,雖然DSP的優(yōu)勢在于數(shù)據(jù)處理,但是隨著FPGA技術(shù)的發(fā)展,很多FPGA已經(jīng)可以取代DSP的作用了。尤其是在高速實(shí)時(shí)的數(shù)據(jù)采集領(lǐng)域,采集

2018-05-09 12:09:43

基于FPGA的數(shù)據(jù)采集系統(tǒng)IEE ... 介紹了數(shù)據(jù)采集系統(tǒng)中以FPGA為處理核心、采用TI公司接口芯片的IEEE1394接口設(shè)計(jì),給出了系統(tǒng)硬件設(shè)計(jì)和FPGA邏輯設(shè)計(jì),討論了IEEE1394總線

2012-08-11 15:43:47

目前,在數(shù)據(jù)采集系統(tǒng)的硬件設(shè)計(jì)方案中,有采用通用單片機(jī)和USB相結(jié)合的方案,也有采用DSP和USB相結(jié)合的方案,前者雖然硬件成本低,但是時(shí)鐘頻率較低,難以滿足數(shù)據(jù)采集系統(tǒng)對速度要求;后者雖然可以實(shí)現(xiàn)

2019-09-05 07:22:57

本帖最后由 eehome 于 2013-1-5 10:11 編輯

基于labview與dsp串口的數(shù)據(jù)采集系統(tǒng)

2012-05-10 15:28:18

高速連續(xù)數(shù)據(jù)采集系統(tǒng)的背景及功能是什么?如何利用FPGA實(shí)現(xiàn)高速連續(xù)數(shù)據(jù)采集系統(tǒng)設(shè)計(jì)?FPGA在高速連續(xù)數(shù)據(jù)采集系統(tǒng)中的應(yīng)用有哪些?

2021-04-08 06:19:37

工程師應(yīng)該掌握的20個(gè)模擬電路(詳細(xì)分析及參考答案)

2013-08-17 09:58:13

工程師應(yīng)該掌握的20個(gè)模擬電路(詳細(xì)分析及參考答案).pdf

2013-04-07 13:28:38

求大神詳細(xì)分析電路圖個(gè)元器件作用

2013-08-04 15:46:35

內(nèi)含參考答案以及詳細(xì)分析

2023-10-07 07:15:56

本文檔的主要內(nèi)容詳細(xì)介紹的是硬件工程師必須掌握的20個(gè)重要模擬電路的概述和參考答案以及詳細(xì)分析

2023-09-27 08:22:32

電子工程師需要掌握的20個(gè)模擬電路的詳細(xì)分析

2023-09-28 06:22:26

本帖最后由 eehome 于 2013-1-5 09:52 編輯

電源電路圖最最最最最詳細(xì)分析(轉(zhuǎn)一網(wǎng)友)

2012-07-31 11:37:21

給大家詳細(xì)分析一下艾德克斯車載充電機(jī)的測試方案

2021-05-08 08:38:05

綜合考慮到圖像采集系統(tǒng)所要求的實(shí)時(shí)性,可靠性,以及FPGA在數(shù)字電路的設(shè)計(jì)中的優(yōu)勢,為此本文討論如何利用FPGA設(shè)計(jì)基于LVDS的圖像數(shù)據(jù)采集傳輸系統(tǒng)?

2021-04-08 06:48:28

請問一下怎樣對stm32的啟動(dòng)代碼進(jìn)行詳細(xì)分析呢?

2021-11-26 07:10:48

介紹一種基于DSP和以太網(wǎng)的數(shù)據(jù)采集處理系統(tǒng)。論述數(shù)據(jù)采集處理系統(tǒng)中的以太網(wǎng)應(yīng)用,分析系統(tǒng)的硬件設(shè)計(jì)方案,提出基于實(shí)時(shí)操作系統(tǒng)DSP/BIOS 進(jìn)行軟件設(shè)計(jì)的思路和實(shí)現(xiàn)方法。

2009-04-16 09:56:45 24

24 基于DSP和CAN總線的機(jī)車故障數(shù)據(jù)采集系統(tǒng)設(shè)計(jì)

2009-05-08 17:19:01 16

16 介紹一種基于DSP和以太網(wǎng)的數(shù)據(jù)采集處理系統(tǒng)。論述數(shù)據(jù)采集處理系統(tǒng)中的以太網(wǎng)應(yīng)用,分析系統(tǒng)的硬件設(shè)計(jì)方案,提出基于實(shí)時(shí)操作系統(tǒng)DSP/BIOS 進(jìn)行軟件設(shè)計(jì)的思路和實(shí)現(xiàn)方法。

2009-05-15 14:19:19 23

23 介紹一種利用TMS320F240數(shù)字處理芯片(DSP)集成的片內(nèi)A/D轉(zhuǎn)換器實(shí)現(xiàn)數(shù)據(jù)采集,LABVIEW作為開發(fā)平臺(tái),兩者之間通過串口實(shí)現(xiàn)數(shù)據(jù)通訊的數(shù)據(jù)采集系統(tǒng),詳細(xì)介紹了軟、硬件設(shè)計(jì)方案。

2009-07-31 08:26:42 489

489 介紹了基于CAN總線的車輛虛擬儀表多路數(shù)據(jù)采集系統(tǒng)的設(shè)計(jì)方法,給出了系統(tǒng)詳細(xì)框圖和關(guān)鍵電路圖.詳細(xì)分析了CAN通信子程序,并給出了CAN通信初始化子程序、數(shù)據(jù)發(fā)送和中斷服務(wù)

2009-08-12 17:10:31 32

32 介紹了CAN 總線在航天領(lǐng)域的應(yīng)用狀況,在對CAN 總線技術(shù)和DSP 芯片功能研究的基礎(chǔ)上,設(shè)計(jì)了基于CAN 總線和DSP 的雙層數(shù)據(jù)采集系統(tǒng),本數(shù)據(jù)采集系統(tǒng)對于CAN 總線技術(shù)在航天領(lǐng)域

2009-09-26 09:11:39 23

23 本文提出了一種基于ARM 的藍(lán)牙無線數(shù)據(jù)采集系統(tǒng)。結(jié)合嵌入式技術(shù)與藍(lán)牙技術(shù)的優(yōu)勢,解決了傳統(tǒng)工業(yè)現(xiàn)場數(shù)據(jù)采集系統(tǒng)中無法同時(shí)滿足低功耗、低價(jià)格與高性能,并受到電纜布

2010-01-20 14:12:33 69

69 設(shè)計(jì)了基于Matlab 和VC 混合編程的DSP 數(shù)據(jù)采集系統(tǒng),實(shí)現(xiàn)了在Matlab 平臺(tái)上控制和操作DSP 目標(biāo)板進(jìn)行數(shù)據(jù)采集,并把采集的數(shù)據(jù)上傳到Matlab 平臺(tái)進(jìn)行實(shí)時(shí)分析處理和圖形顯示,然

2010-01-25 14:43:13 50

50 設(shè)計(jì)一種基于FPGA的多通道同步數(shù)據(jù)采集存儲(chǔ)系統(tǒng),分為多通道同步數(shù)據(jù)采集模塊和數(shù)據(jù)存儲(chǔ)模塊。系統(tǒng)設(shè)計(jì)采用多通道數(shù)據(jù)的同步實(shí)時(shí)采集以及壞塊檢測技術(shù)。多通道同步數(shù)據(jù)采集

2010-12-27 15:31:33 70

70 延時(shí)開關(guān)電路圖及詳細(xì)分析

圖1:

2007-11-08 10:20:09 15438

15438 銀河數(shù)據(jù)采集分析系統(tǒng)——軟件介紹 數(shù)據(jù)采集系統(tǒng)主要是通過以太網(wǎng)對WP4000變頻功率分析儀、DP1000直流功率表、VFE2000數(shù)據(jù)采集儀、EV

2024-10-08 13:33:21

基于DSP和MAX1420的高速數(shù)據(jù)采集系統(tǒng)設(shè)計(jì)

1 引言

數(shù)據(jù)采集系統(tǒng)是通信與信息技術(shù)領(lǐng)域中重要的功能模塊,應(yīng)用廣泛。

2009-12-21 17:07:15 1165

1165

焊接技術(shù)詳細(xì)分析

焊接實(shí)質(zhì)上是將元器件高質(zhì)量連接起來最容易實(shí)現(xiàn)的方法,對于DIY高手來說,光能掌握電腦配件的性能和參數(shù)

2010-01-26 10:46:22 2161

2161 基于ARM的藍(lán)牙實(shí)時(shí)數(shù)據(jù)采集系統(tǒng)的設(shè)計(jì)

摘要:本文提出了一種基于ARM的藍(lán)牙無線數(shù)據(jù)采集系統(tǒng)。結(jié)合嵌入式技術(shù)與藍(lán)牙技術(shù)的優(yōu)勢,解決了傳統(tǒng)工業(yè)現(xiàn)場數(shù)據(jù)采集系統(tǒng)中

2010-02-02 11:27:03 1375

1375

電子整流器工作原理詳細(xì)分析

2010-02-27 10:43:51 25837

25837 FPGA芯片在高速數(shù)據(jù)采集緩存系統(tǒng)中的應(yīng)用

概 述在高速數(shù)據(jù)采集方面,FPGA有單片機(jī)和DSP無法比擬的優(yōu)勢。FPGA的時(shí)鐘頻率高,內(nèi)部時(shí)延小,全部控制邏輯都可由硬

2010-03-30 10:51:15 1179

1179

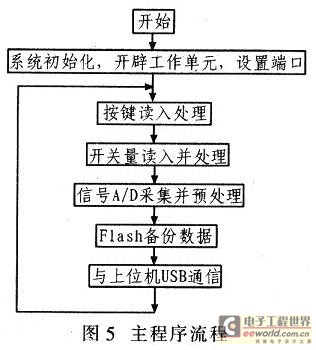

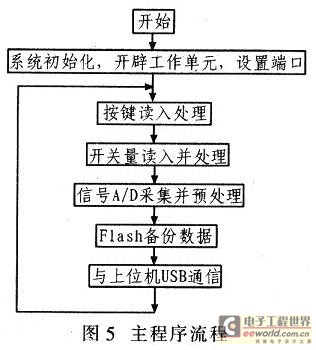

摘要:為準(zhǔn)確地分析工業(yè)生產(chǎn)中的各種數(shù)據(jù)參數(shù),結(jié)合高速DSP和FPGA的特點(diǎn),設(shè)計(jì)一套數(shù)據(jù)采集系統(tǒng),應(yīng)用FPGA的內(nèi)部邏輯實(shí)現(xiàn)時(shí)序控制,以DSP作為采集系統(tǒng)的核心,對采集到的數(shù)據(jù)進(jìn)行濾波等處理,并將處理后的結(jié)果通過USB口傳輸?shù)接?jì)算機(jī)。設(shè)計(jì)中還采用ADC0809模數(shù)轉(zhuǎn)換

2011-02-27 23:04:00 96

96 摘要:隨著數(shù)字信號處理技術(shù)和計(jì)算機(jī)技術(shù)的不斷發(fā)展,基于DSP的PCI總線數(shù)據(jù)采集系統(tǒng)將會(huì)得到越來越廣泛的應(yīng)用。以實(shí)際開發(fā)的系統(tǒng)為背景,詳細(xì)論述了基于DSP的PCI總線結(jié)構(gòu)的數(shù)據(jù)采集系統(tǒng)硬件及軟件設(shè)計(jì)方案和實(shí)現(xiàn)方法。 關(guān)鍵詞:DSP;PCI總線;驅(qū)動(dòng)模型;數(shù)字

2011-02-28 00:36:31 119

119 摘要:在介紹電容層析成像系統(tǒng)組成原理的基礎(chǔ)上,重新構(gòu)建了一套數(shù)字化的數(shù)據(jù)采集系統(tǒng),它具有較高的采集速度和分辨率真,著重分析了FPGA控制A/D采集和DSP響應(yīng)中斷進(jìn)行DMA傳輸?shù)挠嘘P(guān)問題。 關(guān)鍵詞:DSP DMA 中斷服務(wù)程序 ECT

2011-02-28 12:36:44 50

50 摘要:在FPGA+DSP構(gòu)建的便件平臺(tái)上,以鏈路口(LINKPORT)通信協(xié)議為根據(jù),實(shí)現(xiàn)紅外圖像數(shù)據(jù)采集與顯示。重點(diǎn)描述紅外圖像數(shù)據(jù)采集與經(jīng)過LINKPORT傳入DSP,圖像壓縮與經(jīng)過LINKPORT傳出DSP以及圖像數(shù)據(jù)緩存與顯示,最后介紹了程序高度過程中的方法。樣機(jī)在實(shí)

2011-03-01 00:11:12 89

89 文章介紹了一種基于DSP爭FPGA結(jié)構(gòu)的高精度測井數(shù)據(jù)采集系統(tǒng)的設(shè)計(jì)方法,包括信號調(diào)理、數(shù)據(jù)采集、數(shù)據(jù)處理等。整個(gè)系統(tǒng)使用16位高精度A/D轉(zhuǎn)換芯片AD974。數(shù)字電路部分采用Xilinx公司

2011-09-08 17:46:55 71

71 設(shè)計(jì)了一個(gè)基于FPGA的數(shù)據(jù)采集系統(tǒng),并用Verilog HDL語言作為描述語言實(shí)現(xiàn)了對TLC0820的采樣控制和FPGA的數(shù)據(jù)處理等過程的控制,以Xilinx ISE 9.1i軟件為平臺(tái),進(jìn)行了設(shè)計(jì)輸入、分析與綜合、

2012-05-08 15:17:06 80

80 十二五規(guī)劃教材大學(xué)電路(邱關(guān)源、羅先覺版)二端口網(wǎng)絡(luò)的詳細(xì)分析和經(jīng)典例題以及解題方法

2015-12-23 18:15:36 0

0 基于LABVIEW與DSP串口的數(shù)據(jù)采集系統(tǒng)。

2016-01-20 16:26:53 45

45 高速數(shù)據(jù)采集系統(tǒng)中的FPGA的設(shè)計(jì),下來看看

2016-05-10 11:24:33 15

15 基于FPGA的PXI數(shù)據(jù)采集系統(tǒng)設(shè)計(jì),下來看看

2016-05-10 13:45:28 36

36 基于FPGA的多通道數(shù)據(jù)采集系統(tǒng)設(shè)計(jì),下來看看。

2016-05-10 13:45:28 64

64 基于FPGA的高速數(shù)據(jù)采集硬件系統(tǒng)設(shè)計(jì).

2016-05-10 17:06:40 48

48 基于FPGA的高速數(shù)據(jù)采集系統(tǒng)接口設(shè)計(jì).

2016-05-10 17:06:40 27

27 基于FPGA的高速數(shù)據(jù)采集系統(tǒng)的設(shè)計(jì),下來看看

2016-05-10 17:06:40 21

21 基于FPGA的高速數(shù)據(jù)采集系統(tǒng)設(shè)計(jì),用ad芯片和sdram構(gòu)成高速數(shù)據(jù)采集系統(tǒng)。

2016-05-17 09:49:51 35

35 近期的幾個(gè)單片機(jī)例程及詳細(xì)分析,感興趣的可以看看。

2016-06-21 17:02:48 3

3 Buck變換器原理詳細(xì)分析

2017-09-15 17:26:25 30

30 基于ARM與DSP的聲頻數(shù)據(jù)采集系統(tǒng)設(shè)計(jì)

2017-10-20 08:34:12 6

6 基于Matlab和VC混合編程的DSP數(shù)據(jù)采集系統(tǒng)

2017-10-20 09:31:09 4

4 設(shè)計(jì)方法是應(yīng)用MCU或DSP通過軟件控制數(shù)據(jù)采集的A/D轉(zhuǎn)換,這樣必將頻繁中斷系統(tǒng)的運(yùn)行,從而減弱系統(tǒng)的數(shù)據(jù)運(yùn)算能力,數(shù)據(jù)采集的速度也將受到限制。本文采用DSP+FPGA的方案,由硬件控制A/D轉(zhuǎn)換和數(shù)據(jù)存儲(chǔ),最大限度地提高系統(tǒng)的信號采集和處

2017-10-23 11:24:18 5

5 設(shè)計(jì)采用了DSP與FPGA協(xié)同控制處理,并用藍(lán)牙傳輸代替有線電纜傳輸,有效地解決了DSP和FPGA單獨(dú)處理的不足與有線電纜傳輸?shù)谋锥耍蟠筇岣吡?b class="flag-6" style="color: red">數(shù)據(jù)采集處理能力,拓寬了系統(tǒng)在環(huán)境較為惡劣或特殊場所的應(yīng)用。 1 系統(tǒng)硬件設(shè)計(jì) 1.1 系統(tǒng)總體設(shè)計(jì)

2017-10-31 15:53:46 5

5 現(xiàn)代化生產(chǎn)和科學(xué)研究對圖像采集系統(tǒng)的要求日益提高。傳統(tǒng)的圖像采集卡速度慢、處理功能簡單,不能很好地滿足特殊要求,因此,我們構(gòu)建了 高速圖像采集 系統(tǒng)。它主要包括圖像采集模塊、圖像低級處理模塊以及總線接口模塊等。這些模塊是在 FPGA 中利用 VHDL 編程實(shí)現(xiàn)的。高速圖像采集系統(tǒng)主要用于視覺檢測。

2017-11-24 19:00:02 3083

3083

設(shè)計(jì)采用了DSP與FPGA協(xié)同控制處理,并用藍(lán)牙傳輸代替有線電纜傳輸,有效地解決了DSP和FPGA單獨(dú)處理的不足與有線電纜傳輸?shù)谋锥耍蟠筇岣吡?b class="flag-6" style="color: red">數(shù)據(jù)采集處理能力,拓寬了系統(tǒng)在環(huán)境較為惡劣或特殊場所的應(yīng)用。 1 系統(tǒng)硬件設(shè)計(jì) 1.1系統(tǒng)總體設(shè)計(jì) 基

2017-12-02 17:45:54 830

830 本文介紹了基于FPGA的數(shù)據(jù)采集系統(tǒng)電路的工作原理和設(shè)計(jì)過程。根據(jù)數(shù)據(jù)采集技術(shù)原理,以Altera公司的EP2C8Q208C8N芯片為核心器件,通過ADC0809采集數(shù)據(jù),并用DAC0832輸出數(shù)據(jù)

2018-09-06 14:25:50 25

25 為提高處理能力,設(shè)計(jì)了2×2并行流水結(jié)構(gòu)的FPGA矩陣并作為處理核心用于高速數(shù)據(jù)采集與控制。在分析了多片FPGA的同步驅(qū)動(dòng)原理以及協(xié)作模型的基礎(chǔ)上,綜合利用雙時(shí)鐘沿觸發(fā)傳輸、資源重復(fù)與時(shí)間重疊技術(shù)

2018-10-23 19:32:54 5

5 介紹了1種基于FPGA和DSP的高速數(shù)據(jù)采集系統(tǒng)的設(shè)計(jì)和實(shí)現(xiàn),其FPGA采用Altera公司ACEX 1K系列的EPIK50Tcl443器件,DSP芯片采用TI公司TMs320系列

2018-11-07 17:18:24 20

20 提出了一種新的基于FPGA+DSP的高精度數(shù)字化電源的數(shù)據(jù)采集方案。詳細(xì)闡述了FPGA與DSP之.間vXSPI接口進(jìn)行同步通信,以及用DSP作為控制器并通過PI調(diào)節(jié)產(chǎn)生PWM波形來控制數(shù)字化電源穩(wěn)定性的具體方法。

2018-11-07 17:18:30 23

23 物聯(lián)網(wǎng)的產(chǎn)業(yè)生態(tài)是怎樣的詳細(xì)分析概述

2018-12-08 10:00:07 5739

5739 本文介紹了一種基于DSP和FPGA結(jié)構(gòu)的高精度數(shù)據(jù)采集卡的設(shè)計(jì)方法,包括數(shù)據(jù)采集、數(shù)據(jù)處理和PCL總線接口設(shè)計(jì)。數(shù)據(jù)采集卡使用16位高精度A/D轉(zhuǎn)換芯片AD7676,數(shù)字電路部分采用Altera公司

2019-02-21 15:33:26 14

14 本文檔的主要內(nèi)容詳細(xì)介紹的是硬件工程師必須掌握的20個(gè)重要模擬電路的概述和參考答案以及詳細(xì)分析

2019-11-13 16:24:26 177

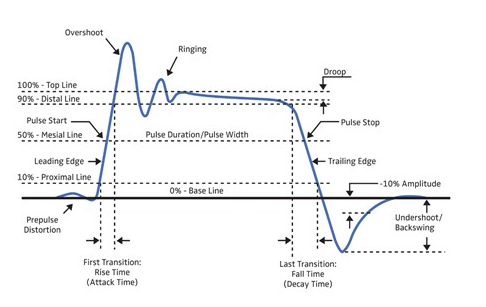

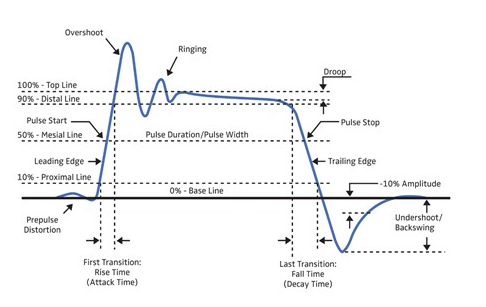

177 Boonton的功率表非常詳細(xì)的波形跟蹤可實(shí)現(xiàn)精確的測量,有效的校準(zhǔn),以及對線性和脈沖射頻部件及系統(tǒng)的詳細(xì)分析。

2020-01-10 09:56:00 1355

1355

本文檔的主要內(nèi)容詳細(xì)介紹的是電子電路的復(fù)習(xí)題詳細(xì)分析

2020-04-15 08:00:00 16

16 基于FPGA 在高速數(shù)據(jù)采集方面有單片機(jī)和DSP 無法比擬的優(yōu)勢, FPGA 具有時(shí)鐘頻率高,內(nèi)部延時(shí)小, 全部控制邏輯由硬件完成, 速度快,效率高,組成形式靈活等特點(diǎn)。因此,本文研究并開發(fā)了一個(gè)

2020-08-21 16:16:00 32

32 本文檔的主要內(nèi)容詳細(xì)介紹的是功率放大電路的仿真資料詳細(xì)分析。

2021-02-01 11:28:50 30

30 正激有源鉗位的詳細(xì)分析介紹。

2021-06-16 16:57:07 68

68 基于FPGA+DSP的高精度數(shù)字電源數(shù)據(jù)采集系統(tǒng)設(shè)計(jì)(開關(guān)電源技術(shù)發(fā)展綜述)-該文檔為基于FPGA+DSP的高精度數(shù)字電源數(shù)據(jù)采集系統(tǒng)設(shè)計(jì)講解文檔,是一份不錯(cuò)的參考資料,感興趣的可以下載看看,,,,,,,,,,,,,,,,,

2021-09-24 11:32:01 36

36 的數(shù)據(jù)采集方案。詳細(xì)闡述了

FPGA與DSP之.間vXSPI接口進(jìn)行同步通信,以及用DSP作為控制器并通過PI調(diào)節(jié)產(chǎn)生PWM波形

來控制數(shù)字化電源穩(wěn)定性的具體方法。?關(guān)鍵詞:數(shù)字電源;FPGA;DSP

2021-09-27 11:16:45 19

19 點(diǎn)擊上方 藍(lán)字 關(guān)注我們 目前,在數(shù)據(jù)采集系統(tǒng)的硬件設(shè)計(jì)方案中,有采用通用單片機(jī)和USB相結(jié)合的方案,也有采用DSP和USB相結(jié)合的方案,前者雖然硬件成本低,但是時(shí)鐘頻率較低,難以滿足數(shù)據(jù)采集系統(tǒng)

2023-10-06 14:55:02 2955

2955

機(jī)房托管費(fèi)是一個(gè)復(fù)雜而多變的話題,它受到多種因素的影響,以下是對機(jī)房托管費(fèi)用的詳細(xì)分析,主機(jī)推薦小編為您整理發(fā)布機(jī)房托管費(fèi)詳細(xì)分析。

2025-02-28 09:48:15 1131

1131

電子發(fā)燒友App

電子發(fā)燒友App

評論