上拉(Pull Up )或下拉(Pull Down)電阻(兩者統稱為“拉電阻”)最基本的作用是:將狀態不確定的信號線通過一個電阻將其箝位至高電平(上拉)或低電平(下拉),無論它的具體用法如何,這個基本的作用都是相同的,只是在不同應用場合中會對電阻的阻值要求有所不同,從而也引出了諸多新的概念,本節我們就來小談一下這些內容。

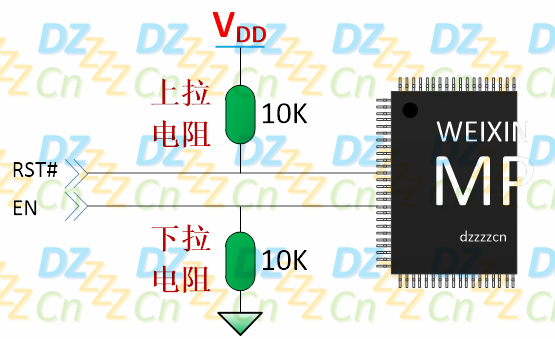

如果拉電阻用于輸入信號引腳,通常的作用是將信號線強制箝位至某個電平,以防止信號線因懸空而出現不確定的狀態,繼而導致系統出現不期望的狀態,如下圖所示:

在實際應用中,10K歐姆的電阻是使用數量最多的拉電阻。需要使用上拉電阻還是下拉電阻,主要取決于電路系統本身的需要,比如,對于高有效的使能控制信號(EN), 我們希望電路系統在上電后應處于無效狀態,則會使用下拉電阻。

假設這個使能信號是用來控制電機的,如果懸空的話,此信號線可能在上電后(或在運行中)受到其它噪聲干擾而誤觸發為高電平,從而導致電機出現不期望的轉動,這肯定不是我們想要的,此時可以增加一個下拉電阻。

而相應的,對于低有效的復位控制信號(RST#),我們希望上電復位后處于無效狀態,則應使用上拉電阻。

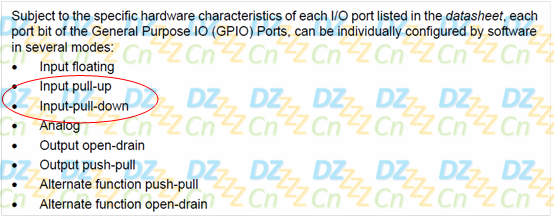

大多數具備邏輯控制功能的芯片(如單片機、FPGA等)都會集成上拉或下拉電阻,用戶可根據需要選擇是否打開,STM32單片機GPIO模式即包含上拉或下拉,如下圖所示(來自ST數據手冊):

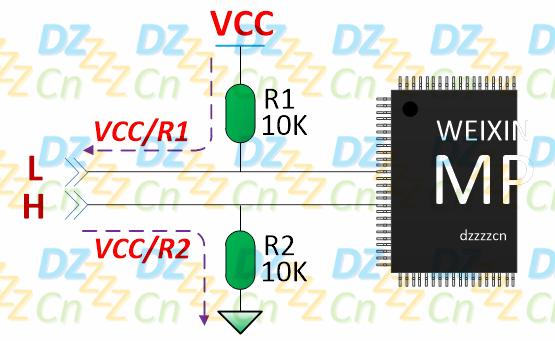

根據拉電阻的阻值大小,我們還可以分為強拉或弱拉(weak pull-up/down),芯片內部集成的拉電阻通常都是弱拉(電阻比較大),拉電阻越小則表示電平能力越強(強拉),可以抵抗外部噪聲的能力也越強(也就是說,不期望出現的干擾噪聲如果要更改強拉的信號電平,則需要的能量也必須相應加強),但是拉電阻越小則相應的功耗也越大,因為正常信號要改變信號線的狀態也需要更多的能量,在能量消耗這一方面,拉電阻是絕不會有所偏頗的,如下圖所示:

對于上拉電阻R1而言,控制信號每次拉低L都會產生VCC/R1的電流消耗(沒有上拉電阻則電流為0),相應的,對于下拉電阻R2而言,控制信號每次拉高H也會產生VCC/R2R 電流消耗(本文假設高電平即為VCC)。

強拉與弱拉之間沒有嚴格說多少歐姆是強弱的分界,一般我們使用的拉電阻都是弱拉,這樣我們仍然可以使用外部控制信號將已經上/下拉的信號線根據需要進行電平的更改。

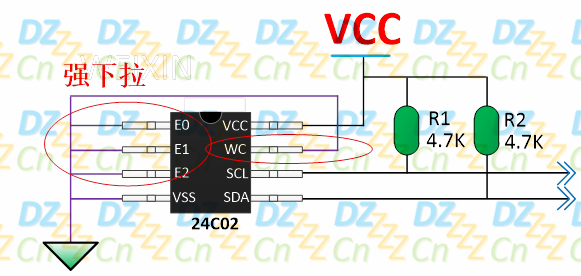

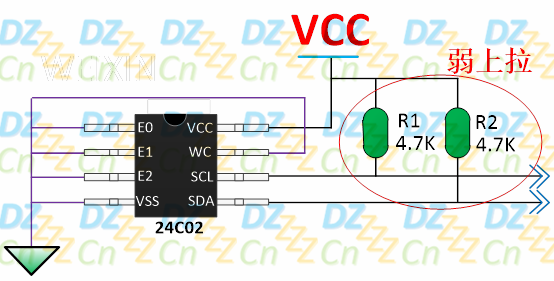

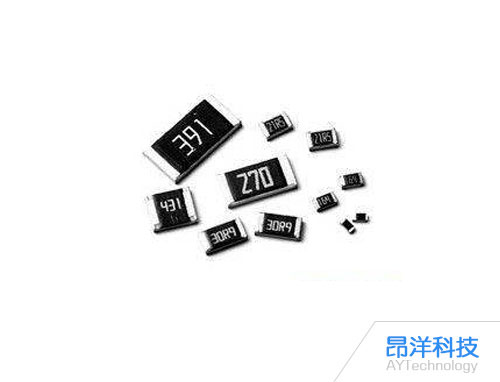

強拉電阻的極端就是零歐姆電阻,亦即將信號線直接與電源或地相連接,比如,對于EEPROM存儲芯片24C02應用電路,如下圖所示:

其中,E0,E1,E2(地址配置位)在應用中通常都是直接強上拉到電源VCC,或強下拉到GND,因為存儲芯片的地址在系統運行過程中是不會再發生變化的,同樣,芯片的寫控制引腳WC(Write Control)也被強下拉到GND。

拉電阻作為輸出(或輸入輸出)時牽涉到的知識點會更多一些,但本質的功能也是將電平箝位,最常見的輸出上拉電阻出現在開集(Open Collector,OC)或開漏(Open Drain,OD)結構的引腳。

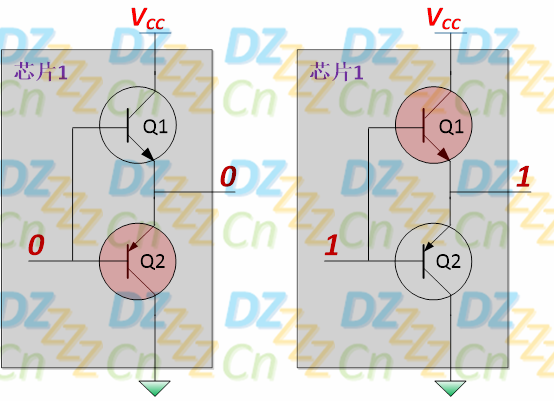

我們有很多芯片的輸出引腳是推挽輸出結構(Output Push-Pull),如下圖所示(還有一種反相輸出的結構,本質也是一樣的):

推挽輸出結構引腳的特點是:無論引腳輸出高電平“H”還是低電平“L”,都有比較強的驅動能力(輸入或輸出電流能力)!

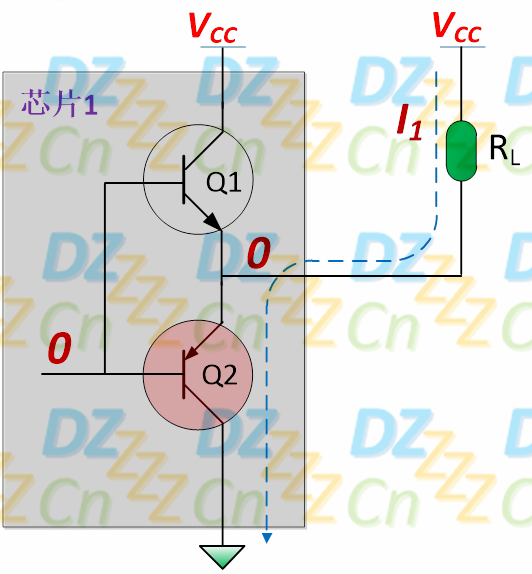

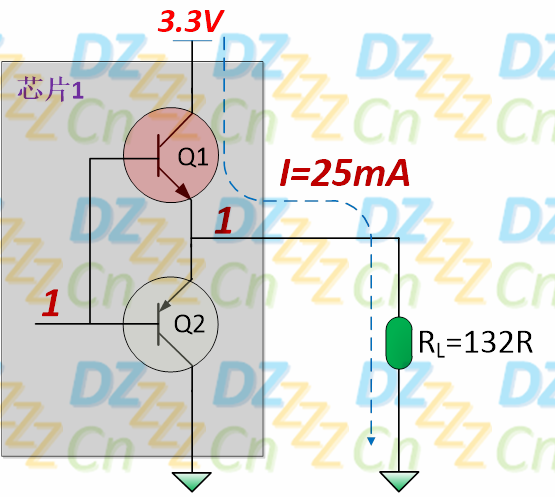

當推挽輸出結構的控制信號為低電平“L”時,Q1截止Q2導通,電流I1由電源VCC經負載RL與三極管Q2流向公共地,我們稱此電流為灌電流(Sink Current),也就是外部電流灌入芯片內部,如下圖所示:

相應的,當推挽輸出結構的控制信號為高電平“H”時,Q1導通Q2截止,電流I1由電源VCC經三極管Q1與負載RL流向公共地,我們稱此電流為拉電流(Source Current),也就是芯片內部可以向外提供的電流(所以稱之為“源電源”),從另一個角度講,也就是外電路可以從芯片中拉走多少電流,如下圖所示:

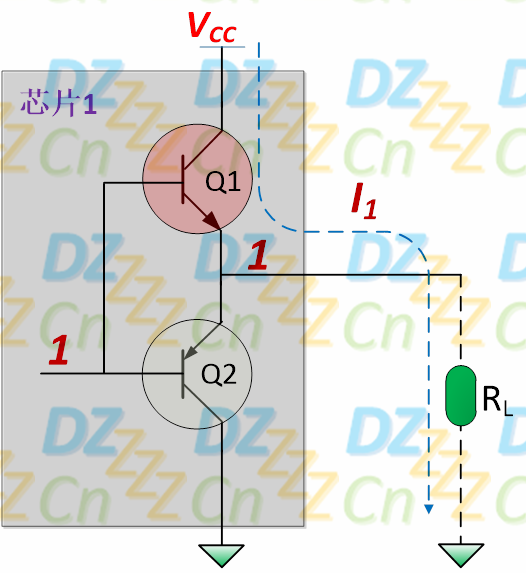

灌電流能力與拉電流能力也稱為芯片引腳的驅動能力。對于任何給定的芯片,引腳的驅動能力都是有限的,如下圖所示為STM32單片機的IO引腳電流驅動能力(來自ST數據手冊):

由上表可知,STM32的IO引腳的驅動能力為25mA,負號“-”表示電流的方向,灌與拉的電流方向是相反的(表中SUNK為SINK的過去分詞)

由于芯片引腳的驅動能力都是有限的,如果引腳驅動的負載比較重,將可能導致輸出電平不正確(無法輸出預定的電平),如下圖所示:

假定芯片的供電電壓為3.3V(忽略晶體管飽和壓降),則輸出最大電流25mA時,負載RL的值約為132歐姆(3.3V/25mA),如果負載值小于132歐姆,則相應輸出電流會更大(超過25mA),但是芯片引腳只能提供最大25mA的電流,因此,輸出電平將會下降(老板你只給我2500月薪,我就只能干2500的活,你要我干更多的活得開更多的工資,一個道理)

一般情況下,這種驅動重負載(小電阻)的電路連接是不會燒毀內部晶體管的,因為內部也是有限流電阻的,換句話講,就算輸出引腳對地短路,輸出電流也不會超過最大的驅動能力(除非是不正規的芯片),當然,在實際應用過程中盡量不要超出引腳的驅動能力。

而OC(OD)的引腳輸出結構有所不同(OC結構存在于三極管,而OD結構存在于場效管,下面以OC輸出結構為例,OD輸出結構的原理是一致的),如下圖所示:

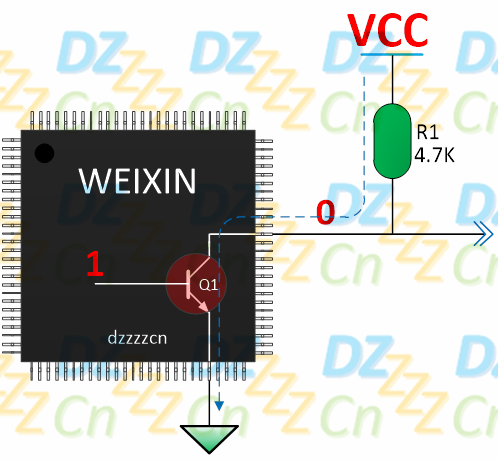

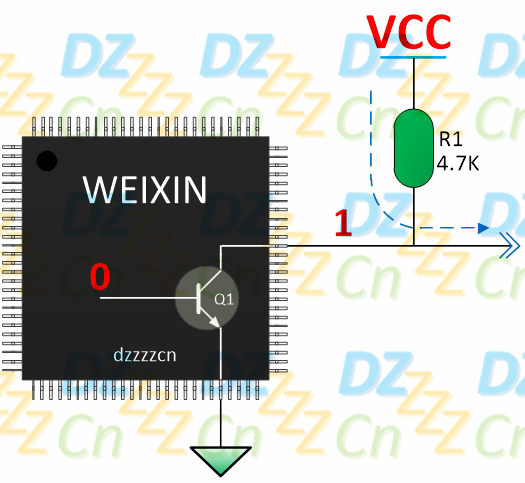

當三極管Q1的驅動控制信號為高電平“H”時,Q1飽和導通,將對應輸出引腳拉為低電平“L”,如下圖所示:

但是當控制驅動信號為低電平“L”時,三極管Q1截止,如果沒有外部上拉電阻的話,該引腳相當于懸空(高阻態),無法輸出高電平,也就是說,OC/OD結構輸出的引腳沒有拉電流(向外部電路提供電流)能力。因此,我們通常都會將OC/OD引腳通過外接電阻上拉到電源電壓VCC,這樣引腳輸出高電平時的拉電流就直接由電源VCC提供,如下圖所示:

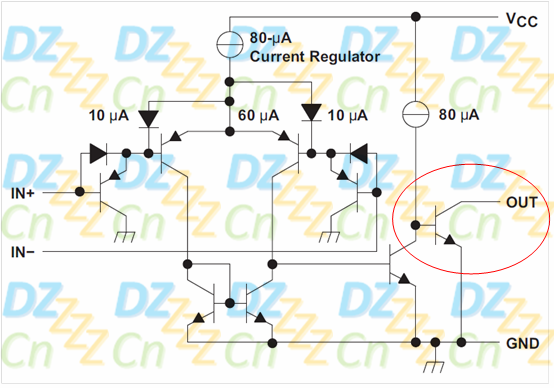

大多數比較器芯片的輸出都是OD/OC輸出結構,如下圖所示(來自TI比較器LM393數據手冊):

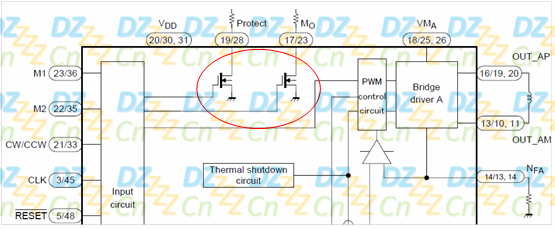

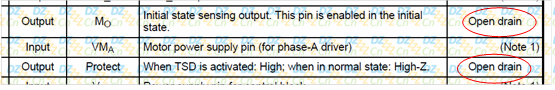

很多芯片或模塊向外反饋系統狀態的信號引腳也是這種結構,這樣用戶就可以根據電路系統實際需要將電平上拉到對應的電源電壓VCC,就可以省略電平轉換了,如下圖所示(來自東芝步進電機控制芯片TB6560數據手冊):

I2C(Inter Integrated Circuit,內部集成電路)總線也是典型的OD輸出結構的應用,如下圖所示:

其中,SCL與SDA都是OD輸出結構輸出,這樣的好處是可以作為雙向數據總線(也稱“線或Wire-OR”功能)。

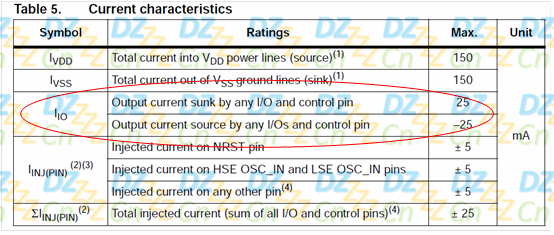

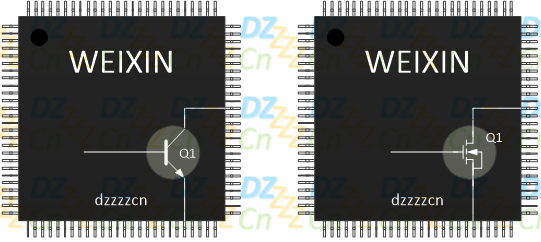

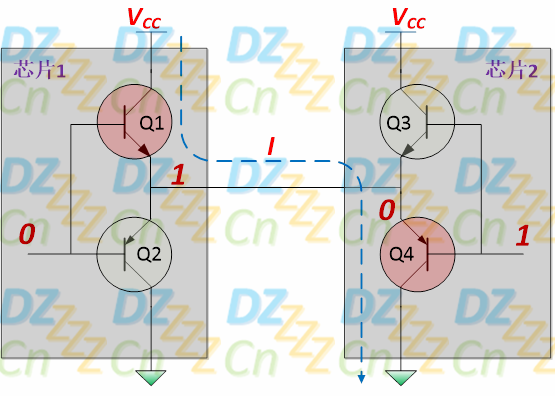

如果芯片引腳使用之前描述的推挽結構,則兩個或多個芯片的引腳連接時將如下圖所示:

假設如上圖所示芯片的輸出分別為0與1,則兩者直接相互連接后,會有非常大的電流自電源VCC經Q1與Q4到公共地,雖然大多數情況下不至于燒芯片,但也會引起很大的功率消耗,同時也會導致數據沖突(芯片1總會試圖將數據線拉高,而芯片2則會試圖將數據線拉低,我們稱之為數據沖突或總線沖突,表示雙方都在搶占總線)

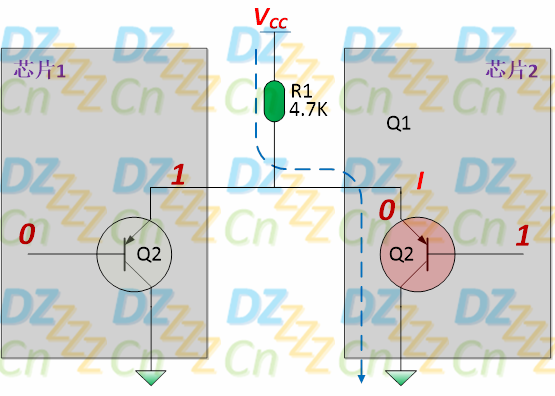

如果使用OC/OD輸出結構,則相應的電路如下圖所示:

此時,無論兩個芯片的引腳輸出什么狀態,都不會引起數據沖突,配合各自芯片內部的數據識別電路及仲裁系統,雙方都可以主動給另一方發送信息,也就是說,任何一方都可以將信號線拉高或拉低,而不會影響起數據沖突。

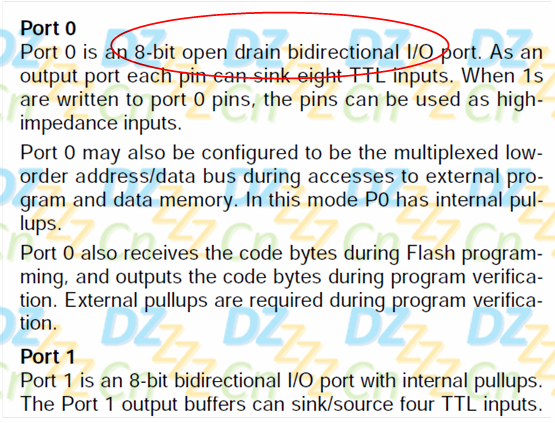

我們所熟悉的51單片機P0口也是OD結構,如下圖所示(來自ATMEL單片機AT89C51數據手冊):

這樣我們可以使用同一個P0口,再配合多個片選信號即可訪問多個外掛的存儲芯片。

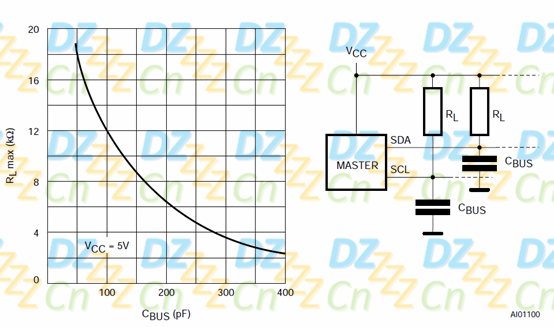

前面所述上拉電阻的阻值對輸入引腳引起的功耗同樣適用于輸出拉電阻,因此拉電阻不宜太小,但在輸出信號速度比較快的電路下,拉電阻也不宜太大,如下圖所示為I2C總線上拉電阻的參考最大值(來自ST存儲芯片 AT24C02數據手冊)。

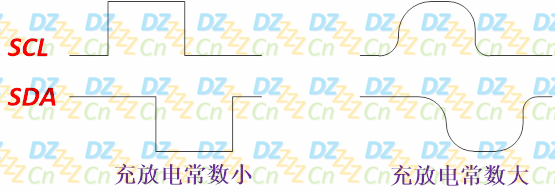

在總線上總會有些雜散電容CBUS,這些電容與上拉電阻RL形成了一個RC充放電電路,上拉電阻越大則充放電常數越大,這樣會把原先比較陡峭的數據邊沿變得平緩,如下圖所示:

嚴重的情況下將導致數據無法正常識別,這樣我們只能進一步優化電路參路,或降低通訊的速率。

原文標題:上拉電阻與下拉電阻詳解

文章出處:【微信公眾號:玩轉單片機】歡迎添加關注!文章轉載請注明出處。

責任編輯:haq

-

芯片

+關注

關注

463文章

54010瀏覽量

466017 -

電阻

+關注

關注

88文章

5781瀏覽量

179520 -

電流

+關注

關注

40文章

7212瀏覽量

141205

原文標題:上拉電阻與下拉電阻詳解

文章出處:【微信號:mcu168,微信公眾號:硬件攻城獅】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

用這種方法來估測CH552的上拉電阻可以嗎?

MOS管加下拉電阻的原因是什么?

一文讀懂貼片電阻:基礎認知、結構、工藝流程與特性分類

CYBT-343026-01與主機MCU連接時,I2S或UART接口是否需要上拉電阻?

浮思特 | 電子電路下拉電阻詳解:原理、計算與應用指南

CYUSB3065 (CX3) GPIO 所有輸出都是推挽還是開漏? 需要配置外部上拉/下拉電阻嗎?

嵌入式硬件雜談:推挽、開漏、高阻態、上拉電阻

一文讓你讀懂上拉電阻與下拉電阻

一文讓你讀懂上拉電阻與下拉電阻

評論