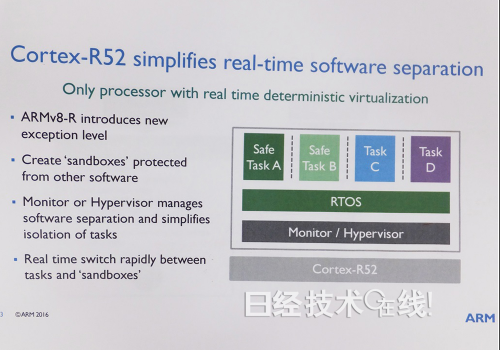

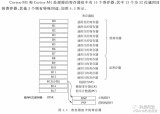

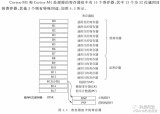

英國ARM公司2016年9月20日(當地時間)發布了瞄準自動駕駛汽車、醫療及工業機器人等領域、可用于實時處理的CPU內核“Cortex-R52”。ARM日本公司于9月21日面向日本的新聞媒體舉行

2016-09-29 10:12:51 3153

3153

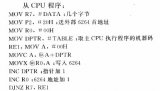

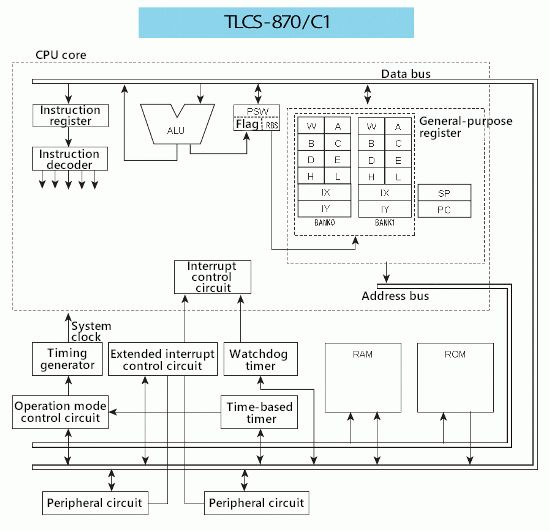

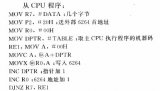

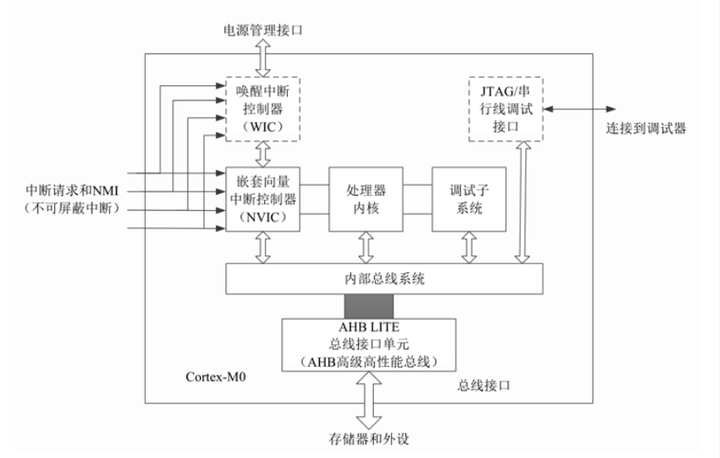

上一節的芝識課堂中我們介紹了微控制器的CPU部分功能單元和基本指令執行的知識,今天我們繼續以東芝的TLCS-870/C1內核作為示例,跟大家一起認識CPU配置的另一個關鍵環節——“中斷處理”。Continue

2022-07-18 10:41:11 1364

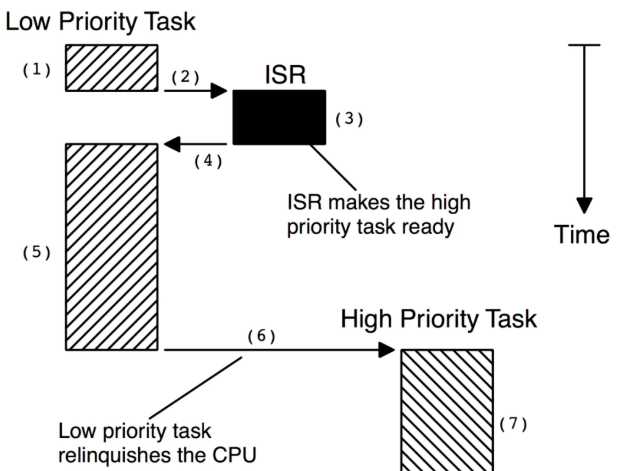

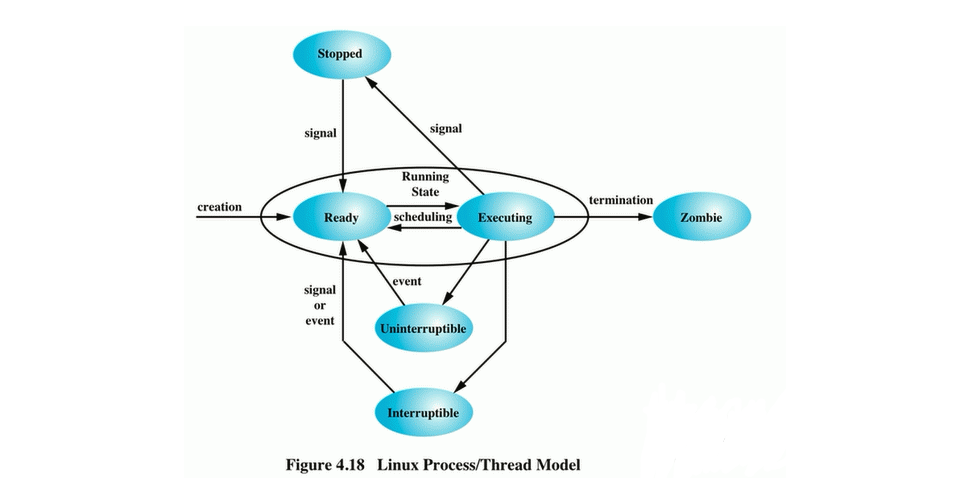

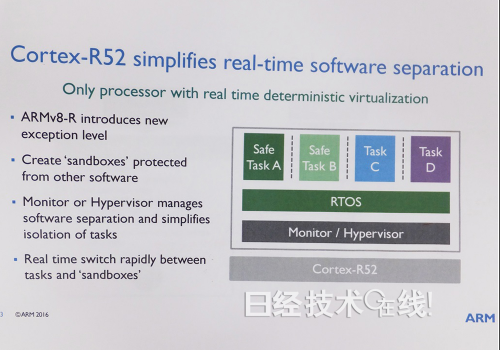

1364 非搶占式內核 非搶占式內核要求每個任務(線程)都做一些事情來明確放棄對 CPU 的控制,為了保持多任務并發的錯覺,必須要有這一步操作。 非搶占式調度也稱為協作多任務,任務相互協作以共享 CPU,異步

2022-09-29 18:38:43 1876

1876

瑞薩電子今日宣布,推出基于64位RISC-V CPU內核的RZ/Five通用微處理器(MPU)——RZ/Five采用Andes AX45MP,基于RISC-V CPU指令集架構(ISA),增強了瑞薩現有基于Arm? CPU內核的MPU陣容,擴充了客戶的選擇,并在產品開發過程中提供更大靈活性。

2022-03-01 13:54:21 1783

1783

大家對下面這段話:“單片機也稱微控制器,并不是所說的CPU,但它是CPU控制的。所說的片內外設就是指cpu控制的模塊,如定時器、串口等,這個cpu就是微控制器的內核,根據不同內核也有不同型號”中

2014-07-12 00:36:27

THERMAL PAD CPU 1.75" X 1.75"

2024-03-14 20:50:16

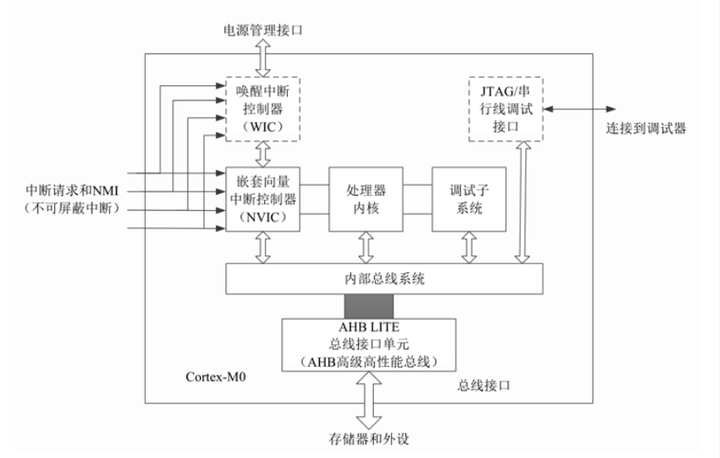

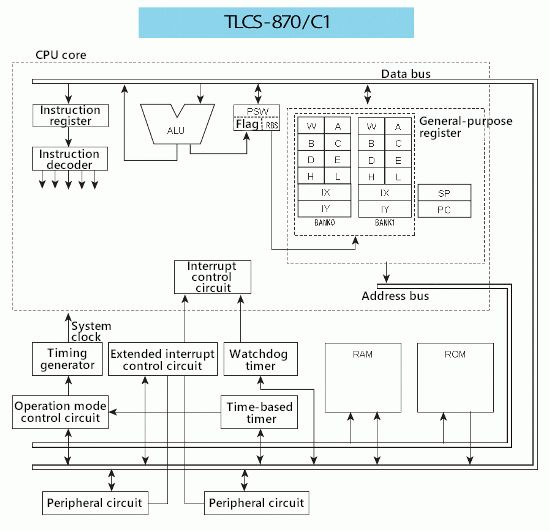

嵌入式之Cortex-M架構CPU內核寄存器及處理模式學習筆記

2021-12-15 06:13:09

CPU是什么?CPU主要由哪幾部分構成?CPU的內部處理過程是怎樣的?

2021-10-19 09:21:03

■ 內核CPU― 32位ARM Cortex-M4 內核+ FPU,單周期硬件乘除法指令,支持DSP指令和MPU― 內置8KB 指令Cache緩存,支持Flash加速單元執行程序 0 等待― 最高

2021-08-20 06:32:56

理想電壓源的特點有哪些?理想電壓源與理想電流源有何區別?

2021-10-14 07:10:37

主系統由 32 位多層 AHB 總線矩陣構成,可實現以下部分的互連:● 八條主控總線:— Cortex?-M4F 內核 I 總線、D 總線和 S 總線— DMA1 存儲器總線— DMA2 存儲器總線

2021-08-05 07:51:29

CJ2M-CPU11 - SYSMAC CJ-series CJ2M CPU Units - Omron Electronics LLC

2022-11-04 17:22:44

OMRON INDUSTRIAL AUTOMATION - CJ2M-CPU11.1 - CPU UNIT, 5KSTEPS, 0.5A, 5VDC

2024-06-21 01:51:33

OMRON INDUSTRIAL AUTOMATION - CJ2M-CPU32.1 - CPU UNIT, 10KSTEPS, 0.7A, 5VDC

2024-06-21 01:50:08

關于內核學習我建議不要上來就讀內核而是先了解內核的構成和特性,然后通過思考發現疑問這時再去讀內核源碼。即先了解概貌在讀局部細節。而且內核分成好多部分,不要只是按照順序去讀,應該針對某一部分比如內存管理或進程管理橫向讀幾本書,這樣可以理解很全面。

2019-07-24 07:09:16

INTEL CPU 志強E5 V4,Linux內核版本3.10.0-514.26.2.el7.x86_64及以上平臺下,PCI寄存器操作,僅可寫,讀操作引起內核崩潰,各位大牛有誰知道什么原因,謝謝!(PS: 降低內核版本或更換E5 V3 ,均可解決問題)

2017-09-07 13:22:47

s5pv210是三星公司推出的32位RISC微處理器,其CPU采用的是ARM Cortex-A8內核,基于ARMv7架構,這里的內核和架構是什么意思???

2015-03-25 12:09:45

arm處理器復位cpu后先進入管理模式,然后內核是怎樣切換模式的,在程序中好像無法體現出來。

2022-11-01 15:16:49

z80內核是什么cpu

2023-09-20 07:26:32

你好,正如我們所知,每個CPU可以在睡眠中獨立于其他CPU的狀態。如果兩個內核處于不同的功率模式,那么這意味著相同的外設對不同的內核表現出不同的性能嗎? 以上來自于百度翻譯 以下為原文Hi

2018-12-14 16:04:32

中,CPU、RAM、ROM、I/O這些都是單獨的芯片,然后這些芯片被安裝在一個主板上,這樣就構成了我們的PC主板,進而組裝成電腦,而單片機只是將這所有的集中在了一個芯片上而已。2、什么是ARM芯片?凡是采用ARM內核的芯片(或者凡是采用ARM內核的CPU)都是ARM芯片3、什么是ARM內核?所謂內核,就是CP

2022-01-13 06:55:55

內核:基于平頭哥半導體 (T-HEAD Semiconductor) CPU E801 內核開發(原生:中天微CK801)RISC 精簡指令結構64K Flash ,獨立2Kbytes Data

2021-12-09 06:20:46

請問下:對市面上的ARM SOC芯片,如何可靠識別ARM SOC內所使用的ARM CPU內核IP型號?1、對市面上的ARM SOC芯片,如何可靠識別ARM SOC內所使用的ARM CPU內核IP

2022-08-01 14:14:45

如何對RK3399 CPU arm64的內核進行配置?

2022-02-16 06:20:18

問題:我有個 Linux 進程運行在多核處理器系統上。怎樣才能找出哪個 CPU 內核正在運行該進程?當你在 [url=]多核 NUMA 處理器上[/url]運行需要較高性能的 HPC(高性能計算

2016-10-24 15:30:42

我需要保留一個 CPU 核心用于關鍵中斷和 WIFI 處理。當我使用 PSRAM 時,訪問 PSRAM 的 CPU 核心將停止,直到 PSRAM 數據傳輸結束。如何配置 ESP-IDF 只為一個 CPU 內核分配 PSRAM,這樣另一個 CPU 內核就不會因為訪問 PSRAM 而停滯?

2023-03-02 06:54:04

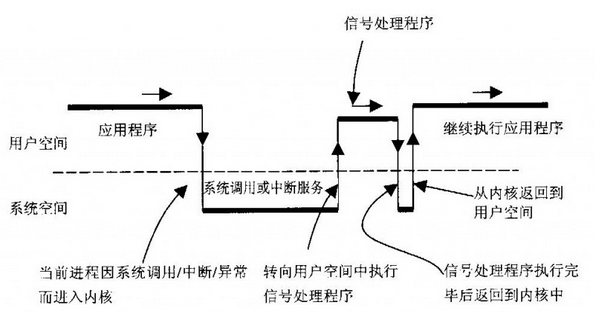

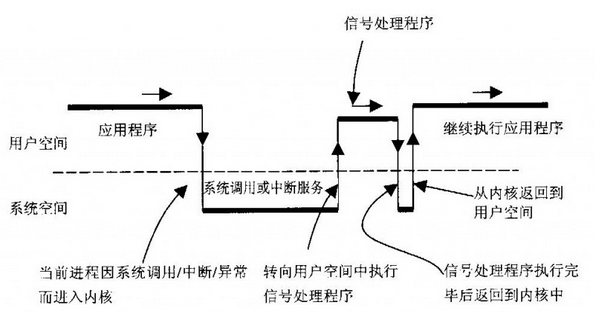

一. Linux內核簡介1. 系統架構1.1 Linux系統架構Linux系統由用戶空間和內核空間兩部分構成,用戶空間包括用戶應用程序和C庫,而內核空間包含了系統調用接口、狹義上的內核以及體系結構

2021-12-20 07:23:39

計算機硬件系統由哪幾部分構成?編程語言的作用及與操作系統和硬件的關系是什么?請問CPU與寄存器,內核態與用戶態及如何切換?

2021-10-25 06:31:50

三菱PLC Q基本模式CPU硬件設計保養:1 概要1.1 特點2 系統構成2.1 系統構成2.1.1 Q00JCPU2.1.2 Q00/Q01CPU2.1.3 GX Developer的構成2.2 使用時的注意事項2.3 功能版本的確認方

2008-11-21 13:33:43 73

73 本文主要講述的是便攜式CPU內核的供電問題。

2009-04-30 10:10:31 25

25 提出一種基于51 內核網絡單片機的嵌入式遠程監控系統方案,介紹以DS80C400單片機為核心的系統硬件構成和基于TINI運行環境的應用程序設計方法。該方案可以實現串口、CAN總線等輕

2009-05-18 14:25:30 19

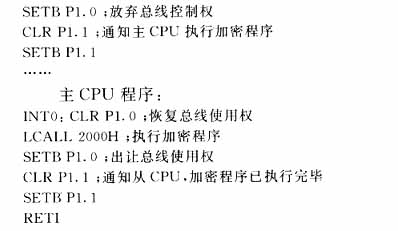

19 介紹了單片機雙CPU構成復雜系統的電路以及該系統的幾種應用實例。 關鍵詞:單片機,雙CPU,總線,數據存儲器

2009-05-06 20:44:22 827

827

TMS320C31和80C196雙CPU構成的高速實時控制系統

介紹了采用TMS320C31和80C196雙CPU構成的高速實時控制系統的基本構成,給出了TMS320C31、80C196與雙口RAM IDT7140

2009-12-08 14:21:54 1781

1781

什么是CPU核心

核心(Die)又稱為內核,是CPU最重要的組成部分

2009-12-17 10:57:07 1642

1642 雙核cpu

雙核就是2個核心,核心(Die)又稱為內核,是CPU最重要

2009-12-17 11:01:49 1679

1679 CPU核心技術 核心(Die)又稱為內核,是CPU最重要的組

2009-12-18 09:54:16 1723

1723 CPU核心類型 核心(Die)又稱為內核,是CPU

2009-12-24 09:58:03 803

803 CPU內核結構解析 CPU內核主要分為兩部分:運算器和控制器。

(一) 運算器

1、 算

2010-04-15 16:13:27 1628

1628 美普思科技公司(MIPS Technologies, Inc)宣布,龍芯中科技術有限公司已獲得 MIPS32和 MIPS64架構授權,將持續開發 MIPS-Based龍芯 CPU 內核。

2011-08-24 09:21:04 1863

1863 由KIA7033構成的單片機復位電路,可手動復位,效果理想。

2012-01-04 10:50:04 2617

2617

多任務系統中,內核負責管理各個任務,或者說為每個任務分配CPU時間,并且負責任務之間的通訊。內核提供的基本服務是任務切換。

2012-05-11 10:41:03 2004

2004 Imagination在近日更新了MIPS旗艦級的Aptiv 內核現有的產品組合,并且宣布在今年稍晚點時候推出包括32位和64位內核的全系列新款MIPS CPU,新的 MIPS Series5

2013-07-08 14:59:18 10739

10739 ‘Warrior P-class’ CPU,這是邁向高性能 MIPS CPU IP 內核的重大進展。新款MIPS P5600 內核可提供領先業界的 32 位性能,內核芯片面積比競爭對手小 30% ,提供較同類領先的低功耗特性,MIPS P5600 內核成為各種移動、消費和嵌入式應用的理想選擇。

2013-10-22 16:29:28 1095

1095 今年三星的半導體部門已經開始嘗試一些大的飛躍,其運用于Galaxy S7旗艦的Exynos 8890處理器,首次采用了自主定制的CPU內核M1。

2016-11-25 14:50:10 1021

1021 今年三星的半導體部門已經開始嘗試一些大的飛躍,其運用于Galaxy S7旗艦的Exynos 8890處理器,首次采用了自主定制的CPU內核M1。

2016-11-28 13:57:07 681

681 發布了多款新產品,表現出了大力發展IoT市場的勃勃雄心。除了CPU內核、安全技術、互聯IP內核、無線通信IP內核、IoT子系統、POP等SoC設計用新產品之外,ARM還宣布提供SaaS。

2016-12-13 15:29:53 1941

1941 1 引言 本文分析了Windows 系統的進程調度機制,并設計了一種基于Windows 操作系統內核驅動的多核CPU 線程管理方法,實現了一個基于Windows 內核驅動的線程管理服務系統,它能

2017-10-31 11:02:46 0

0 如果讓內核定期對設備進行輪詢,以便處理設備,那會做很多無用功,因為外設的處理速度一般慢于CPU,而CPU不能一直等待外部事件。所以能讓設備在需要內核時主動通知內核,會是一個聰明的方式,這便是中斷。

2017-11-14 15:48:05 3393

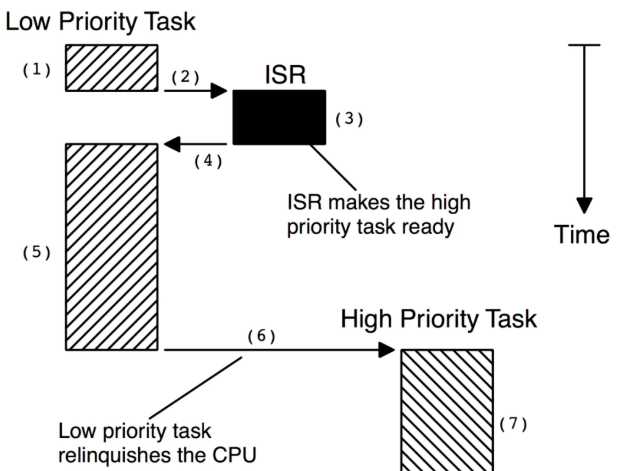

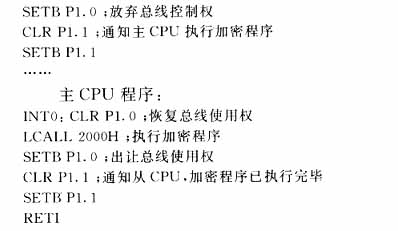

3393 等缺點。在這種情況下,往往采取雙CPU或多CPU的設計方案,以彌補其不足。但是由于單片微機不像通用的微機系統具有其它總線主控設備向CPU請求總線使用申請信號輸入端,以及CPU對系統中其他總線主控設備請求使用權的應答信號

2017-12-01 11:55:47 864

864

的CPU》中看出。這個受到中科院院士李國杰鼓舞而走上“龍芯”研發之路的博士,以一種理想主義的文字敘述了龍芯1號的誕生過程。

他說,當初,李國杰在所里倡導中國CPU

2017-12-04 03:01:02 372

372 算法的準入條件。在此基礎上搭建了基于GPP的LTE系統實驗平臺,通過實驗比較了基于兩種內核調度算法的通信系統在時間響應、CPU使用率等方面的性能。結果表明,基于DEADLINE算法的通信系統時間響應性能優于FIFO,提高了28. 38%,同時CPU使用率提高了36. 53%。實驗結果對基于不同場景搭建軟

2018-02-02 15:59:28 0

0 核心又稱為內核,是CPU最重要的組成部分。CPU中心那塊隆起的芯片就是核心,是由單晶硅以一定的生產工藝制造出來的,CPU所有的計算、接受/存儲命令、處理數據都由核心執行。各種CPU核心都具有固定的邏輯結構。

2018-02-12 10:42:26 39344

39344

Architecture, ISA)。本節概述基于 M4K 處理器內核的 PIC32 系列單片機的 CPU 特性和系統架構。

2018-06-06 12:29:00 19

19 PIC32 系列參考手冊—第50章 采用MIPS32? microAptiv?和M-Class內核的器件的CPU

2018-05-25 17:29:32 6

6 CPU的主頻,即CPU內核工作的時鐘頻率(CPU Clock Speed)。通常所說的某某CPU是多少兆赫的,而這個多少兆赫就是“CPU的主頻”。

2018-09-10 11:17:45 242962

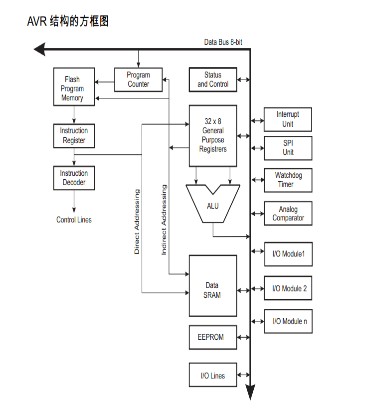

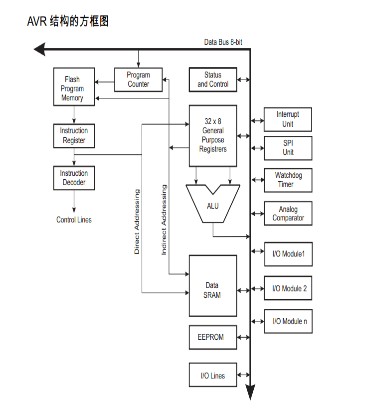

242962 AVR采用了Harvard結構,具有獨立的數據和程序總線,CPU在執行一條指令的同時,就將PC中指定的下一條指令取出,構成了一級流水線運行方式,實現了一個時鐘周期執行一條指令,數據吞吐量高達1MIPS/MHz。

2018-10-17 16:39:35 5293

5293

讓我們考慮一些似乎是兼容處理器技術平滑發展的例子,這些技術將MCU產品線推向微處理器領域。飛思卡爾提供基于ARM Cortex-M4內核的Kinetis MCU系列,包括K10,K20,K30

2019-01-25 08:56:00 4580

4580

內核最初啟動的時候,沒有啟動MMU,這樣導致CPU只認物理地址(又稱運行地址),不認虛擬地址(又稱鏈接地址)。

2019-05-15 11:51:29 560

560

服務器,是雙核又CPU,等于是有4個內核,每個內核的負載為1的話,總負載為4。這就是說,如果我那臺服務器的CPU負載長期保持在4左右,還可以接受。但是每個內核的負載為1,并不能算是一種理想狀態!這意味著我們

2019-04-02 14:31:57 660

660 2019年就要正式量產了,6月份就會發布10nm Ice Lake處理器,今天Intel也正式宣布了第二代10nm工藝的處理器Tiger Lake,將會使用全新的CPU內核及GPU內核。

2019-05-09 15:19:03 2265

2265 讓我們快速描述一下CPU。CPU在設備上運行OS和各種應用程序,處理數據并提供輸出。現在的CPU通常包含多個處理器(內核)。比如雙核,四核,八核等。

2020-02-24 20:44:13 3663

3663 CPU的主頻,即CPU內核工作的時鐘頻率(CPU Clock Speed)。通常所說的某某CPU是多少兆赫的,而這個多少兆赫就是CPU的主頻。很多人認為CPU的主頻就是其運行速度,其實不然。CPU

2020-05-12 16:15:25 3240

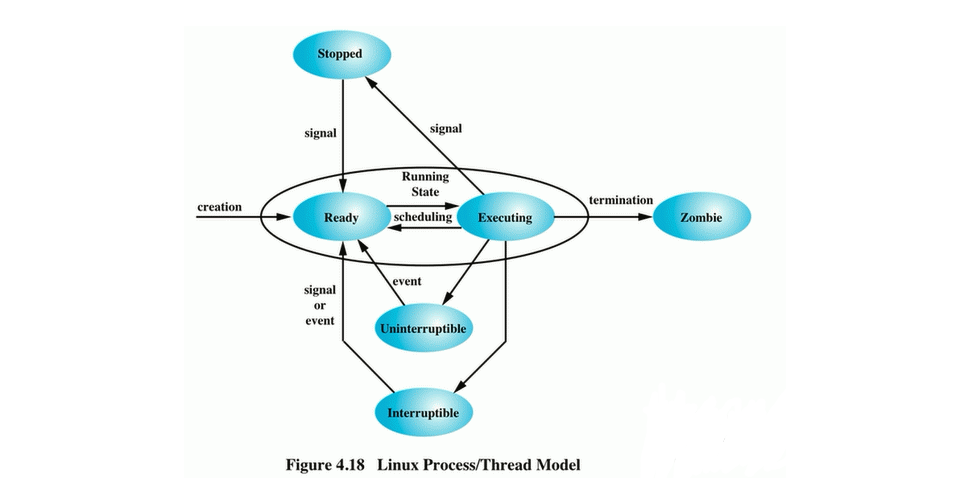

3240 首先,Linux整體的架構如圖: 再來看Linux內核架構, 內核由五個主要子系統組成: Process Scheduler : 進程調度(SCHED)負責控制對CPU的進程訪問。調度程序執行

2020-05-20 09:28:31 1105

1105 編譯嵌入式Linux內核都是通過make的不同命令來實現的,它的執行配置文件是Makefile。Linux內核中不同的目錄結構里都有相應的Makefile,而不同的Makefile又通過彼此之間的依賴關系構成統一的整體,共同完成建立依存關系、建立內核等功能。

2020-06-19 09:30:24 3270

3270

保持ASIL-B功能安全的拆分模式仍然需要定期檢查內核以確保其正常工作,這使它們暫時不可用。問題在于DSU級別(動態共享單元– L3緩存),要對其進行檢查將使整個CPU群集不可用,并且對系統的性能影響更大。

2020-09-30 15:13:12 12033

12033 ARM宣布,從2022年開始,其所有“大型” CPU內核將僅采用64位。但這為ARM將繼續為使用其“ LITTLE” CPU內核的新型節能芯片提供32位支持提供了可能性。

2020-10-12 10:50:40 3286

3286 本篇有相當的難度,涉及用戶棧和內核棧的兩輪切換,CPU四次換棧,寄存器改值,將圍繞下圖來說明.? 解讀 為本篇理解方便,把圖做簡化標簽說明: user:用戶空間 kernel:內核空間 source

2021-04-28 16:56:17 2194

2194

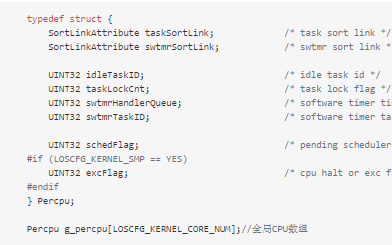

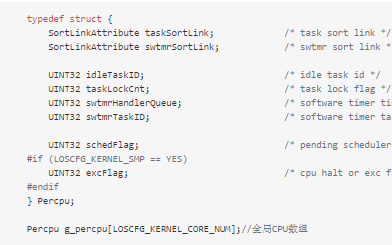

這是內核對CPU的描述,主要是兩個排序鏈表,一個是任務的排序,一個是定時器的排序.什么意思? 在

2021-04-25 09:24:00 2216

2216

本篇說清楚CPU cpu是負責執行指令的,誰能給它指令?是線程(也叫任務), 任務是內核的調度單元,調度到哪個任務CPU就去執行哪個任務的指令. 要執行指令就要有個取指令的開始地址. 開始地址就是

2021-03-15 14:37:06 2690

2690 目錄對 Linux Kernel來說,意義非常有限,導致內核中充斥這大量板級相關代碼和大量# i fdef形式的代碼Linus Torvalds認為ARM很多的代碼都是垃圾,代碼里面有若干對內核沒有意義的 table,每次 merge中,ARM的代碼變化大約占整個ARCH目錄的60%,大部分變化都是板級相關代碼。

2020-11-19 16:53:00 19

19 適用于工業和嵌入式 PC 的 Intel Core i7 (Arrandale) 48A CPU 內核參考設計;此兩相 48A 設計面向采用 Intel Core i7 處理器的嵌入式和工業 PC,在小面積內提供緊湊 CPU 內核電壓調節和出眾熱性能

2020-11-24 08:00:00 2

2 設計,俗稱CPU內核,例如Zilog的Z80內核、Intel的8051內核、Microchip的PIC16、18、dsPIC、PIC32內核、Motorola的68000內核、Atmel的AVR...

2021-11-15 13:06:03 37

37 先進半導體解決方案的主要供應商瑞薩電子公司(TSE:6723)今天宣布推出圍繞 64 位 RISC-V CPU 內核構建的 RZ/5 個通用微處理器單元 (MPU)。RZ/Five 采用

2022-03-01 16:52:22 5129

5129 非搶占式內核的優點之一是中斷延遲更低,在任務級別,非搶占內核也可以使用不可重入函數。每個任務都可以使用不可重入函數,而不必擔心被另一個任務破壞。這是因為每個任務都可以在放棄 CPU 之前運行到完成。但是,不應允許不可重入函數放棄對 CPU 的控制。

2022-06-02 14:35:30 1808

1808 ,比如:cache 等,這些部分會在后面進行補充。CPU 拓撲除了描述 CPU 的組成關系外,還為內核的調度器提供服務,從而提供更好的性能。

2022-08-29 11:02:22 5736

5736 Linux內核由七個部分構成,每個不同的部分又有多個內核模塊組成。

2022-10-13 15:44:45 1541

1541 CPU由運算器、控制器和寄存器及實現它們之間聯系的數據、控制及狀態的總線 構成。CPU的能力高低直接影響了整個電腦的運行速度。

2023-02-14 15:03:07 8009

8009 /rx-32-bit-performance-efficiency-mcus/rx-features ◆ RX內核比較 特性1:延續前代產品優勢的獨創CPU RX內核兼具CISC和RISC的優勢 將CISC的可變字節長度指令與RISC的通用寄存器機、架構和流水線相結合。RX CPU內核融

2023-02-17 13:45:02 2816

2816 PLC的構成:由微處理器(CPU)、存儲器(ROM,RAM)、輸入/輸出單元(I/O)、編程器和電源構成。

2023-03-03 15:49:18 14876

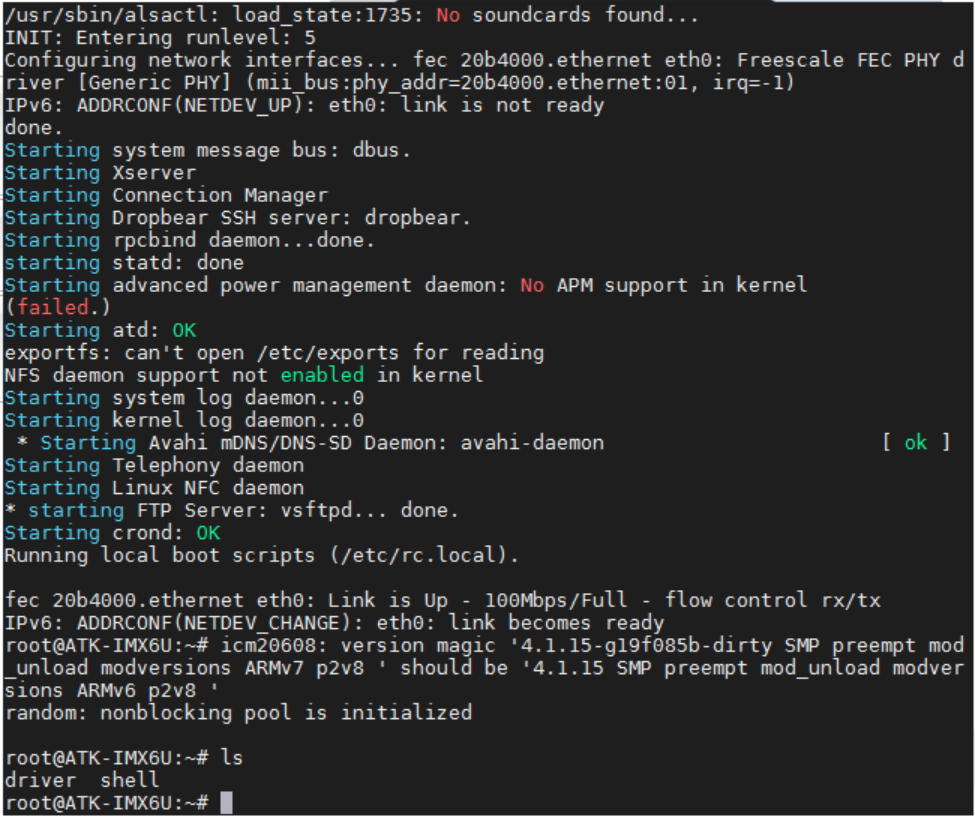

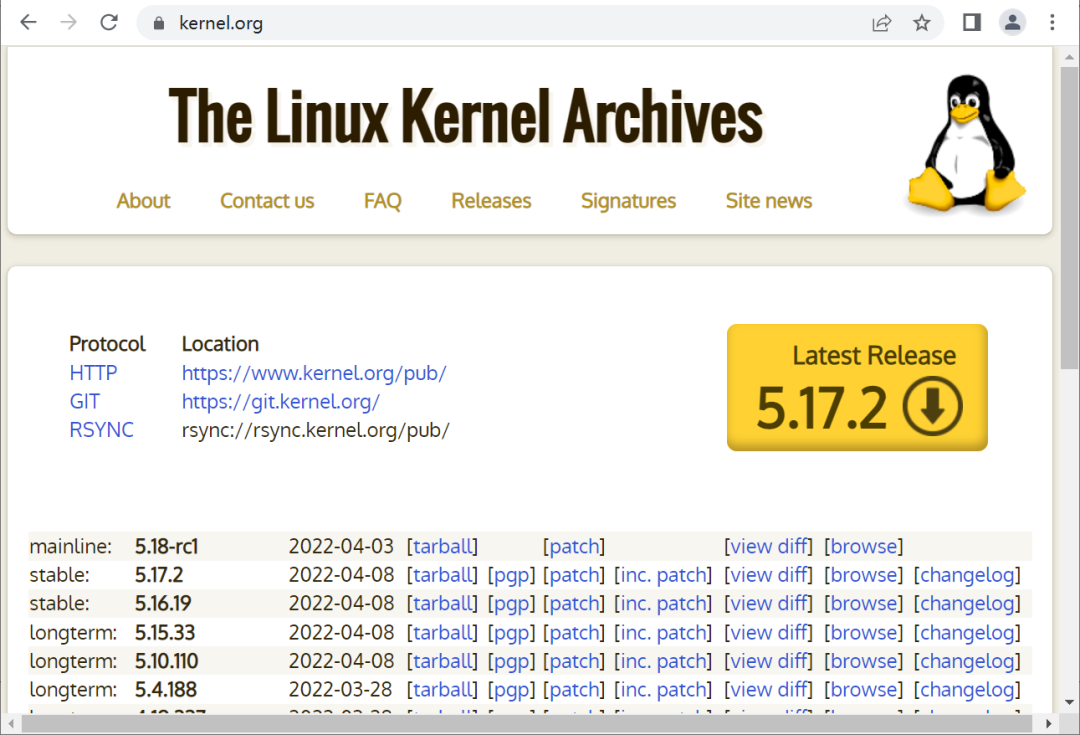

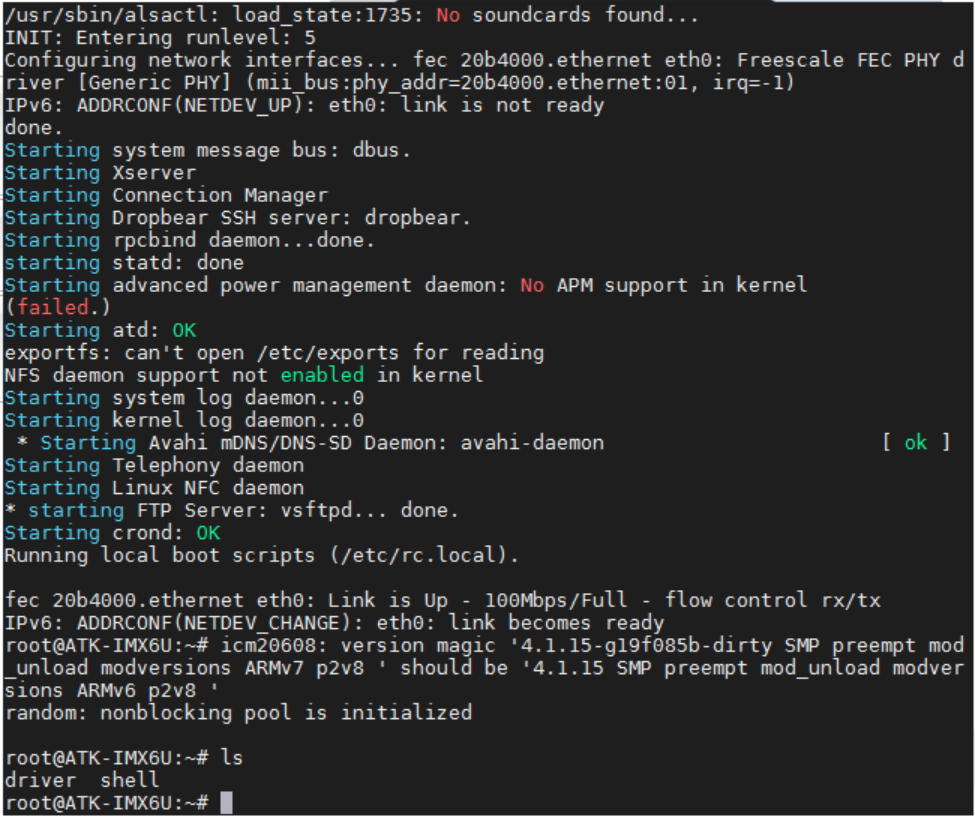

14876 半導體廠商會從 Linux內核官網下載某個版本,將其移植到自己的 CPU上,測試成功后就會將其開放給該半導體廠商的 CPU開發者。開發者下載其提供的 Linux內核,然后將其移植到自己的產品上。

2023-04-19 11:20:32 2273

2273

一般半導體廠商會從 Linux內核官網下載某個版本,將其移植到自己的 CPU上,測試成功后就會將其開放給該半導體廠商的 CPU開發者。開發者下載其提供的 Linux內核,然后將其移植到自己的產品上。

2023-04-19 11:20:56 1808

1808

初步用戶手冊 帶 32 位 RISC CPU 內核的 ERTEC 400 增強型實時以太網控制器用戶手冊

2023-04-28 20:12:09 1

1 芯片內核又稱CPU內核,它是CPU中間的核心芯片,是CPU最重要的組成部分。由單晶硅制成,CPU所有的計算、接受/存儲命令、處理數據都由核心執行。各種CPU核心都具有固定的邏輯結構,一級緩存

2023-08-02 15:21:12 2468

2468

【微控制器基礎】——CPU內核與整體配置(上)

2023-10-17 17:19:38 1769

1769

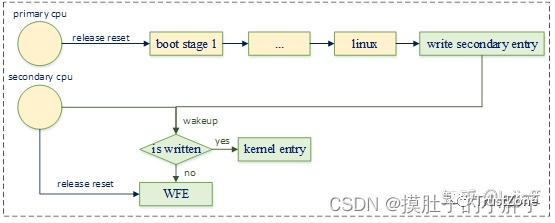

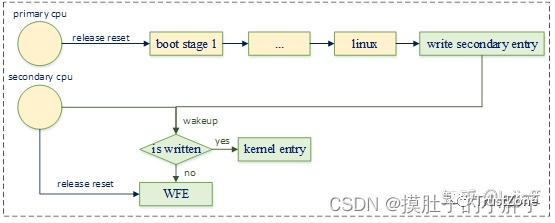

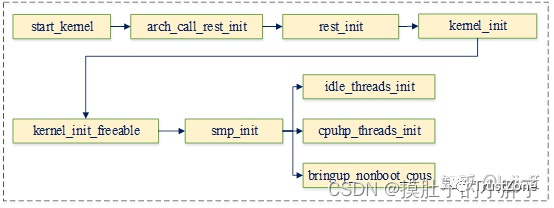

spin-table spin-table啟動流程的示意圖如下: 芯片上電后primary cpu開始執行啟動流程,而secondary cpu則將自身設置為WFE睡眠狀態,并且為內核準備了一塊內存

2023-12-05 15:27:21 2030

2030

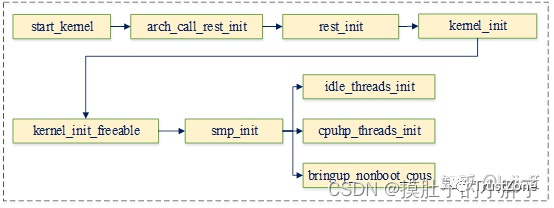

啟動secondary cpu 內核在啟動secondary cpu之前當然需要為其準備好執行環境,因為內核中cpu最終都將由調度器管理,故此時調度子系統應該要初始化完成。 同時cpu啟動完成轉交

2023-12-05 15:46:51 1235

1235

cpu_ops接口 驅動初始化完成后,cpu的cpu_ops就可以調用這些回調實現psci功能的調用。如下所示,當devicetree中cpu的enable-method設置為psci時,該cpu

2023-12-05 17:25:11 1418

1418 新聞快訊 全球半導體解決方案供應商瑞薩電子(TSE:6723)宣布成功設計、測試并推出基于開放標準RISC-V指令集架構(ISA)的32位CPU內核。瑞薩作為業內首個為32位通用RISC-V市場獨立研發CPU內核的廠商,面向物聯網、消費電子、醫療保健和工業系統打造了一個開放、靈活的平臺。

2023-12-08 11:40:02 1053

1053 在計算市場持續迎來變革的背景下,Arm公司發布了其最新一代Neoverse CPU內核設計,分別為Neoverse V3(代號Poseidon)和N3(代號Hermes),兩款內核將為服務器、云計算和基礎設施領域帶來更大規模和更快速度的計算能力。

2024-02-27 09:27:24 2388

2388

電子發燒友網站提供《用于高頻 CPU 內核功率的同步降壓 FET 驅動器TPS51604數據表.pdf》資料免費下載

2024-03-13 11:10:03 0

0 全球半導體領軍企業瑞薩電子宣布,該公司已率先在業界推出了一款基于內部自研CPU內核的通用32位RISC-V微控制器(MCU)——R9A02G021。盡管近年來,多家MCU供應商紛紛加入投資聯盟,共同

2024-03-29 10:05:21 1247

1247 X-Silicon 的芯片與其他架構不同,其設計將 CPU 和 GPU 的功能整合到單核架構中。這與英特爾和 AMD 的典型設計不同,前者有獨立的 CPU 內核和 GPU 內核。

2024-04-08 11:34:44 1346

1346

內核寄存器與外設寄存器: 內核寄存器與外設寄存器是完全不同的概念。內核寄存器是指 CPU 內部的寄存器,CPU處理所有指令數據需要用到這些寄存器保存處理數據。

2024-04-17 11:47:58 6648

6648

CPU(Central Processing Unit),是一臺計算機的運算核心和控制核心。CPU由運算器、控制器和寄存器及實現它們之間聯系的數據、控制及狀態的總線構成。

2024-04-22 15:05:23 2369

2369 Linux內核中是如何分配出頁面的,如果我們站在CPU的角度去看這個問題,CPU能分配出來的頁面是以物理頁面為單位的。也就是我們計算機中常講的分頁機制。本文就看下Linux內核是如何管理,釋放和分配這些物理頁面的。

2024-08-07 15:51:11 1021

1021

晶體管作為CPU(中央處理器)的基本構成單元,對CPU的性能有著至關重要的影響。

2024-09-13 17:22:49 2697

2697

電子發燒友App

電子發燒友App

評論