賦值何時使用阻塞賦值才能設(shè)計出符合要求的電路。 他們也不完全明白在電路結(jié)構(gòu)的設(shè)計中,即可綜合風(fēng)格的Verilog模塊的設(shè)計中,究竟為什么還要用非阻塞賦值,以及符合IEEE 標(biāo)準(zhǔn)的Verilog 仿真器究竟如何來處理非阻塞賦值的仿真。 本小節(jié)的目的是盡可能地把阻塞和非阻

2021-08-17 16:18:17 7048

7048 Verilog是一種硬件描述語言,用于描述數(shù)字電路的結(jié)構(gòu)和行為。與傳統(tǒng)的編程語言不同,Verilog更加注重電路的行為和時序特性。

2023-08-01 09:00:07 7038

7038

Verilog HDL語言有什么優(yōu)越性Verilog HDL語言在FPGA/CPLD開發(fā)中的應(yīng)用

2021-04-23 07:02:03

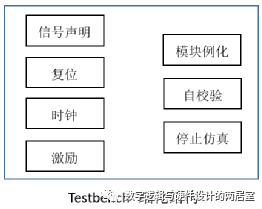

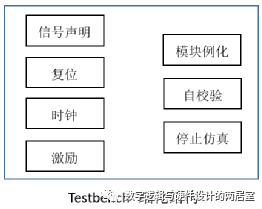

:① 邏輯功能正確,②可快速仿真,③ 綜合結(jié)果最優(yōu)(如果是hardware model),④可讀性較好。2. 范圍本規(guī)范涉及Verilog HDL編碼風(fēng)格,編碼中應(yīng)注意的問題, Testbench的編碼

2017-12-08 14:36:30

的復(fù)雜性可以介于簡單的門和完整的電子數(shù)字系統(tǒng)之間。數(shù)字系統(tǒng)能夠按層次描述,并可在相同描述中顯式地進(jìn)行時序建模。Verilog HDL 語言具有下述描述能力:設(shè)計的行為特性、設(shè)計的數(shù)據(jù)流特性、設(shè)計的結(jié)構(gòu)

2020-11-30 19:03:38

Verilog HDL的基礎(chǔ)教程.pdf 硬件描述語言 是硬件設(shè)計人員和電子設(shè)計自動化工具之間的界面其主要目的是用來編寫設(shè)計文件建立電子系統(tǒng)行為級的仿真模型即利用

2008-05-20 13:07:14

Verilog可綜合子集

2013-04-01 12:44:46

可綜合模型的結(jié)構(gòu)如果程序只用于仿真,那么幾乎所有的語法和編程語句都可以使用。但如果程序是用于硬件實現(xiàn),那么我們就必須保證程序的可綜合性,即所編寫的程序能被綜合器轉(zhuǎn)化為相應(yīng)的電路結(jié)構(gòu)。不可綜合的HDL

2012-10-20 08:10:13

1,在一個verilog程序里,如果循環(huán)是一個循環(huán)次數(shù)不可定的循環(huán),那么它能被綜合工具綜合嗎2,如果程序里有always @(clock)里面又嵌套了@(clock)這樣的控制事件,這個能被綜合嗎

2015-02-03 15:29:11

,若不是,則只能用于仿真),while, 建立可綜合模型的原則 要保證Verilog HDL賦值語句的可綜合性,在建模時應(yīng)注意以下要點: (1)不使用initial。 (2)不使用#10。 (3)不使

2015-01-05 19:42:44

,arrays,memories,repeat,task,while。建立可綜合模型的原則 要保證Verilog HDL賦值語句的可綜合性,在建模時應(yīng)注意以下要點: (1)不使用initial。 (2)不使

2012-02-27 15:01:27

verilog的仿真和綜合有什么區(qū)別,請具體一點?

2018-06-06 22:41:18

轉(zhuǎn)換成HDL代碼,跳過了中間的C語言改寫步驟12.常規(guī)從算法到硬件電路的開發(fā)過程:算法的開發(fā)C語言的功能描述并行結(jié)構(gòu)的C語言改寫verilog的改寫仿真、驗證、修正綜合、布局布線、投入實用13.C語言

2012-01-12 15:15:21

可綜合的Verilog語法和語義(劍橋大學(xué),影印)

2012-08-06 13:03:57

全球領(lǐng)先的設(shè)備軟件優(yōu)化(DSO)廠商風(fēng)河系統(tǒng)公司(Wind River)宣布推出Wind River Workbench On-Chip Debugging 3.1.1,將這套綜合性開發(fā)工具的支持

2019-08-28 08:14:28

apex20ke_atoms.v編譯到其中。2:在圖形界面中的Load Design對話框中裝入仿真設(shè)計時,在Verilog 標(biāo)簽下指定預(yù)編譯庫的完整路徑。(見下圖)邏輯綜合目前可用的FPGA綜合工具

2020-05-15 07:00:00

、固核與硬核:1.3Verilog HDL設(shè)計流程:注:Verilog HDL語法的兩個部分第一章Verilog基礎(chǔ)知識1.1Verilog HDL開發(fā)的優(yōu)勢:語法簡單,可綜合性與系統(tǒng)仿真性能強,支持

2022-03-22 10:26:00

:Verilog HDL程序設(shè)計語句和描述方式第四章:Verilog HDL數(shù)字邏輯電路設(shè)計方法第五章:仿真驗證與Testbench編寫第六章:Verilog HDL高級程序設(shè)計舉例第七章:數(shù)字集成電路設(shè)計流程(測試仿真、綜合)超級干貨,精選內(nèi)容不可錯過!

2021-03-30 14:31:41

我們以Imagination新發(fā)布的兩款內(nèi)核產(chǎn)品為例,來分析不同應(yīng)用市場對嵌入式AI的綜合性能指標(biāo)。

2021-01-14 06:53:15

肇慶學(xué)院光機(jī)電一體化綜合性實驗教學(xué)示范中心實驗教材之二十六計算機(jī)控制技術(shù)實 驗 教 程肇慶學(xué)院電子信息與機(jī)電工程學(xué)院編二00八年九月內(nèi)容簡介本書主要是基于清華大學(xué)出版社出版的由于海生先生所編著

2021-09-01 06:50:57

問題:用vhdl語言和Verilog語言和matlab協(xié)仿真同一個程序,在modelsim上跑出來的結(jié)果不一樣。導(dǎo)致時序有問題。網(wǎng)上查了很多資料沒有結(jié)果。(調(diào)用的.m函數(shù)一樣即輸入信號一樣)。例子

2015-04-28 09:12:50

功能仿真:可以驗證代碼的邏輯性,不加任何的時延信息。仿真工具為modelsim(組合邏輯和時序邏輯都可以功能仿真),modelsim不能綜合。在modelsim中添加相應(yīng)的激勵信號,調(diào)用

2016-08-23 16:57:06

數(shù)字集成電路設(shè)計入門--從HDL到版圖于敦山北大微電子學(xué)系?介紹Verilog HDL,內(nèi)容包括:–Verilog應(yīng)用–Verilog語言的構(gòu)成元素–結(jié)構(gòu)級描述及仿真–行為級描述及仿真–延時的特點

2012-08-03 00:23:48

`該資料對STM32微控制器作了詮釋和指導(dǎo),STM32的基礎(chǔ)實驗,進(jìn)階應(yīng)用,硬件描述和綜合性實驗的詳細(xì)資料概述包括了實物圖和原理圖。`

2018-09-04 14:35:45

描述語言,它主要應(yīng)用于數(shù)字電路和系統(tǒng)設(shè)計、數(shù)字電路和系統(tǒng)仿真等,即利用計算機(jī)和相關(guān)軟件對VERILOG HDL等硬件語言建模的復(fù)雜數(shù)字電路設(shè)計進(jìn)行仿真驗證,再利用綜合軟件將設(shè)計的數(shù)字電路自動綜合,以得到

2018-11-05 20:24:23

少部分才是用于電路設(shè)計,詳細(xì)可以參考本書的“可綜合邏輯設(shè)計”一節(jié)。Verilog中用于設(shè)計的語法,才是學(xué)習(xí)的重點。掌握好設(shè)計的語法,熟練應(yīng)用于各種復(fù)雜的項目,這是技能的核心。其他測試用的語法,需要

2018-10-08 15:19:23

大神,求51單片機(jī)綜合性編程題越多越好!

2013-11-04 16:24:05

語言標(biāo)準(zhǔn)的時候,并沒有考慮這些代碼如何用硬件來實現(xiàn)。換句話說,有些代碼寫起來簡單,實現(xiàn)起來卻可能非常復(fù)雜,或者幾乎不可能實現(xiàn)。三、HDL代碼的可綜合性現(xiàn)在回到最初的問題上。為什么諸如除法、循環(huán)之類

2019-03-27 07:00:00

在本篇里,我們討論 Verilog 語言的綜合問題,Verilog HDL (Hardware Description Language) 中文名為硬件描述語言,而不是硬件設(shè)計語言。這個名稱提醒我們

2021-07-29 07:42:25

粘土混砂機(jī)實驗(綜合性實驗)一、實驗內(nèi)容學(xué)生自行用實驗用混砂機(jī)所帶配件組裝成一種機(jī)型的混砂機(jī),并調(diào)整到所選定的工作參數(shù);確定型砂配方,在已

2009-05-14 23:49:33 0

0 T型結(jié)構(gòu)焊接變形與火焰矯正綜合性實驗一、實驗原理焊接殘余變形是焊接后殘存在于結(jié)構(gòu)中的變形。它包括縱向收縮變形、橫向收縮變形、彎曲變形、角變形

2009-05-15 00:34:20 17

17 實驗 譯碼器及其應(yīng)用(綜合性設(shè)計性)

一、實驗?zāi)康?. 掌握中規(guī)模集成譯碼器的邏輯功能2. 熟悉數(shù)碼管的使用3. 能使用譯碼器進(jìn)行綜合性設(shè)計二、實驗預(yù)習(xí)

2009-07-15 18:43:09 20

20 Verilog HDL 綜合實用教程第1章 基礎(chǔ)知識第2章 從Verilog結(jié)構(gòu)到邏輯門第3章 建模示例第4章 模型的優(yōu)化第5章 驗證附錄A 可綜合的語言結(jié)構(gòu)附錄B 通用庫

2009-07-20 11:21:13 86

86 采用 Verilog HDL 語言在Altera 公司的FPGA 芯片上實現(xiàn)了RISC_CPU 的關(guān)鍵部件狀態(tài)控制器的設(shè)計,以及在與其它各種數(shù)字邏輯設(shè)計方法的比較下,顯示出使用Verilog HDL語言的優(yōu)越性.關(guān)鍵詞

2009-08-21 10:50:05 69

69 分析了模擬硬件描述語言 Verilog-A 的特點及模型結(jié)構(gòu),根據(jù)仿真速度和仿真精度的折衷考慮,設(shè)計實現(xiàn)了模擬開關(guān)、帶隙基準(zhǔn)電壓源及運放的Verilog-A 行為模型。根據(jù)數(shù)模轉(zhuǎn)換器

2009-11-21 15:37:55 31

31 Verilog代碼書寫規(guī)范

本規(guī)范的目的是提高書寫代碼的可讀性、可修改性、可重用性,優(yōu)化代碼綜合和仿真的結(jié)果,指導(dǎo)設(shè)計工程師使用

2010-04-15 09:47:00 106

106 LCCT-01A 魯爾接頭綜合性能測試儀產(chǎn)品簡介LCCT-01A 型魯爾接頭綜合性能測試儀是根據(jù)“GB/T1962.1-2015(ISO594-1:19)(ISO80369)注射器、注射針

2023-11-23 12:40:54

線纜線束電磁特性仿真提供線纜線束傳輸特性仿真、線纜線束串?dāng)_仿真、線纜線束輻射抗擾度仿真、線纜線束輻射發(fā)射仿真、線纜線束敷設(shè)布局仿真分析。 服務(wù)內(nèi)容套餐名稱套餐特點線纜傳輸特性分析適用于研究

2024-11-18 11:08:03

摘 要:通過設(shè)計實例詳細(xì)介紹了用Verilog HDL語言開發(fā)FPGA/CPLD的方法,并通過與其他各種輸入方式的比較,顯示出使用Verilog HDL語言的優(yōu)越性。

2009-06-20 11:51:28 2331

2331

基于Verilog的順序狀態(tài)邏輯FSM的設(shè)計與仿真

硬件描述語言Verilog為數(shù)字系統(tǒng)設(shè)計人員提供了一種在廣泛抽象層次上描述數(shù)字系統(tǒng)的方式,同時,為計算機(jī)輔助設(shè)計工具

2010-02-04 09:32:41 2242

2242

Verilog HDL語言簡介

1.什么是Verilog HDLVerilog HDL是硬件描述語言的一種,用于數(shù)

2010-02-09 08:59:33 4137

4137 VHDL和Verilog HDL語言對比

Verilog HDL和VHDL都是用于邏輯設(shè)計的硬件描述語言,并且都已成為IEEE標(biāo)準(zhǔn)。VHDL是在1987年成為IEEE標(biāo)準(zhǔn),Verilog HDL

2010-02-09 09:01:17 10864

10864 以模擬與數(shù)字電路實驗課程為例,簡述了改進(jìn)學(xué)生實驗考核辦法的必要性,提出了一個有效的可操作的綜合性、設(shè)計性實驗考核辦法,并討論了該考核辦法的實施效果和存在的問題。改革學(xué)

2011-04-01 12:27:36 0

0 《Verilog HDL 程序設(shè)計教程》對Verilog HDL程序設(shè)計作了系統(tǒng)全面的介紹,以可綜合的設(shè)計為重點,同時對仿真和模擬也作了深入的闡述。《Verilog HDL 程序設(shè)計教程》以Verilog-1995標(biāo)準(zhǔn)為基礎(chǔ)

2011-09-22 15:53:36 0

0 有許多可綜合狀態(tài)機(jī)的Verilog代碼描述風(fēng)格,不同代碼描述風(fēng)格經(jīng)綜合后得到電路的物理實現(xiàn)在速度和面積上有很大差別。優(yōu)秀的代碼描述應(yīng)當(dāng)易于修改、易于編寫和理解,有助于仿真和調(diào)

2011-12-24 00:52:00 30

30 本文簡單探討了verilog HDL設(shè)計中的可綜合性問題,適合HDL初學(xué)者閱讀 用組合邏輯實現(xiàn)的電路和用時序邏輯實現(xiàn)的 電路要分配到不同的進(jìn)程中。 不要使用枚舉類型的屬性。 Integer應(yīng)加范圍

2012-01-17 11:17:03 0

0 可綜合的Verilog語法和語義(劍橋大學(xué),影印):第七版

2012-05-21 14:50:14 27

27 介紹利用自動化綜合工具在編碼和綜合的階段完成用于HDTV芯片設(shè)計的優(yōu)化

2012-06-15 10:31:26 1932

1932 邏輯綜合帶來了數(shù)字設(shè)計行業(yè)的革命,有效地提高了生產(chǎn)率,減少了設(shè)計周期時間。在手動轉(zhuǎn)換設(shè)計的年代,設(shè)計過程受到諸多限制,結(jié)更容易帶來人為的錯誤。而一個小小的錯誤就導(dǎo)

2012-06-25 15:21:14 44

44 Verilog HDL 數(shù)字設(shè)計教程【作者:賀敬凱;出版社:西安電子科技大學(xué)出版社】(本資料為ppt) 內(nèi)容簡介:介紹了Verilog HDL語言,狀態(tài)機(jī)設(shè)計,仿真,還有好幾個可綜合設(shè)計的舉例,除了

2012-11-28 13:43:11 491

491 Verilog硬件描述語言參考手冊,Verilog語法內(nèi)容介紹

2015-11-12 17:20:37 0

0 基于verilog語言的數(shù)字頻率計設(shè)計基于verilog語言的數(shù)字頻率計設(shè)計基于verilog語言的數(shù)字頻率計設(shè)計基于verilog語言的數(shù)字頻率計設(shè)計

2015-12-08 15:57:23 0

0 本章介紹Verilog HDL的基本要素,包括標(biāo)識符、注釋、數(shù)值、編譯程序指令、系統(tǒng)任務(wù)和系統(tǒng)函數(shù)。另外,本章還介紹了Verilog硬件描述語言中的兩種數(shù)據(jù)類型。verilog相關(guān)教程材料,有興趣的同學(xué)可以下載學(xué)習(xí)。

2016-04-25 16:09:32 17

17 VHDL語言編程學(xué)習(xí)Verilog硬件描述語言

2016-09-01 15:27:27 0

0 ;第4章至第6章主要討論如何合理地使用Verilog HDL語言描述高性能的可綜合電路;第7章和第8章重點介紹了如何編寫測試激勵以及Verilog的仿真原理;第9章展望HDL語言的發(fā)展趨勢。

2016-10-10 17:04:40 613

613 Verilog語言入門,感興趣的小伙伴們可以瞧一瞧。

2016-11-10 15:29:36 5

5 最近在寫代碼的時候總是在思考,我寫的這個能被綜合嗎?總是不放心,或是寫完了綜合的時候出問題,被搞的非常煩惱,雖然看了一些書,比如對組合邏輯用阻塞賦值,時序用非阻塞賦值,延時不能被綜合等等,但是沒有一本能完全將清楚所有的問題!

2017-02-11 11:11:00 7114

7114

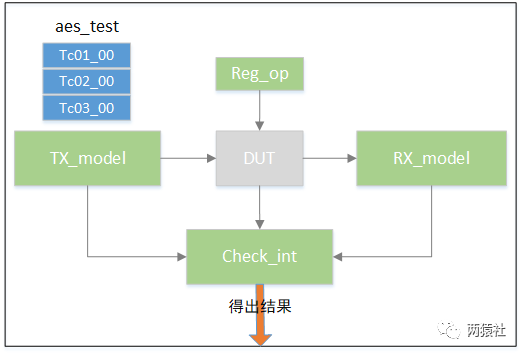

基于Verilog HDL語言的電路設(shè)計、仿真與綜合 (一)頂層模塊 本程序采用結(jié)構(gòu)化設(shè)計方法,將其分為彼此獨立又有一定聯(lián)系的三個模塊,如圖1所示:

2017-11-28 14:36:03 16

16 該資料對STM32微控制器作了詮釋和指導(dǎo),STM32的基礎(chǔ)實驗進(jìn)階應(yīng)用硬件描述和綜合性實驗的詳細(xì)資料概述包括了實物圖和原理圖。

2018-06-19 08:00:00 22

22 在接觸Verilog 語法參考手冊的時候,我們發(fā)現(xiàn)其提供了一組非常豐富的功能來描述硬件。所以大家往往會疑惑那些Verilog語句是可綜合的,那些是只能用于寫Testbench的,其實,參考手冊中只有

2019-04-20 10:59:39 5221

5221 本課程以目前流行的Xilinx 7系列FPGA的開發(fā)為主線,全面講解FPGA的原理及電路設(shè)計、Verilog HDL語言及VIVADO的應(yīng)用,并循序漸進(jìn)地從組合邏輯、時序邏輯的開發(fā)開始,深入到FPGA的基礎(chǔ)應(yīng)用、綜合應(yīng)用和進(jìn)階應(yīng)用。

2019-12-02 07:10:00 3646

3646

可綜合設(shè)計的特點:1、不使用初始化語句。2、不使用帶有延時的描述。3、不使用循環(huán)次數(shù)不確定的循環(huán)語句,如: forever 、while 等。4、盡量采用同步方式設(shè)計電路。5、除非是關(guān)鍵路徑的設(shè)計,一般不調(diào)用門級元件來描述設(shè)計的方法,建議采用行為語句來完成設(shè)計。

2019-08-01 16:55:54 11

11 Verilog中提供了四種循環(huán)語句,可用于控制語句的執(zhí)行次數(shù),分別為:for,while,repeat,forever。其中,for,while,repeat是可綜合的,但循環(huán)的次數(shù)需要在編譯之前就確定,動態(tài)改變循環(huán)次數(shù)的語句是不可綜合的。forever語句是不可綜合的,主要用于產(chǎn)生各種仿真激勵。

2019-10-13 12:23:00 20332

20332 Verilog HDL簡稱Verilog,它是使用最廣泛的硬件描述語言。

2020-03-22 17:29:00 5712

5712 端口添加多數(shù)表決電路。構(gòu)建這種三重化方案是一項非常重要的任務(wù),需要花費大量的時間和精力來修改設(shè)計代碼。本文開發(fā)了RASP-TMR工具,該工具具有以可綜合的Verilog設(shè)計文件為輸入,對設(shè)計進(jìn)行解析和三次復(fù)制的功能。該工具還生成了一個頂層模塊,其中所有三個模塊都

2020-04-16 08:00:00 5

5 的是硬件描述語言。最為流行的硬件描述語言有兩種Verilog HDL/VHDL,均為IEEE標(biāo)準(zhǔn)。Verilog HDL具有C語言基礎(chǔ)就很容易上手,而VHDL語言則需要Ada編程基礎(chǔ)。另外Verilog

2020-09-01 11:47:09 5063

5063

在現(xiàn)階段,作為設(shè)計人員熟練掌握 Verilog HDL程序設(shè)計的多樣性和可綜合性,是至關(guān)重要的。作為數(shù)字集成電路的基礎(chǔ),基本數(shù)字邏輯電路的設(shè)計是進(jìn)行復(fù)雜電路的前提。本章通過對數(shù)字電路中基本邏輯電路的erilog HDL程序設(shè)計進(jìn)行講述,掌握基本邏輯電路的可綜合性設(shè)計,為具有特定功能的復(fù)雜電路的設(shè)計打下基礎(chǔ)

2020-12-09 11:24:00 37

37 可合成Verilog是Verilog HDL的一個子集,它位于當(dāng)前合成工具(RTL和行為)的領(lǐng)域內(nèi)。本文檔指定了Verilog的一個子集V0.1。該子集旨在作為思想快速原型化的工具。

2021-01-21 16:30:55 9

9 Verilog標(biāo)準(zhǔn)前,由于Cadence公司的 Verilog-XL 仿真器廣泛使用,它所提供的Verilog LRM成了事實上的語言標(biāo)準(zhǔn)。許多第三方廠商的仿真器都努力向這一已成事實的標(biāo)準(zhǔn)靠攏。

2021-02-05 16:24:00 79

79 開發(fā)所有可綜合Verilog的語義所選擇的方法是從過于簡單的{V0{開始,然后在簡單的語義中斷時使其更加復(fù)雜。這樣可以避免不必要的復(fù)雜性。計劃對越來越大的子集(V1、V2等)進(jìn)行重新排序,這些子集將收斂到劍橋VFE project2中使用的Verilog版本。

2021-02-05 16:24:05 14

14 1、如何使用Verilog HDL描述可綜合電路 Verilog 有什么奇技淫巧?我想最重要的是理解其硬件特性。Verilog HDL語言僅是對已知硬件電路的文本描述。所以編寫前: 對所需實現(xiàn)的硬件

2021-04-04 11:19:00 4855

4855

簡單介紹Verilog HDL語言和仿真工具。

2021-05-06 16:17:10 619

619 條件語句的可綜合性 HDL語言的條件語句與算法語言的條件語句,最大的差異在于: 1.不管條件:當(dāng)前輸入條件沒有對應(yīng)的描述,則該條件為不管條件(Don’t?Care)。對應(yīng)不管條件的信號稱為不管信號

2021-05-12 09:12:22 2332

2332

(含循環(huán)體)組成的代碼塊,EDA稱為循環(huán)框架(Loop Frame)。 在這里,HDL循環(huán)語句與算法語言的循環(huán)語句的差異: 1.HDL的循環(huán)變量i是以常量進(jìn)入循環(huán)體。算法語言則是以變量進(jìn)入循環(huán)體。 2.HDL的循環(huán)體并不被循環(huán)執(zhí)行,而是被重復(fù)描述(多次重復(fù)綜合),從而實現(xiàn)建

2021-05-12 09:27:48 2830

2830

阻塞賦值和非阻塞賦值的可綜合性 Blocking Assignment阻塞賦值和NonBlocking Assignment非阻塞賦值,原本是軟件進(jìn)程管理的術(shù)語。由于Verilog團(tuán)隊是從C語言發(fā)展

2021-05-12 09:45:09 3264

3264

VHDL與Verilog硬件描述語言在數(shù)字電路的設(shè)計中使用的非常普遍,無論是哪種語言,仿真都是必不可少的。而且隨著設(shè)計復(fù)雜度的提高,仿真工具的重要性就越來越凸顯出來。在一些小的設(shè)計中,用

2021-08-04 14:16:44 4725

4725 知乎上刷到一個問題,問性能最強的編程語言是什么?看到高贊回答到是Verilog,然后在評論區(qū)就引發(fā)了一場Verilog到底算不算編程語言的爭論,我覺得比較有意思,所以就也打算嘮嘮這個事情。 趁著最近

2021-08-23 14:30:49 6909

6909 綜合性CPLD/FPGA軟件Quartus 13.0下載

2021-09-12 09:35:13 19

19 Vivado 仿真器支持混合語言項目文件及混合語言仿真。這有助于您在 VHDL 設(shè)計中包含 Verilog 模塊,反過來也是一樣。 本文主要介紹使用 Vivado 仿真器進(jìn)行混合語言仿真的一些要點

2021-10-28 16:24:49 3811

3811 Q-MIDI 為九齊公司針對音色而研發(fā)的綜合性開發(fā)軟件。包含了音色、包絡(luò)編輯、音色自動分析、實時音色

仿真等功能。用戶可以快速、輕松地利用鼠標(biāo)進(jìn)行包絡(luò)的編輯、完成音色文件與包絡(luò)的合成,而完成用戶

2022-06-14 17:13:55 4

4 Q-Tone 是九齊科技為開發(fā) NY2 系列音樂 IC 而研發(fā)的一套全新的綜合性開發(fā)系統(tǒng)。它提供了簡易的工作界面和實

時仿真功能,將使程序設(shè)計人員在開發(fā)新程序時更加便利而搭配 Q-MIDI、Quick-IO 與 Q-Writer 等外圍工具,也

將使程序開發(fā)更加簡單而有效率。

2022-06-14 17:00:29 0

0 要想深入理解Verilog就必須正視Verilog語言同時具備硬件特性和軟件特性。

2022-07-07 09:54:48 2085

2085 綜合工具讀入源文件,通過綜合算法將設(shè)計轉(zhuǎn)化為網(wǎng)表,比如DC。能夠綜合的特性要求Verilog語言能夠描述信號的各種狀態(tài)(0,1,x,z)、信號和模塊的連接(例化)以及模塊的邏輯(賦值以及各種運算符)。

2022-07-07 09:53:52 1106

1106 本規(guī)范的目的是提高書寫代碼的可讀性 可修改性 可重用性 優(yōu)化代碼綜合和仿真的結(jié) 果 指導(dǎo)設(shè)計工程師使用VerilogHDL規(guī)范代碼和優(yōu)化電路 規(guī)范化公司的ASIC設(shè)計輸入從而做到。

2022-11-23 17:28:18 1907

1907 Verilog 是硬件描述語言,顧名思義,就是用代碼的形式描述硬件的功能,最終在硬件電路上實現(xiàn)該功能。 在 Verilog 描述出硬件功能后需要使用綜合器對 Verilog 代碼進(jìn)行解釋并將代碼

2023-03-21 10:31:40 1735

1735

要想深入理解Verilog就必須正視Verilog語言同時具備硬件特性和軟件特性。在當(dāng)下的教學(xué)過程中,教師和教材都過于強調(diào)Verilog語言的硬件特性和可綜合特性。將Verilog語言的行為級語法

2023-05-25 15:10:21 1496

1496

要想深入理解Verilog就必須正視Verilog語言同時具備硬件特性和軟件特性。在當(dāng)下的教學(xué)過程中,教師和教材都過于強調(diào)Verilog語言的硬件特性和可綜合特性。將Verilog語言的行為級語法

2023-05-25 15:10:44 1379

1379

建立用于RTL綜合的Verilog標(biāo)準(zhǔn)化子集。他是貝爾實驗室所開發(fā)的ArchSyn綜合系統(tǒng)的主要設(shè)計者之一。他曾為AT&T和Lucent的許多設(shè)計師講授Verilog HDL語言和Verilog HDL綜合課程。

2023-05-26 16:59:30 2182

2182

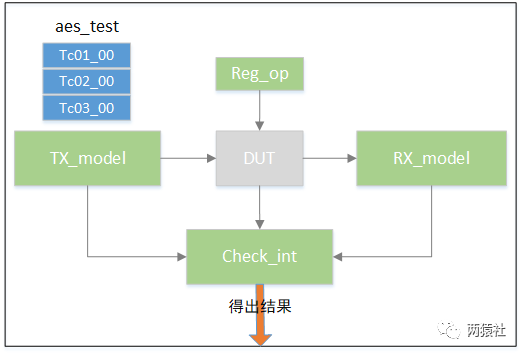

Verilog 代碼設(shè)計完成后,還需要進(jìn)行重要的步驟,即邏輯功能仿真。仿真激勵文件稱之為 testbench,放在各設(shè)計模塊的頂層,以便對模塊進(jìn)行系統(tǒng)性的例化調(diào)用進(jìn)行仿真。

2023-06-02 11:35:25 2272

2272

仿真部分結(jié)構(gòu)和設(shè)計類似,同樣有波特率、接收數(shù)據(jù)和發(fā)送數(shù)據(jù)模型。仿真的實現(xiàn)比較靈活,不用考慮可綜合性。

2023-06-05 16:08:16 2368

2368

Verilog 是一種用于數(shù)字邏輯電路設(shè)計的硬件描述語言,可以用來進(jìn)行數(shù)字電路的仿真驗證、時序分析、邏輯綜合。

2023-06-10 10:04:44 2658

2658

近日,清華大學(xué)新聞與傳播學(xué)院發(fā)布了《大語言模型綜合性能評估報告》,該報告對目前市場上的7個大型語言模型進(jìn)行了全面的綜合評估。近年,大語言模型以其強大的自然語言處理能力,成為AI領(lǐng)域的一大熱點。它們

2023-08-10 08:32:01 2137

2137

VHDL與Verilog硬件描述語言在數(shù)字電路的設(shè)計中使用的非常普遍,無論是哪種語言,仿真都是必不可少的。而且隨著設(shè)計復(fù)雜度的提高,仿真工具的重要性就越來越凸顯出來。在一些小的設(shè)計中,用

2023-09-09 10:16:56 2619

2619

Verilog語言是一種硬件描述語言(HDL),用于描述數(shù)字邏輯電路和系統(tǒng)。它是一種非常強大且廣泛使用的語言,在數(shù)字電路設(shè)計中扮演著重要的角色。其中, inout 是Verilog中的一種信號類型

2024-02-23 10:15:48 4944

4944 Verilog是一種硬件描述語言,用于描述數(shù)字電路的行為和結(jié)構(gòu)。與其他編程語言相比,Verilog具有與硬件緊密結(jié)合的特點,因此其接口機(jī)制也有一些與眾不同之處。本文將詳細(xì)介紹Verilog與其他編程

2024-02-23 10:22:37 1488

1488 ICer需要System Verilog語言得加成,這是ICer深度的表現(xiàn)。

2024-11-01 10:44:36 0

0 。然而,在實際應(yīng)用中,設(shè)計師可能會遇到各種問題,這些問題可能會影響仿真的準(zhǔn)確性和設(shè)計的可靠性。 Verilog電路仿真常見問題 仿真環(huán)境的搭建問題 仿真環(huán)境的搭建是進(jìn)行Verilog仿真的第一步。設(shè)計師需要選擇合適的仿真工具,并確保所有必要的

2024-12-17 09:53:28 1690

1690 NVIDIA Isaac 是英偉達(dá)推出的綜合性機(jī)器人開發(fā)平臺,旨在通過 GPU 加速、物理仿真和生成式 AI 技術(shù),加速自主移動機(jī)器人(AMR)、機(jī)械臂及人形機(jī)器人的開發(fā)與部署。以下從核心組件、技術(shù)

2025-04-02 18:03:32 2153

2153

電子發(fā)燒友App

電子發(fā)燒友App

評論