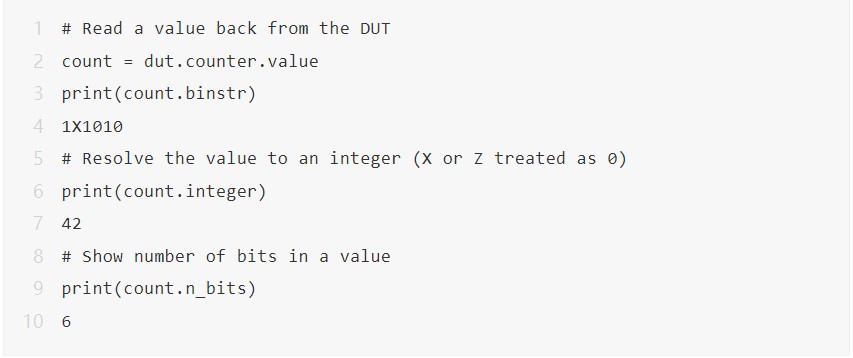

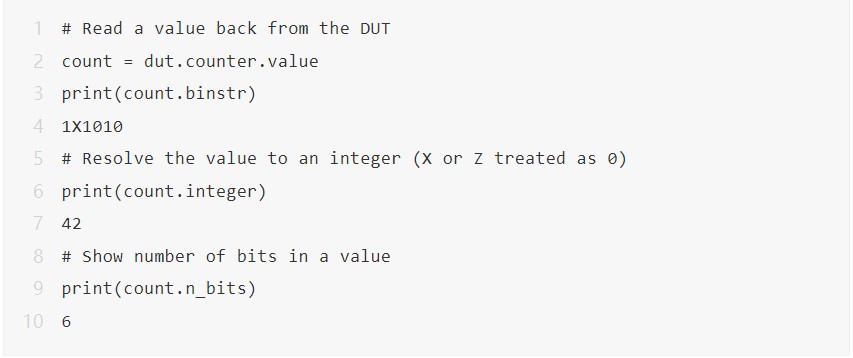

對于信號的讀取,我們在SystemVerilog中,可以直接讀取信號值,而在cocotb中,其為接口變量提供了value方法屬性用于獲取信號值。

2022-07-21 09:07:29 4740

4740

在systemverilog中,如果一個類沒有顯式地聲明構造函數(new()),那么編譯仿真工具會自動提供一個隱式的new()函數。這個new函數會默認地將所有屬性變量。

2022-11-16 09:58:24 4246

4246 默認情況下,類的成員和方法可從外部訪問使用類的對象句柄來訪問,也就是說,它們是公共的。

2022-11-28 09:26:41 2767

2767 SystemVerilog中多態能夠工作的前提是父類中的方法被聲明為virtual的。

2022-11-28 11:12:42 1094

1094 SystemVerilog中可以將類屬性聲明為常量,即“只讀”。目的就是希望,別人可以讀但是不能修改它的值。

2022-11-29 10:25:42 2506

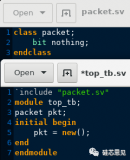

2506 談到package,用過VHDL的工程師并不陌生。實際上,SystemVerilog中的package正是從VHDL引入的,以進一步增強其在系統級的描述能力。

2023-10-07 11:33:55 4428

4428

在 SystemVerilog 中,聯合只是信號,可通過不同名稱和縱橫比來加以引用。

2023-10-08 15:45:14 2419

2419

SystemVerilog 接口的開發旨在讓設計中層級之間的連接變得更加輕松容易。 您可以把這類接口看作是多個模塊共有的引腳集合。

2024-03-04 15:25:22 2065

2065

SystemVerilog 的VMM 驗證方法學教程教材包含大量經典的VMM源代碼,可以實際操作練習的例子,更是ic從業人員的絕佳學習資料。SystemVerilog 的VMM 驗證方法學教程教材[hide][/hide]

2012-01-11 11:21:38

本帖最后由 鼻子抽筋 于 2012-2-21 15:41 編輯

SystemVerilog給予Verilog、VHDL和C/C++優點為一身的硬件描述語言,很值得學一學。1、8-bit up

2012-02-21 15:39:27

SystemVerilog有哪些標準?

2021-06-21 08:09:41

官方的一個systemverilog詳解,很詳細。推薦給打算往IC方面發展的朋友。QQ群374590107歡迎有志于FPGA開發,IC設計的朋友加入一起交流。一起為中國的IC加油!!!

2014-06-02 09:47:23

官方的一個systemverilog詳解,很詳細。推薦給打算往IC方面發展的朋友。

2014-06-02 09:30:16

systemverilog的一些基本語法以及和verilog語言之間的區別。

2015-04-01 14:24:14

學快速發展,這些趨勢你了解嗎?SystemVerilog + VM是目前的主流,在未來也將被大量采用,這些語言和方法學,你熟練掌握了嗎?對SoC芯片設計驗證感興趣的朋友,可以關注啟芯工作室推出的SoC芯片

2013-06-10 09:25:55

大家好,我對一個 round robin 的 systemverilog 代碼有疑惑。https://www.edaplayground.com/x/2TzD代碼第49和54行是怎么解析呢 ?

2017-03-14 19:16:04

FPGA中接口的連接方式。 ??也許很多FPGA工程師對SystemVerilog并不是很了解,因為以前的FPGA開發工具是不支持SystemVerilog的,導致大家都是用VHDL或者Verilog來

2021-01-08 17:23:22

在某大型科技公司的招聘網站上看到招聘邏輯硬件工程師需要掌握SystemVerilog語言,感覺SystemVerilog語言是用于ASIC驗證的,那么做FPGA工程師有沒有必要掌握SystemVerilog語言呢?

2017-08-02 20:30:21

如下圖,先建一個systemverilog的cell,但是會報錯,求幫解決下。寫個最簡單的也會報語法錯誤。

2021-06-24 06:24:26

我們將展示如何在SystemVerilog中為狀態機的命令序列的生成建模,并且我們將看到它是如何實現更高效的建模,以及實現更好的測試生成。?

2021-01-01 06:05:05

多態(Polymorphism) ,從字面意思上看指的是多種形式,在OOP(面向對象編程)中指的是同一個父類的函數可以體現為不同的行為。在SystemVerilog中,指的是我們可以使用父類句柄來

2022-12-05 17:34:00

類成員函數中const的使用,有什么注意事項?

2021-04-26 06:42:30

導入SystemVerilog程序包意味著什么?

2020-12-11 06:53:29

Systemverilog數據類型l 合并數組和非合并數組1)合并數組:存儲方式是連續的,中間沒有閑置空間。例如,32bit的寄存器,可以看成是4個8bit的數據,或者也可以看成是1個32bit

2015-08-27 14:50:39

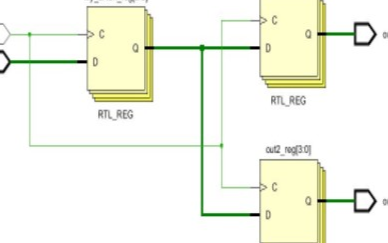

2打兩拍systemverilog與VHDL編碼1 本章目錄1)FPGA簡介2)SystemVerilog簡介3)VHDL簡介4)打兩拍verilog編碼5)打兩拍VHDL編碼6)結束語2 FPGA

2021-07-26 06:19:28

本參考手冊詳細描述了Accellera為使用Verilog硬件描述語言在更高的抽象層次上進行系統的建模和驗證所作的擴展。這些擴展將Verilog語言推向了系統級空間和驗證級空間。SystemVerilog

2009-07-22 12:14:44 188

188 SystemVerilog Assertion Handbook1 ROLE OF SYSTEMVERILOG ASSERTIONSIN A VERIFICATION METHODOLOGY

2009-07-22 14:08:48 188

188 SystemVerilog Assertion Handbook1 ROLE OF SYSTEMVERILOG ASSERTIONSIN A VERIFICATION METHODOLOGY

2009-07-22 14:12:50 20

20 Section 1 Introduction to SystemVerilog ..... 1Section 2 Literal Values... 42.1 Introduction

2009-07-22 14:18:46 39

39 Chapter 1: Introduction to SystemVerilogChapter 2: SystemVerilog Declaration SpacesExample 2-1: A

2009-07-22 14:45:34 0

0 本文利用形式化的方法對SystemVerilog的指稱語義進行研究,采用EBES(extendedbundle event structure)作為抽象模型,以便更好的描述SystemVerilog真并發的特點。我們的主要工作是:首先,

2009-12-22 14:01:07 12

12 如何采用SystemVerilog 來改善基于FPGA 的ASIC 原型關鍵詞:FPGA, ASIC, SystemVerilog摘要:ASIC 在解決高性能復雜設計概念方面提供了一種解決方案,但是ASIC 也是高投資風險的,如90nm ASIC/S

2010-02-08 09:53:33 10

10 ±15kV ESD-Protected, Single-/Dual-Channel, Bidirectional Low-Level Translators in Tiny Packages

2008-08-20 12:25:17 1067

1067 就 SystemC 和 SystemVerilog 這兩種語言而言, SystemC 是C++在硬件支持方面的擴展,而 SystemVerilog 則繼承了 Verilog,并對 Verilog 在面向對象和驗證能力方面進行了擴展。這兩種語言均支持

2010-08-16 10:52:48 5673

5673 隨著項目復雜程度的提高,最新的系統語言的聚合可以促進生產能力的激增,并為處在電子設計自動化(EDA)行業中的設計企業帶來益處。SystemVerilog和SystemC這兩種語言在設計流

2010-08-25 09:44:47 1557

1557 SystemVerilog 是過去10年來多方面技術發展和實際試驗的結晶,包括硬件描述語言(HDL)、硬件驗證語言(HVL)、SystemC、Superlog和屬性規范語言。它們都從技術和市場的成敗中得到了豐富的經

2010-09-07 09:55:16 1402

1402 文章主要介紹《VMM for SystemVerilog》一書描述的如何利用SystemVerilog語言,采用驗證方法學以及驗證庫開發出先進驗證環境。文章分為四部分,第一部分概述了用SystemVerilog語言驗證復雜S

2011-05-09 15:22:02 53

53 在介紹SystemVerilog 斷言的概念、使用斷言的好處、斷言的分類、斷言的組成以及斷言如何被插入到被測設計(DUT)的基礎上,本文詳細地介紹了如何使用不同的斷言語句對信號之間的復

2011-05-24 16:35:19 0

0 文中分析了基于Systemverilog驗證環境的結構,并在介紹I 2 C總線協議的基礎上,重點論述了驗證環境中事務產生器及驅動器的設計。

2011-12-22 17:20:21 27

27 在用STVP下載程序的時候提示:the device is protected!,此時的實測解決方案詳細請見附件。

2016-06-08 15:30:29 87

87 ADA4177-2CHIPS: OVP and EMI Protected, Precision, Low Noise and Low Bias Current Op Amp Data Sheet

2021-01-28 12:52:20 4

4 LTC7003: Fast 60V Protected High Side NMOS Static Switch Driver Data Sheet

2021-02-19 10:31:12 1

1 手冊的這一部分探討了使用SystemVerilog進行驗證,然后查看了使用SystemVerilog的優點和缺點。

2021-03-29 10:32:46 25

25 作者:limanjihe ?https://blog.csdn.net/limanjihe/article/details/83005713 SystemVerilog是一種硬件描述和驗證語言

2021-10-11 10:35:38 3040

3040 采用SystemVerilog進行仿真則更容易生成隨機數,而且對隨機數具有更強的可控性。對于隨機變量,在SystemVerilog中可通過rand或randc加數據類型的方式定義。rand表明該變量

2021-10-30 10:33:05 12568

12568

在 SystemVerilog 中,聯合體只是信號,可通過不同名稱和縱橫比來加以引用。 其工作方式為通過 typedef 來聲明聯合,并提供不同標識符用于引用此聯合體。 這些標識符稱為“字段”。

2022-02-19 19:01:44 1696

1696

本文定義了通常用于描述使用SystemVerilog對硬件功能進行建模的詳細級別的術語。

2022-03-30 11:42:02 2477

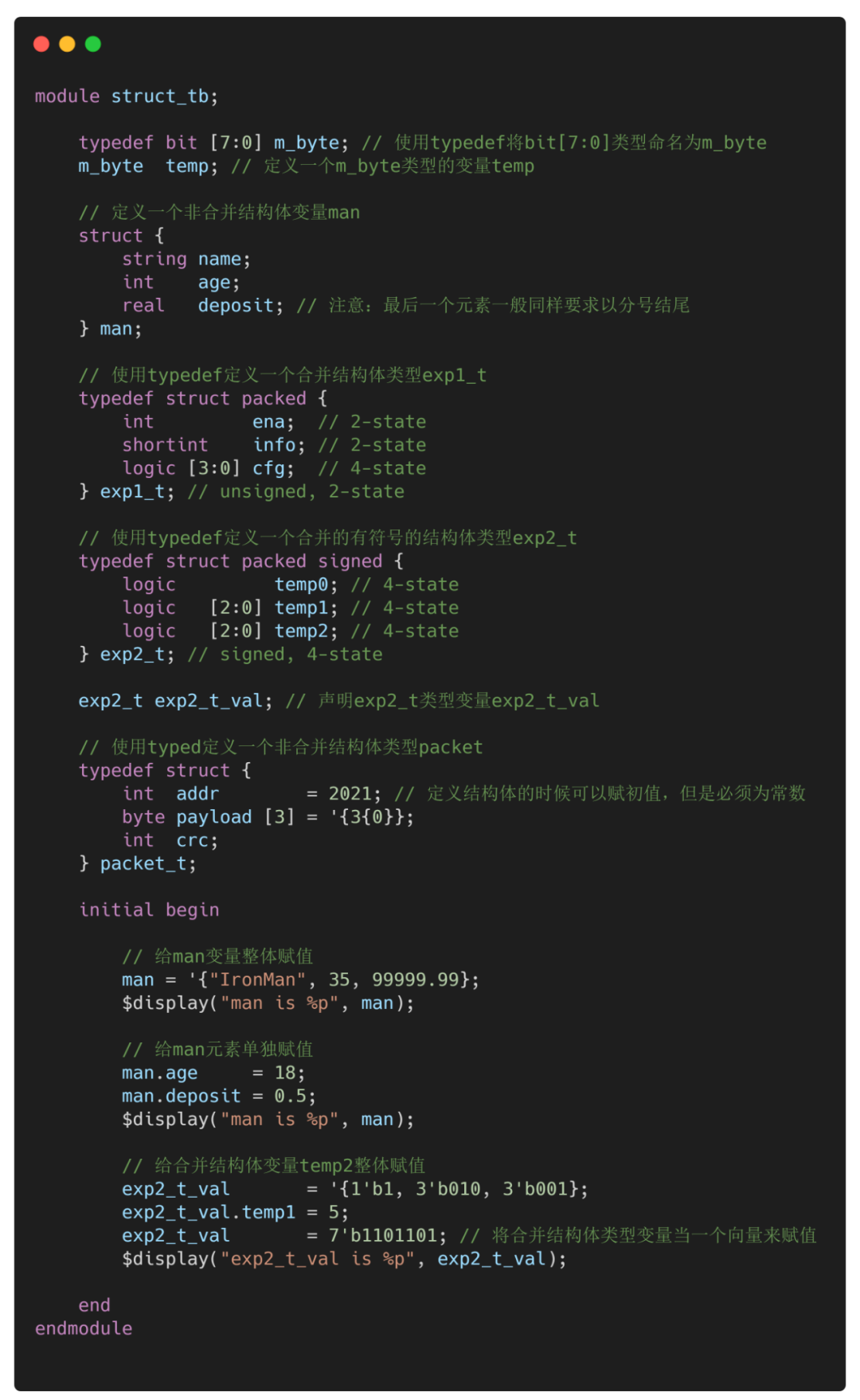

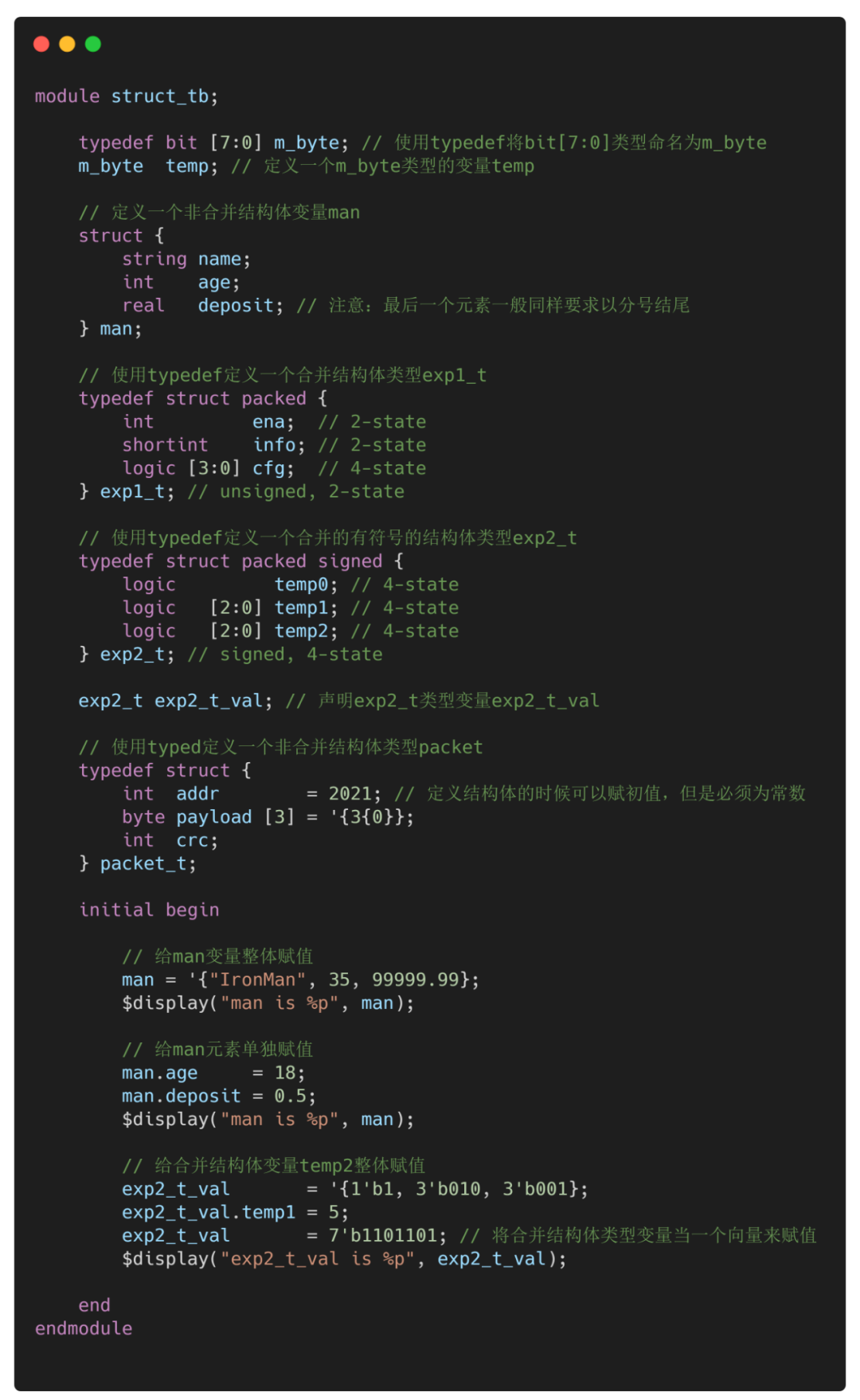

2477 默認情況下,結構體會被非壓縮的。這意味著結構體的成員被視為獨立變量或常量,并以一個共同的名稱分組在一起。SystemVerilog沒有指定軟件工具應該如何存儲非壓縮結構體的成員。不同的軟件工具具對于結構體的存儲分布也是不同的。

2022-06-30 09:54:02 2319

2319 利用Systemverilog+UVM搭建soc驗證環境

2022-08-08 14:35:05 5

5 IEEE SystemVerilog標準:統一的硬件設計規范和驗證語言

2022-08-25 15:52:21 1

1 HDLBits 是一組小型電路設計習題集,使用 Verilog/SystemVerilog 硬件描述語言 (HDL) 練習數字硬件設計~

2022-08-31 09:06:59 2676

2676 SystemVerilog中枚舉類型雖然屬于一種“強類型”,但是枚舉類型還是提供了一些“不正經”的用法可以實現一些很常見的功能,本文將示例一些在枚舉類型使用過程中的一些“不正經”用法,并給出一些使用建議。

2022-09-01 14:20:14 2499

2499 Block,也就是語句塊,SystemVerilog提供了兩種類型的語句塊,分別是begin…end為代表的順序語句塊,還有以fork…join為代表的并發語句塊。

2022-09-14 10:27:30 1782

1782 event是SystemVerilog語言中的一個強大特性,可以支持多個并發進程之間的同步。

2022-10-17 10:21:33 2232

2232 SystemVerilog casting意味著將一種數據類型轉換為另一種數據類型。在將一個變量賦值給另一個變量時,SystemVerilog要求這兩個變量具有相同的數據類型。

2022-10-17 14:35:40 3918

3918 學習Systemverilog必備的手冊,很全且介紹詳細

2022-10-19 16:04:06 3

3 SystemVerilog提供了幾個內置方法來支持數組搜索、排序等功能。

2022-10-31 10:10:37 4278

4278 SystemVerilog中除了數組、隊列和關聯數組等數據結構,這些數據結構還可以嵌套。

2022-11-03 09:59:08 2517

2517 SystemVerilog packages提供了對于許多不同數據類型的封裝,包括變量、task、function、assertion等等,以至于可以在多個module中共享。

2022-11-07 09:44:45 1810

1810 SystemVerilog“struct”表示相同或不同數據類型的集合。

2022-11-07 10:18:20 3224

3224 SystemVerilog union允許單個存儲空間以不同的數據類型存在,所以union雖然看起來和struct一樣包含了很多個成員,實際上物理上共享相同的存儲區域。

2022-11-09 09:41:28 1379

1379 tagged union包含一個隱式成員,該成員存儲tag,也就是標記,它表示這個union最終存儲的到底是哪一個成員。

2022-11-10 10:02:06 1965

1965 unpacked union中各個成員的大小可以是不同的。

2022-11-11 09:33:19 1093

1093 packed union相比unpacked union最大的一個區別就是,在packed union中,所有成員的大小必須相同,這就保證了不管union中存儲了哪一個成員,最終這個union的大小是一樣的。也正是加了這個限制,所以packed union是可綜合的。

2022-11-12 09:05:53 1594

1594 在systemverilog中方法也可以聲明為“static”。靜態方法意味著對類的所有對象實例共享。在內存中,靜態方法的聲明存儲在一個同一個地方,所有對象實例都可以訪問。

2022-11-18 09:31:44 1757

1757 SystemVerilog中的句柄賦值和對象復制的概念是有區別的。

2022-11-21 10:32:59 1419

1419 要想理解清楚SystemVerilog語言中的Upcasting和Downcasting概念,最好的方式從內存分配的角度理解。

2022-11-24 09:58:15 2236

2236 SystemVerilog是一種硬件描述和驗證語言(HDVL),它基于IEEE1364-2001 Verilog硬件描述語言(HDL),并對其進行了擴展,包括擴充了 C語言 數據類型、結構、壓縮和非

2022-12-08 10:35:05 3047

3047 SystemVerilog中Semaphore(旗語)是一個多個進程之間同步的機制之一,這里需要同步的原因是這多個進程共享某些資源。

2022-12-12 09:50:58 4241

4241 上一篇文章介紹了SystemVerilog的各種隨機化方法,本文將在其基礎上引入SystemVerilog的隨機約束方法(constraints)。通過使用隨機約束,我們可以將隨機限制在一定的空間內,有針對性地提高功能覆蓋率。

2023-01-21 17:03:00 3203

3203 在上一篇文章《SystemVerilog中至關重要的的數據類型》中,介紹了枚舉類型的本質和使用語法。本文接著介紹SV中同樣不可忽略的結構體(structure)和自定義類型(typedef),最后也

2023-01-21 17:18:00 3231

3231

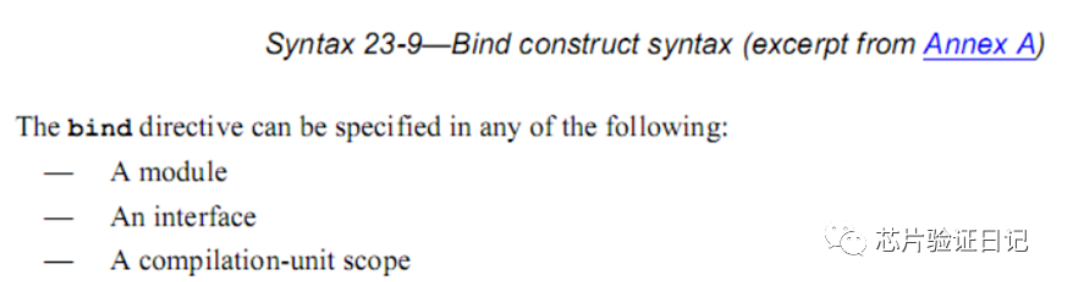

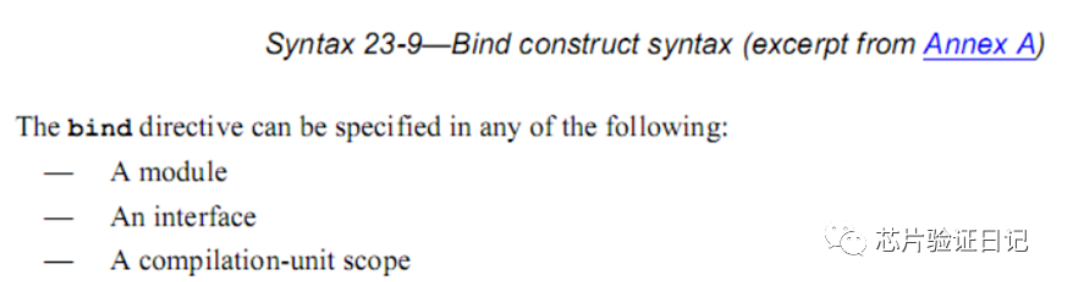

bind是systemverilog中一個重要的知識點,很多時候能夠在驗證中發揮重要的作用,今天就針對這個知識點做一個梳理,希望能幫助到大家。

2023-01-11 08:59:03 10751

10751

數獨是一種非常流行的游戲,數獨本質上也是一個約束問題,所以我們可以讓SystemVerilog的約束求解器來幫助我們解決。 約束求解器的精妙之處就是,我們只描述約束限制,繁重的數值生成工作由工具來幫我們完成。 你只需“既要...又要...”,其他的讓下人干吧。

2023-03-08 14:06:00 2286

2286 我們在工作中常常會針對數組施加各式的約束,下面列舉一下有趣的Systemverilog數組約束示例。

2023-03-08 13:12:00 1720

1720 SystemVerilog Interface是modport的一種,但比簡單的輸入、輸出或輸入輸出端口的功能更多。

2023-04-28 14:10:06 4244

4244

SystemVerilog Interface是modport的一種,但比簡單的輸入、輸出或輸入輸出端口的功能更多。

2023-04-28 14:12:22 6113

6113

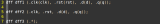

寫過Verilog和systemverilog的人肯定都用過系統自定義的函數$display,這是預定好的,可以直接調用的功能。

2023-05-16 09:27:02 1594

1594

我們在工作中常常會針對數組施加各式的約束,下面列舉一下有趣的**Systemverilog數組約束**示例

2023-05-30 11:13:21 1421

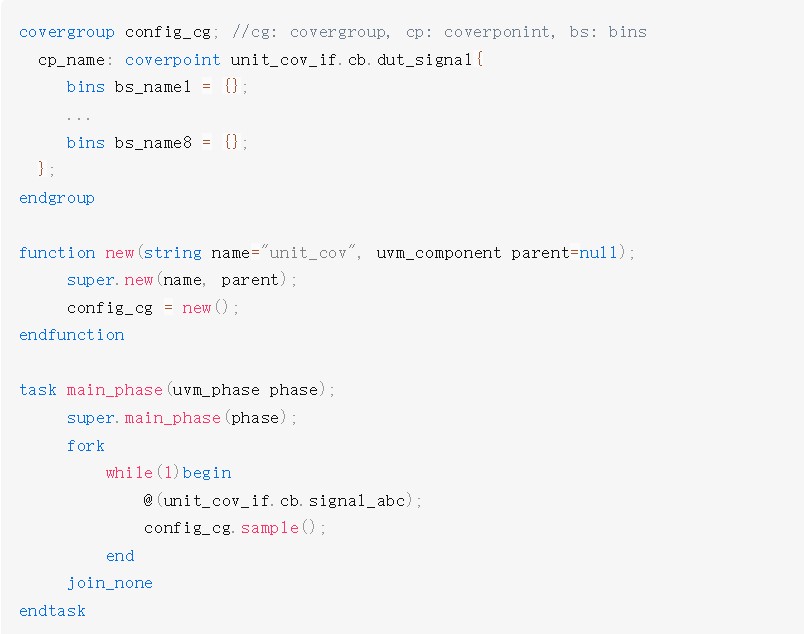

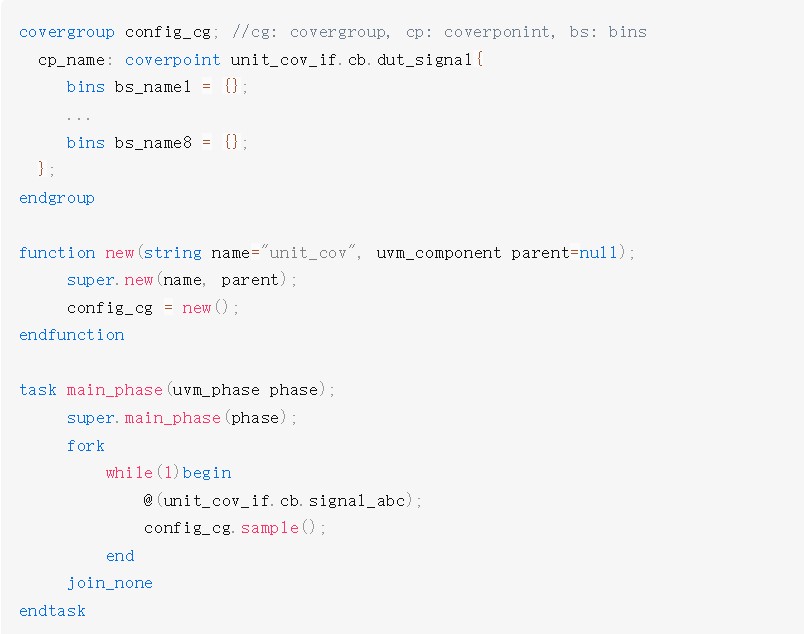

1421 SystemVerilog是一名芯片驗證工程師,必須掌握的一門語言,其中Function Coverage是必須要懂的知識點之一;

2023-06-04 16:30:24 10786

10786

在SystemVerilog中,我們知道可以使用動態數組實現數組元素個數的動態分配,即隨用隨分

2023-06-09 09:46:24 9092

9092

在systemverilog中,net用于對電路中連線進行建模,driving strength(驅動強度)可以讓net變量值的建模更加精確。

2023-06-14 15:50:16 2521

2521

為了確保驗證的完備性,我們需要量化驗證目標。SystemVerilog提供了一套豐富的覆蓋率建模方式。

2023-06-25 10:44:16 2269

2269 `ifndef是SystemVerilog/Verilog中的一種條件編譯命令,可以認為其是"if not defined"的縮寫,其用法與`ifdef相反,他們主要用來根據其后

2023-06-25 15:59:54 4458

4458

Bluespec SystemVerilog (BSV) 是由Arvind 開發的 Bluespec 語言,這是一種高級功能 硬件 描述編程語言,本質上是Haskell(Haskell ( / ?h

2023-06-27 10:14:52 1559

1559

SystemVeirlog的全面支持是開發商用仿真器的第一道門檻。市面上可以找到不少基于純Verilog的仿真器,但是真正能完整支持SystemVerilog 的仍然屈指可數。如何全面地支持SystemVerilog語言,是開發仿真器的一個重要任務。

2023-07-14 15:15:25 1210

1210

本文講一下SystemVerilog的time slot里的regions以及events的調度。SystemVerilog語言是根據離散事件執行模型定義的,由events驅動。

2023-07-12 11:20:32 2823

2823

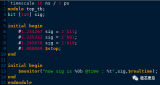

在SystemVerilog中,輸出信息顯示時間時,經常會在輸出信息格式中指定“%t”格式符,一般情況下“%t”輸出的格式都是固定的,但是這樣固定的輸出顯示的時間可能有時會讓用戶看起來感覺比較詫異,例如下面的示例。

2023-08-16 09:41:58 3826

3826

在Verilog和SystemVerilog中經常需要在使用變量或者線網之前,期望變量和線網有對應的初始值

2023-08-25 09:47:56 1872

1872

上一篇文章《暗藏玄機的SV隨機化》介紹了SystemVerilog的各種隨機化方法,本文將在其基礎上引入SystemVerilog的隨機約束方法(constraints)。通過使用隨機約束,我們可以將隨機限制在一定的空間內,有針對性地提高功能覆蓋率。

2023-09-24 12:15:30 3513

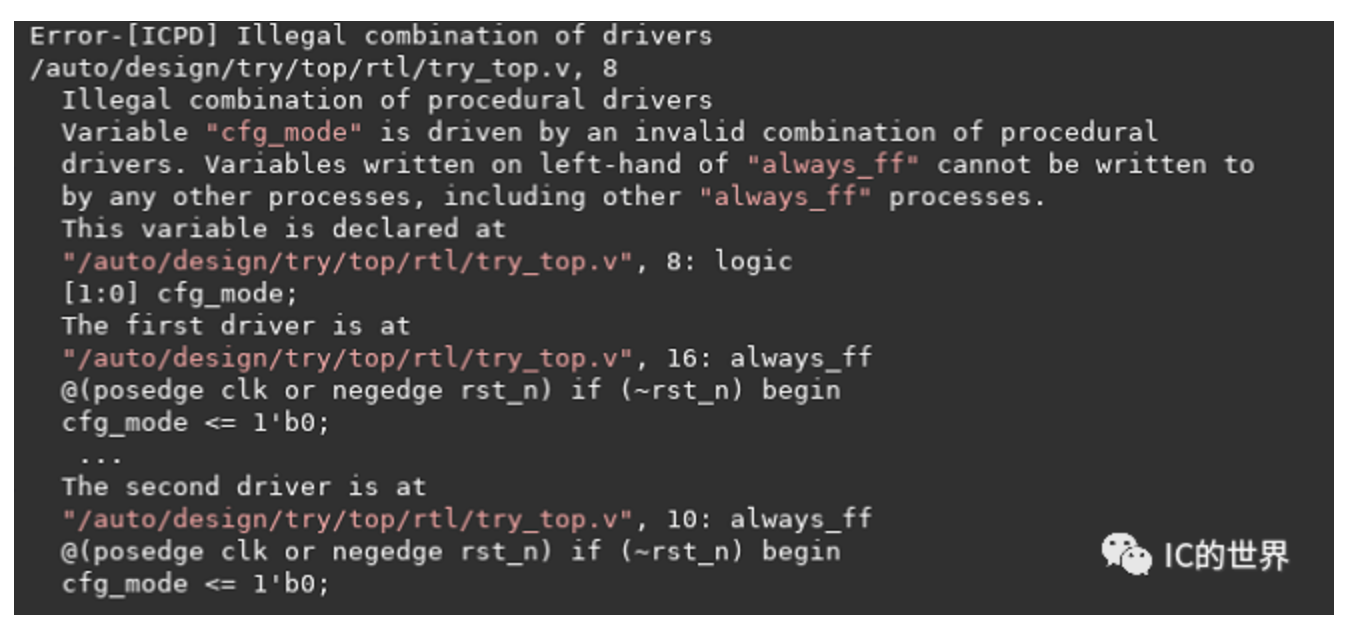

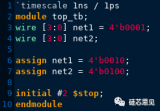

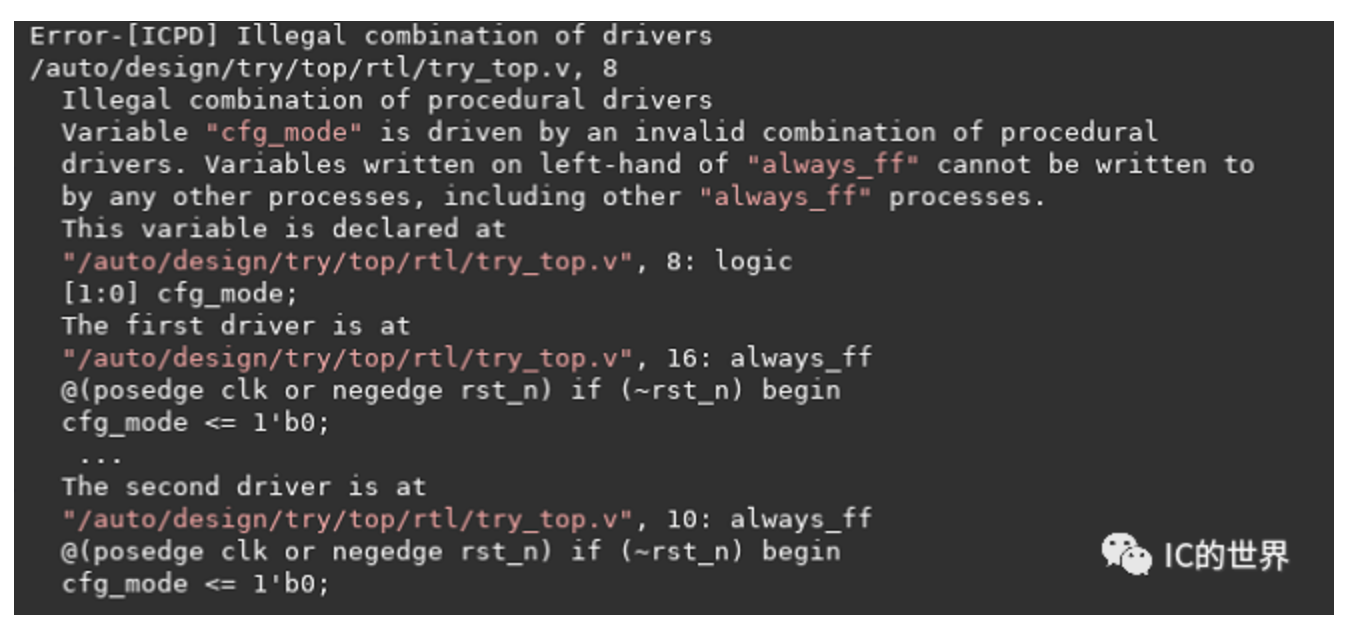

3513 在systemverilog協議中,logic定義四態值,即向量(vector)的每個位(bit)可以是邏輯0, 1, Z或X,與verilog協議中的reg很接近。但是logic有個很明顯的優勢,不允許多驅動。

2023-09-28 17:34:37 3273

3273

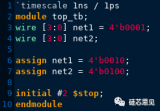

在SystemVerilog中,類型可以分為線網(net)和變量(variable)。線網的賦值設定與Verilog的要求相同,即線網賦值需要使用連續賦值語句(assign),而不應該出現在過程塊(initial/always)中。

2023-10-13 14:53:19 3751

3751

談到SystemVerilog,很多工程師都認為SystemVerilog僅僅是一門驗證語言,事實上不只如此。傳統的Verilog和VHDL被稱為HDL(Hardware Description

2023-10-19 11:19:19 2240

2240

在systemverilog協議中,logic定義四態值,即向量(vector)的每個位(bit)可以是邏輯0, 1, Z或X,與verilog協議中的reg很接近。但是logic有個很明顯的優勢,不允許多驅動。

2023-10-26 09:32:24 2256

2256

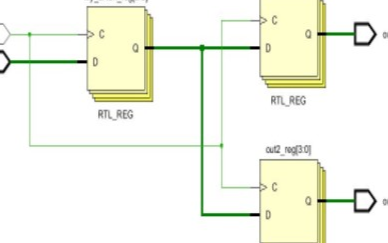

我們再從對可綜合代碼的支持角度看看SystemVerilog相比于Verilog的優勢。針對硬件設計,SystemVerilog引入了三種進程always_ff,always_comb

2023-10-26 10:05:09 2159

2159

本文分享一些SystemVerilog的coding guideline。

2023-11-22 09:17:30 1391

1391

電子發燒友App

電子發燒友App

評論