1.前言

最近幫朋友搞定一個(gè)小問題,記錄一下。不啰嗦,直接上結(jié)論:當(dāng)某個(gè)信號(hào)出現(xiàn)多于一個(gè)驅(qū)動(dòng)源的時(shí)候,或者某個(gè)信號(hào)是雙向(inout)的時(shí)候,都需要使用wire來完成線網(wǎng)連接。具體用法就是聲明某個(gè)信號(hào)為wire sigal_a;或者wire logic signal_a;就可以了。注意直接聲明為logic signal_a;是不行的,會(huì)報(bào)類似如下的錯(cuò)誤:xmelab: *E,ICDCBA: Illegal combination of driver and output clockvar to variable 'signal_a' detected (output clockvar found in ......).

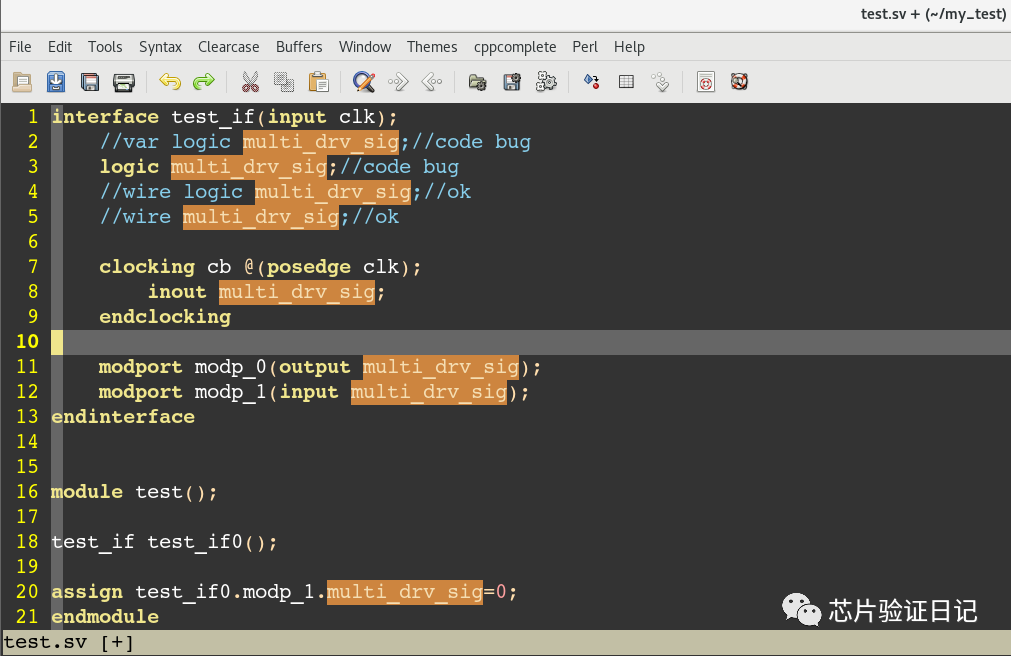

2. 實(shí)例代碼

interface test_if(input clk); //var logic multi_drv_sig;//code bug logic multi_drv_sig;//code bug //wire logic multi_drv_sig;//ok //wire multi_drv_sig;//ok clocking cb @(posedge clk); inout multi_drv_sig; endclocking modport modp_0(output multi_drv_sig); modport modp_1(input multi_drv_sig); endinterface module test(); test_if test_if0(); assign test_if0.modp_1.multi_drv_sig=0; endmodule

3.Makefile腳本

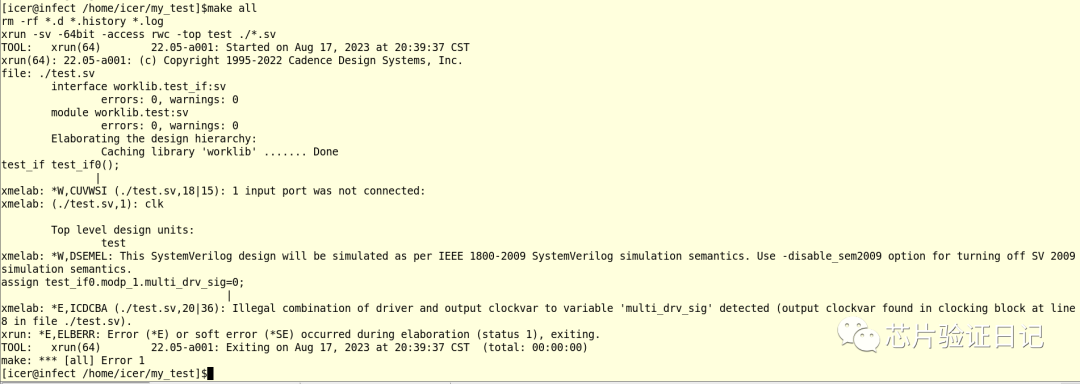

all:clean xrun -sv -64bit -access rwc -top test ./*.sv clean: rm -rf *.d *.history *.log4.仿真結(jié)果

5.報(bào)錯(cuò)信息查詢

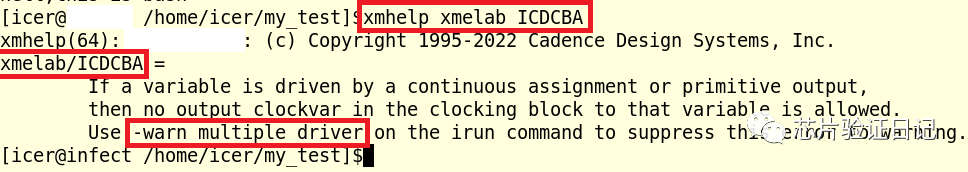

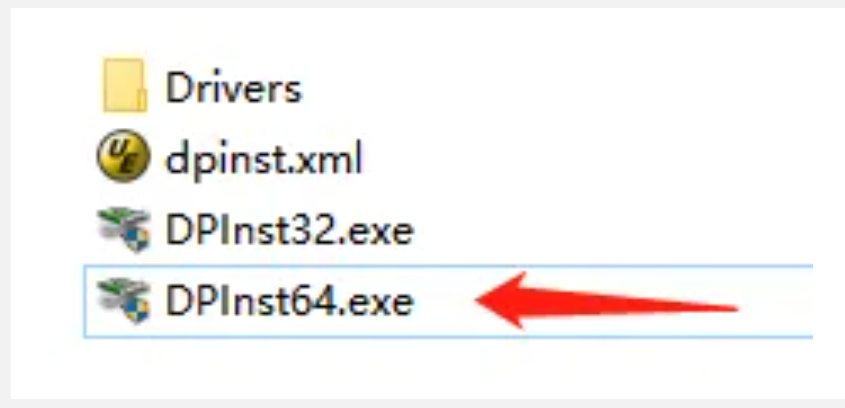

如下圖所示,查詢報(bào)錯(cuò)信息的含義,xrun甚至還給出了解決方案,通過添加工具提供的選項(xiàng)-warn_multiple_driver的確可以將這個(gè)*E的Error降為Warning,但是這不是問題的根源。

6. 問題的根源

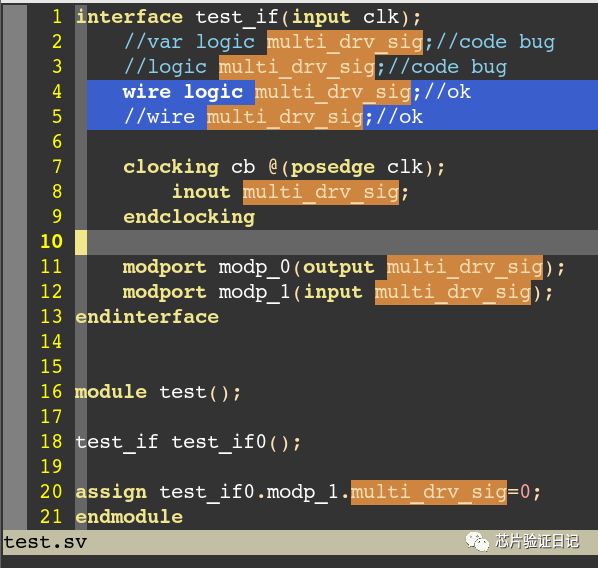

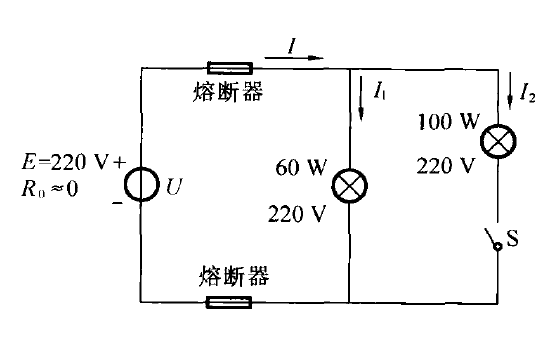

如下圖所示,第4行和第5行的用法都是對(duì)的,第2行和第3行的用法都是錯(cuò)誤的。

7. Summary& Conclusion

在SystemVerilog中,類型可以分為線網(wǎng)(net)和變量(variable)。線網(wǎng)的賦值設(shè)定與Verilog的要求相同,即線網(wǎng)賦值需要使用連續(xù)賦值語句(assign),而不應(yīng)該出現(xiàn)在過程塊(initial/always)中;相比于線網(wǎng)驅(qū)動(dòng)的限制,變量(var)類型的驅(qū)動(dòng)要求就沒有那么多了,如logic [15:0] signal_b,該變量默認(rèn)類型是var(變量),對(duì)它可以使用連續(xù)賦值或過程賦值。

簡(jiǎn)言之,可以在module中的數(shù)值存儲(chǔ)和線網(wǎng)連接,多數(shù)情況下使用logic類型變量,而很少有只能使用wire的情況。那么什么時(shí)候需要使用wire類型呢?就是本文的這種scenario:當(dāng)某個(gè)信號(hào)出現(xiàn)多于一個(gè)驅(qū)動(dòng)源的時(shí)候,或者某個(gè)信號(hào)是雙向(inout)的時(shí)候,都需要使用wire來完成線網(wǎng)連接。具體用法就是聲明某個(gè)信號(hào)為wire sigal_a;或者wire logic signal_a;就可以了。

編輯:黃飛

-

信號(hào)處理

+關(guān)注

關(guān)注

49文章

1143瀏覽量

105097 -

Verilog

+關(guān)注

關(guān)注

30文章

1374瀏覽量

114522 -

Makefile

+關(guān)注

關(guān)注

1文章

125瀏覽量

20339

原文標(biāo)題:SystemVerilog中如何處理信號(hào)的雙驅(qū)動(dòng)問題

文章出處:【微信號(hào):處芯積律,微信公眾號(hào):處芯積律】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

RCC電路原理與設(shè)計(jì)及問題解析

round robin 的 systemverilog 代碼

UART串口與LWIP以太網(wǎng)問題解析

電視卡常見問題解決方法(驅(qū)動(dòng)問題等)

運(yùn)算放大器容性負(fù)載驅(qū)動(dòng)問題

電工學(xué)知識(shí)要點(diǎn)與習(xí)題解析

解決高頻MEMS測(cè)試驅(qū)動(dòng)問題的方案是什么

SystemVerilog里的regions以及events的調(diào)度

光耦失效的幾種常見問題解析

USB驅(qū)動(dòng)問題:設(shè)備無法識(shí)別的全面指南!

SystemVerilog:處理信號(hào)雙驅(qū)動(dòng)問題解析

SystemVerilog:處理信號(hào)雙驅(qū)動(dòng)問題解析

評(píng)論