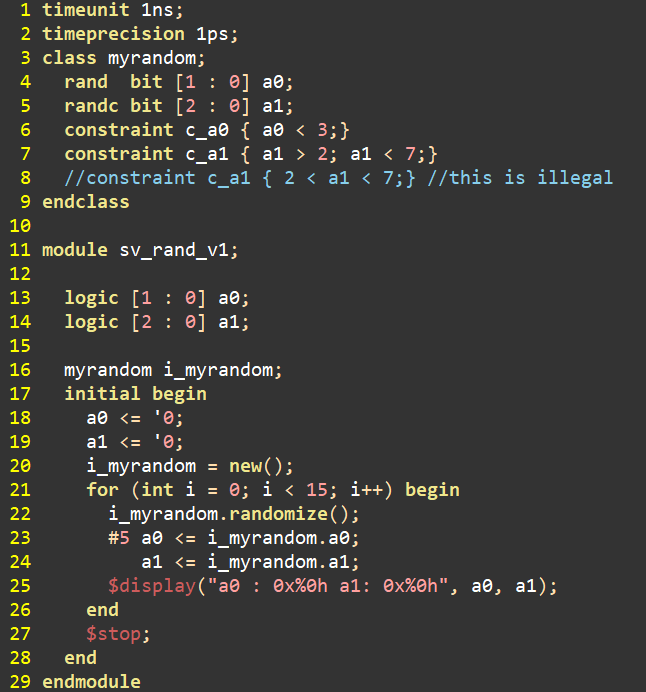

采用SystemVerilog進行仿真則更容易生成隨機數(shù),而且對隨機數(shù)具有更強的可控性。對于隨機變量,在SystemVerilog中可通過rand或randc加數(shù)據(jù)類型的方式定義。rand表明該變量為隨機變量,且在指定范圍內(nèi)服從均勻分布;randc是在rand的基礎上要求當生成的隨機數(shù)已經(jīng)在指定范圍內(nèi)完成一次遍歷之后,將重復遍歷,c為cyclic(循環(huán))。聲明隨機變量后,需要通過constraint限定隨機數(shù)需要滿足的條件。這些都需要在class中聲明。

案例1:用小于號《 大于號 》 小于等于號 《= 大于等于號》=創(chuàng)建限定條件

代碼如下圖所示。代碼第6行限定了a0必須小于3,第7行限定了a1必須大于2且小于7。注意,這4個關系運算符不能連寫,如代碼第8行是不合法的。代碼第16行對class實例化,代碼第20行為class對象分配內(nèi)存空間并完成class對象的初始化。代碼第22行用于判定隨機數(shù)是否成功生成,若成功則返回1,否則返回0。

編輯:jq

-

仿真

+關注

關注

55文章

4507瀏覽量

138533 -

Verilog

+關注

關注

30文章

1374瀏覽量

114617 -

System

+關注

關注

0文章

166瀏覽量

38757 -

代碼

+關注

關注

30文章

4974瀏覽量

74210

原文標題:SystemVerilog仿真如何生成隨機數(shù)

文章出處:【微信號:Lauren_FPGA,微信公眾號:FPGA技術驛站】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

硅臻正式推出QRNG全系列量子隨機數(shù)發(fā)生器產(chǎn)品

飛凌嵌入式ElfBoard-系統(tǒng)信息與資源之產(chǎn)生隨機數(shù)

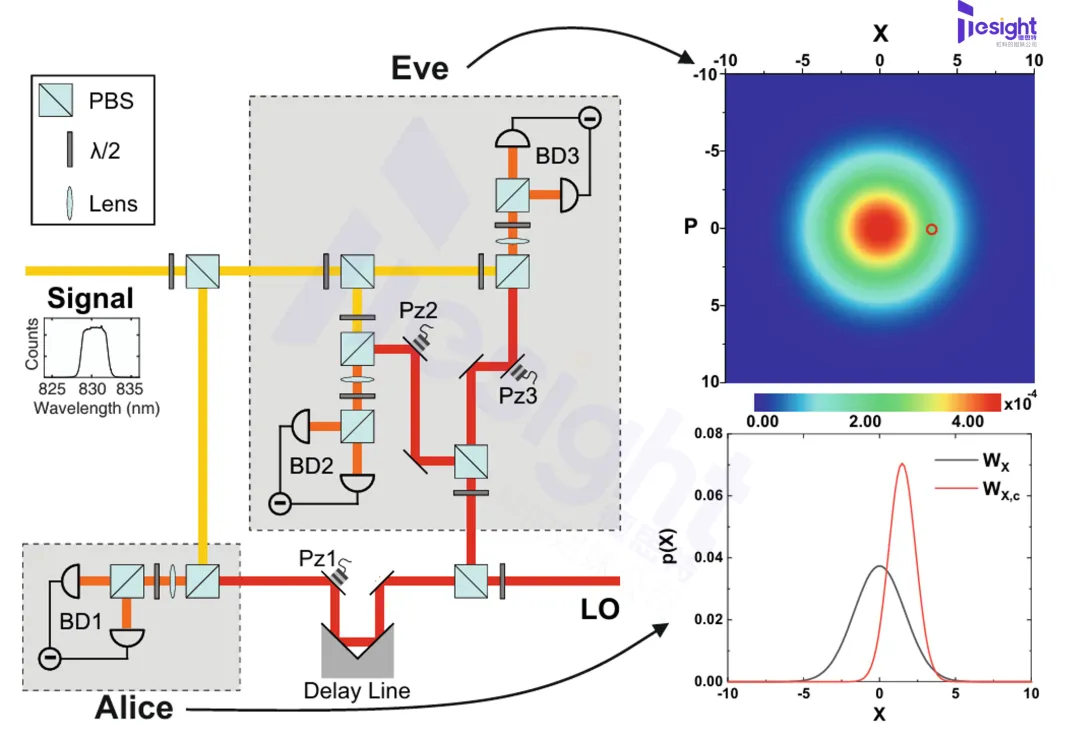

如何在LTspice仿真中實現(xiàn)偽隨機數(shù)和真隨機數(shù)的生成

德思特應用 | 前沿量子隨機數(shù)研究:多特蒙德工業(yè)大學如何通過高速數(shù)字化儀保障信息安全

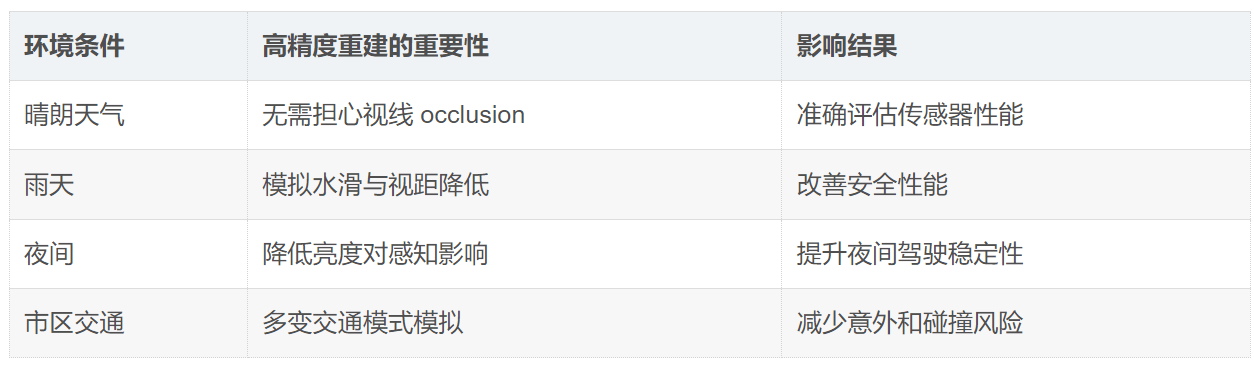

如何選擇適合的智駕仿真工具進行場景生成和測試?

?基于RNG90的真隨機數(shù)生成器技術解析與應用指南

凌科芯安LCSHA204安全加密芯片介紹

真隨機數(shù)和偽隨機數(shù)的區(qū)別

生成式 AI 重塑自動駕駛仿真:4D 場景生成技術的突破與實踐

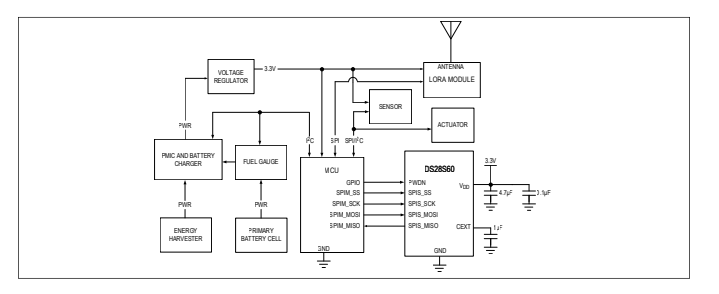

DS28S60具有ChipDNA的DeepCover加密協(xié)處理器技術手冊

如何利用SystemVerilog仿真生成隨機數(shù)

如何利用SystemVerilog仿真生成隨機數(shù)

評論