一文詳細(xì)了解可編程邏輯器件(PLD)

在過(guò)去的十年中,可編程邏輯器件(PLD)市場(chǎng)不斷增長(zhǎng),對(duì)PLD的需求不斷增加。具有可編程特性且可編程....

FPGA設(shè)計(jì)流程

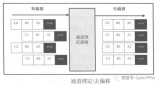

現(xiàn)代FPGA的體系結(jié)構(gòu)包括CLB陣列、塊RAM、乘法器、DSP、IOB和數(shù)字時(shí)鐘管理器(DCM)。延....

Verilog時(shí)序邏輯中同步計(jì)數(shù)器的功能和應(yīng)用

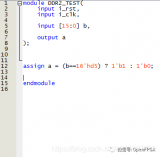

沒(méi)有任何寄存器邏輯,RTL設(shè)計(jì)是不完整的。RTL是寄存器傳輸級(jí)或邏輯,用于描述依賴(lài)于當(dāng)前輸入和過(guò)去輸....

Verilog設(shè)計(jì)中函數(shù)和任務(wù)的作用分析

任務(wù)和函數(shù)在Verilog中用于描述常用的功能行為。與其在不同的地方復(fù)制相同的代碼,不如根據(jù)需求使用....

Verilog RTL和觸發(fā)器中的同步和異步復(fù)位功能分析

沒(méi)有任何寄存器邏輯,RTL設(shè)計(jì)是不完整的。RTL是寄存器傳輸級(jí)或邏輯,用于描述依賴(lài)于當(dāng)前輸入和過(guò)去輸....

硬件開(kāi)源編程利器MyHDL簡(jiǎn)介

自從1995年Verilog HDL 1364-1995標(biāo)準(zhǔn)發(fā)布至今已經(jīng)20多年了,說(shuō)他經(jīng)久不衰并不....

異步設(shè)計(jì)之Verilog時(shí)序分析

沒(méi)有任何寄存器邏輯,RTL設(shè)計(jì)是不完整的。RTL是寄存器傳輸級(jí)或邏輯,用于描述依賴(lài)于當(dāng)前輸入和過(guò)去輸....

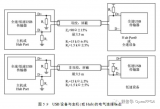

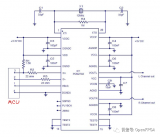

CAN總線特點(diǎn)及FPGA的實(shí)現(xiàn)

【科普】CAN總線介紹及FPGA實(shí)現(xiàn)方案簡(jiǎn)介 這里我們先逆推一下CAN總線的一些特點(diǎn)。 第一,CAN....

GameBoy硬件介紹及FPGA實(shí)現(xiàn)

拯救童年系列-GameBoy介紹及FPGA實(shí)現(xiàn) 這個(gè)掌上游戲機(jī)應(yīng)該不需要過(guò)多言語(yǔ),大部分的80后、9....

Verilog/FPGA開(kāi)源項(xiàng)目介紹

優(yōu)秀的 Verilog/FPGA開(kāi)源項(xiàng)目介紹(七)- CAN0、CAN總線介紹《【科普】CAN總線介....

Verilog HDL 編譯器指令說(shuō)明

Verilog HDL 編譯器指令 復(fù)雜一點(diǎn)的系統(tǒng)在進(jìn)行設(shè)計(jì)或者驗(yàn)證時(shí),都會(huì)用到一些編譯器指令,那么....

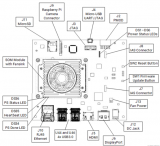

Kria KV260超長(zhǎng)干貨之開(kāi)箱指南

本篇文章來(lái)自 王偉博士, 北京中際賽威文化發(fā)展有限公司 FPGA技術(shù)專(zhuān)家 中國(guó)高科技產(chǎn)業(yè)化研究會(huì)智能....

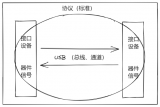

優(yōu)秀的 Verilog/FPGA開(kāi)源項(xiàng)目之 USB通信

優(yōu)秀的 Verilog/FPGA開(kāi)源項(xiàng)目介紹(五)- USB通信 USB是我們生活中非常非常常見(jiàn)的接....

什么是DPU 未來(lái)的DPU智能?卡硬件形態(tài)

1.什么是DPU DPU(Data Processing Unit)是以數(shù)據(jù)為中心構(gòu)造的專(zhuān)用處理器,....

FPGA和USB3.0通信-USB3.0協(xié)議簡(jiǎn)介

今天開(kāi)始將會(huì)通過(guò)4~5篇文章介紹FPGA和USB3.0通信的相關(guān)知識(shí),這其實(shí)是《FPGA和外圍接口(....

詳解串行總線中的SATA協(xié)議

書(shū)接上回-《串行總線技術(shù)(一)-串行總線結(jié)構(gòu)(以PCIe為例)》《串行總線技術(shù)(二)-串行總線中的先....

兩個(gè)網(wǎng)絡(luò)相關(guān)的開(kāi)源項(xiàng)目詳解

今天介紹兩個(gè)(only two)網(wǎng)絡(luò)相關(guān)的開(kāi)源項(xiàng)目。 Alex的verilog-ethernet之前....

異構(gòu)計(jì)算發(fā)展趨勢(shì)的助力

1.什么是DPU DPU(Data Processing Unit)是以數(shù)據(jù)為中心構(gòu)造的專(zhuān)用處理器,....

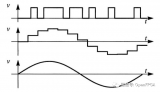

串行總線中的先進(jìn)設(shè)計(jì)理念及SerDes/PMA介紹

串行總線技術(shù)(二)-串行總線中的先進(jìn)設(shè)計(jì)理念及SerDes/PMA介紹字節(jié)分割/鏈路聚合下面以PCI....

Vivado中運(yùn)行時(shí)出現(xiàn)visual c++運(yùn)行錯(cuò)誤該如何解決

Vivado中運(yùn)行時(shí)出現(xiàn)visual c++運(yùn)行錯(cuò)誤的解決辦法Win10系統(tǒng)中運(yùn)行Vivado一直好....

簡(jiǎn)單介紹一下-Verilog-AMS的基礎(chǔ)知識(shí)

混合信號(hào)建模語(yǔ)言Verilog-AMS很多人做模擬電路的朋友,都希望有一款“模擬FPGA”,希望有一....

VIVADO中時(shí)序報(bào)告中WNS、WHS、TNS、THS有什么含義

VIVADO中時(shí)序報(bào)告中WNS,WHS,TNS,THS含義運(yùn)行“report_timing”或“re....

串行總線的優(yōu)缺點(diǎn)優(yōu)點(diǎn)

串行總線技術(shù)(一)-串行總線結(jié)構(gòu)(以PCIe為例)串行總線的出現(xiàn)在早期的計(jì)算機(jī)系統(tǒng)中,多數(shù)外圍設(shè)備使....

基于python的用于構(gòu)建仿真及測(cè)試用例的lib庫(kù)cocotb

?? ????對(duì)于從事ASIC行業(yè)及FPGA行業(yè)的小伙伴來(lái)說(shuō),仿真是一件必不可少的事情。或許有人是驗(yàn)....

Vivado中XDC文件的約束順序

很對(duì)人在使用Vivado時(shí)喜歡使用多個(gè)約束文件對(duì)整個(gè)工程進(jìn)行約束,同時(shí)Vivado允許設(shè)計(jì)者使用一個(gè)....

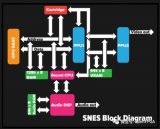

童年修復(fù)系列-SNES芯片組介紹及FPGA實(shí)現(xiàn)

超級(jí)任天堂1990年11月21日在日本開(kāi)始發(fā)售,北美于1991年8月13日發(fā)售,歐洲于1992年4月....

優(yōu)秀的 Verilog/FPGA開(kāi)源項(xiàng)目介紹(一)

優(yōu)秀的 Verilog/FPGA開(kāi)源項(xiàng)目介紹(一)-PCIe通信 今天開(kāi)始會(huì)陸續(xù)介紹一些優(yōu)秀的開(kāi)源項(xiàng)....