探討always和always_ff的編碼風格

數字門級電路可分為兩大類:組合邏輯和時序邏輯。鎖存器是組合邏輯和時序邏輯的一個交叉點,在后面會作為單....

可不可以同時在Windows和Linux上做FPGA開發呢?

Linux上運行Vivado這類EDA工具要比Window上快很多,大概就是優化的問題,所以選擇Li....

在AMD FPGA上簡單實現Xilinx DDS IP

直接數字合成器 (DDS) 是軟件定義無線電和數字通信系統中的關鍵工具,因為它們提供了一種在數字域中....

組合邏輯決策優先級介紹

組合邏輯描述了門級電路,其中邏輯塊的輸出直接反映到該塊的輸入值的組合,例如,雙輸入AND門的輸出是兩....

使用函數表示組合邏輯的方法

數字門級電路可分為兩大類:組合邏輯和時序邏輯。鎖存器是組合邏輯和時序邏輯的一個交叉點,在后面會作為單....

這幾個神級開源網站,都是FPGA/IC項目

其他平臺我看的比較少,在AMD-Xilinx分類下,有幾個大佬一直致力于開源項目的分享,包括神經網絡....

如何避免組合邏輯程序中的意外鎖存

組合邏輯描述了門級電路,其中邏輯塊的輸出直接反映到該塊的輸入值的組合,例如,雙輸入AND門的輸出是兩....

在線學習SystemVerilog:移位寄存器

設計一個100bit的可左移或右移的移位寄存器,附帶同步置位和左移或右移的使能信號。本題中,移位寄存....

數字硬件建模SystemVerilog-組合邏輯建模(1)連續賦值語句

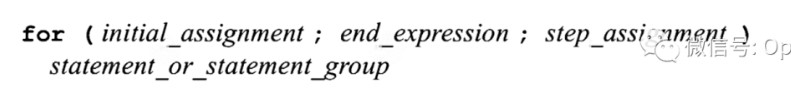

SystemVerilog有三種在可綜合RTL級別表示組合邏輯的方法:連續賦值語句、always程序....

在ultrascale+上利用VCU和DPU實現的智能零售系統

整個系統是以DPU為核心,在 DPU 上部署對象檢測模型實現實時智能檢測,該系統視頻輸入可以來自 V....

構建一個4位二進制計數器

構建一個4位二進制計數器,計數范圍從0到15(包括0和15),計數周期為16。同步復位輸入時,將計數....

什么是TinyML?它可以(也不能)用于什么?

FPGA一直以低功耗、可重構的特點在各個領域內應用,同時也可以大大增加物聯網應用環境,所以在FPGA....

Vitis HLS圖像處理平臺搭建

在 2019.2 以上的版本中AMD-Xilinx去除了對 OpenCV 的庫函數的直接支持,需要我....

寫出一個包含觸發器和多路選擇器的子模塊

我們用3個包含觸發器和多路選擇器的子模塊來實現圖中電路。題目要求我們寫出包含一個觸發器和一個多路選擇....

雙MIPI攝像頭圖像系統設計

為了讓系統快速啟動和運行,我們將從賽靈思的一個示例項目開始設計。要打開參考項目,我們需要首先創建一個....

使用AXI4S接口的視頻IP細節介紹

AXI4S攜帶實際的視頻數據(無行場消隱),由主機和從機接口驅動,如Figure 1-1所示。

如何通過NoC從Versal應用處理單元(APU)訪問AXI BRAM

Versal 架構將“Scalar Engine”(標量引擎)、“Adaptable Engine”....

如何通過NoC 從 Versal應用處理單元訪問AXI BRAM

Versal 架構將“Scalar Engine”(標量引擎)、“Adaptable Engine”....

Problem 80-89(觸發器和鎖存器(1))

D 觸發器是一個電路,存儲 1bit 數據,并定期地根據觸發器的輸入(d)更新這 1 bit 數據,....

RTL建模中的函數和任務討論

函數和任務可以在使用它們的模塊或接口中定義。定義可以出現在調用函數或任務的語句之前或之后完成,函數和....

continue和break跳轉語句介紹

跳轉語句允許程序代碼跳過一個或多個編程語句,SystemVerilog的jump語句是continu....

?構建自定義AXI4-Stream FIR濾波器

為了方便用戶進行相關設計,Vivado 提供了一個內置的 IP 封裝編輯器工具,它可以為 AXI I....

如何簡化從 XPE 向 PDM 的遷移

電源設計管理器 (PDM) 是全新的下一代功耗評估平臺,設計目的是為 Versal 和 Kria S....