優秀的 Verilog/FPGA開源項目介紹(七)- CAN0、CAN總線介紹《【科普】CAN總線介紹及FPGA實現方案簡介》

1、CAN權威文檔CAN總線有兩個ISO國際標準:ISO11898 和 ISO11519。其中:

ISO11898 定義了通信速率為 125 kbps~1 Mbps 的高速 CAN 通信標準,屬于閉環總線,傳輸速率可達1Mbps,總線長度 ≤ 40米。

ISO11519 定義了通信速率為 10~125 kbps 的低速 CAN 通信標準,屬于開環總線,傳輸速率為40kbps時,總線長度可達1000米。

ISO 11898 文檔在這里

鏈接//caiyun.139.com/m/i?1B5C60ZjPpmPA提取碼:PR9t復制內容打開和彩云PC客戶端,操作更方便哦

3、【小梅哥FPGA】使用FPGA實現CAN通信的例子(NIOS+CAN IP)

https://bbs.elecfans.com/jishu_1385802_1_1.html

這是小梅哥FPGA開發板上的實例,之所以放到第一個是因為這是目前FPGA實現CAN通信的比較完美的解決方案,單純使用硬件描述語言的IP,會有一些不可預知的BUG,但是使用軟核處理器是比較完美的。

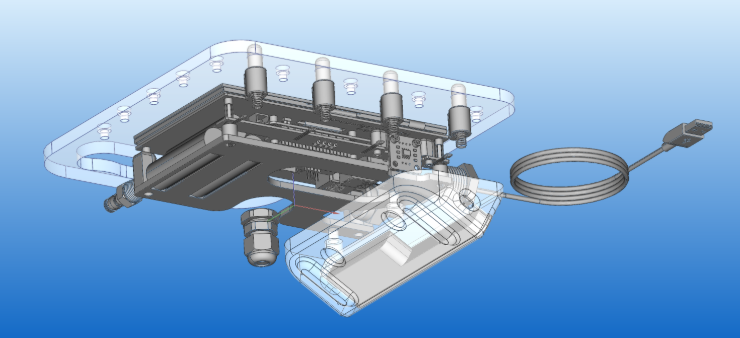

上圖就是整個項目的系統方案,也很好理解,就不過多贅述了。

SJA100就是CAN控制器;

VP230就是CAN收發器。

PS:代碼在上訴鏈接中。

4、liteCAN

https://github.com/WangXuan95/liteCAN

基于 FPGA 的輕量級CAN總線控制器

此項目實現的是CAN控制器,CAN收發器還是需要外掛。

簡介CAN總線作為工業和汽車領域最常用的通信總線,具有拓撲結構簡潔、可靠性高、傳輸距離長等優點。CAN總線的非破壞性仲裁機制依賴于幀ID,CAN2.0A和CAN2.0B分別規定了11bit-ID(短ID) 的標準幀和29bit-ID(長ID) 的擴展幀,另外,還有遠程幀這種數據請求機制。關于CAN總線的更多知識可以參考這個科普文章。

CAN總線的復雜機制決定了控制器設計的復雜性。本庫實現了一個輕量化但完備的CAN控制器,特點如下:

本地ID可固定配置為任意短ID。

發送 : 僅支持以本地ID發送數據長度為4Byte的幀。

接收 : 支持接收短ID或長ID的幀,接收幀的數據長度沒有限制 (即支持 0~8Byte ) 。

接收幀過濾 : 可針對短ID和長ID獨立設置過濾器,只接收和過濾器匹配的數據幀。

自動響應遠程幀 : 當收到的遠程幀與本地ID匹配時,自動將發送緩存中的下一個數據發送出去。若緩存為空,則重復發送上次發過的數據。

平臺無關 :純 RTL 編寫 (SystemVerilog),可以在 Altera 和 Xilinx 等各種 FPGA 上運行。

設計文件說明

設計相關的4個文件在 RTL 文件夾中,各文件功能如下表。你只需將以上4個文件包含進工程,就可以調用can_top.sv進行更高層次的CAN通信業務的二次開發。

此項目非常完整,項目由中文說明,完備的TB及測試方案。

5、CAN-fpga

https://github.com/AlxyF/CAN-fpga

項目沒有任何介紹,看文件結構,是基于Quartus II建立的,結構和上一項目完全沒什么區別。整個項目應該是完備的,有興趣可以看看。

6、sja1000

https://github.com/zhaotliang/sja1000

這個就是Verilog編寫的外掛SJA100的驅動程序,這里就不過多介紹了。

7、Click_MCP25625

https://github.com/MikroElektronika/Click_MCP25625

這是MCP25625(控制器+收發器集合)的SPI驅動(ARM單片機的)。

https://github.com/UberLambda/CANnuccia

這個項目和這個功能一樣,就不展開描述了。

USB-CAN(調試利器)因為本期沒幾個開源項目,所以這里在推薦幾個開源的USB-CAN方案,大部分都是可以直接打板使用的。

一、stm32f0 + CAN收發器TJA1051/3

https://canable.io/

https://codechina.csdn.net/mirrors/HubertD/candleLight?utm_source=csdn_github_accelerator

https://github.com/HubertD/candleLight/blob/master/export/v1.1/pdf/candleLight-v1.1.pdf

ta有完全開源的軟硬件及上位機支持,支持windos和linux Stock can并且都免驅哦。且支持Python。

上述的方案某寶上也有成品。

二、KS22方案

http://bbs.eeworld.com.cn/thread-491860-1-1.html

相關文檔及上位機:

三、open-usb-can

https://github.com/fabiobaltieri/open-usb-can

文檔很完備。

該項目是基于 ATMega32U2 和 MCP2515 SPI CANBus 控制器的 USB 轉 CANBus 接口。

最后,還是感謝各個大佬開源的項目,讓我們受益匪淺。后面有什么感興趣方面的項目,大家可以在后臺留言或者加微信留言,今天就到這,我是爆肝的碎碎思,期待下期文章與你相見。

責任編輯:haq

-

FPGA

+關注

關注

1660文章

22412瀏覽量

636328 -

CAN

+關注

關注

59文章

3067瀏覽量

472748 -

通信

+關注

關注

18文章

6389瀏覽量

140047

原文標題:優秀的 Verilog/FPGA開源項目介紹(七)- CAN通信

文章出處:【微信號:Open_FPGA,微信公眾號:OpenFPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

FPGA 入門必看:Verilog 與 VHDL 編程基礎解析!

開源鴻蒙項目順利孵化畢業

開源鴻蒙項目達成開源孵化目標順利畢業

開源鴻蒙和開源歐拉成為開放原子開源基金會首批畢業項目

【開源FPGA硬件】硬件黑客集結:開源FPGA開發板測評活動全網火熱招募中......

硬件黑客集結:開源FPGA開發板測評活動全網火熱招募中......

如何利用Verilog HDL在FPGA上實現SRAM的讀寫測試

開源FPGA硬件|FPGA LAYOUT評審,紫光同創定制公仔派送中

火爆開發中 | 開源FPGA硬件板卡,硬件第一期發布

RT-Thread榮獲2025優秀開源項目 | 新聞速遞

開源FPGA硬件,核心開發者招募中......

【開源分享】:開源小巧的FPGA開發板——Icepi Zero

擁抱開源!一起來做FPGA開發板啦!

FPGA Verilog HDL語法之編譯預處理

Open Echo:一個開源的聲納項目

Verilog/FPGA開源項目介紹

Verilog/FPGA開源項目介紹

評論