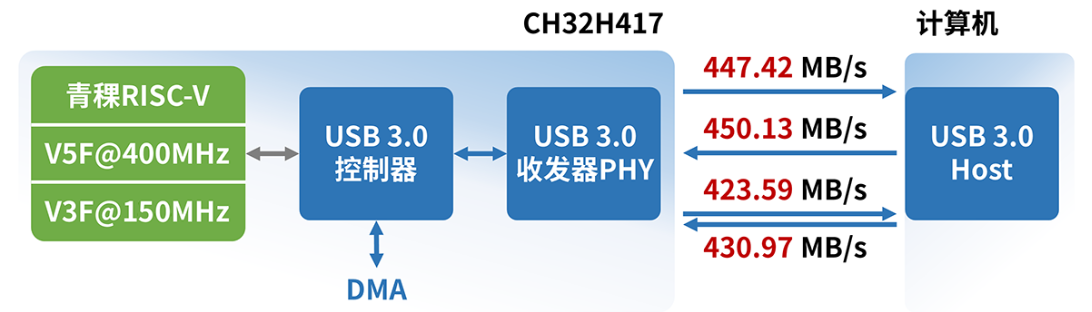

今天開(kāi)始將會(huì)通過(guò)4~5篇文章介紹FPGA和USB3.0通信的相關(guān)知識(shí),這其實(shí)是《FPGA和外圍接口(繼續(xù)更新)基于FPGA的網(wǎng)口通信設(shè)計(jì)》后續(xù)。PCIe也在籌備中。

完成后也是《Xilinx 7系列FPGA入門(mén)級(jí)圖像處理-完整版V1》初、中級(jí)篇的開(kāi)始,圖像處理部分也會(huì)通過(guò)攝像頭前端算法(主要ISP)和后端算法組成,最后應(yīng)該會(huì)形成一個(gè)初級(jí)工業(yè)UVC攝像頭和IPC,平臺(tái)還沒(méi)選定(不知道有沒(méi)有贊助,哈哈),算法基本驗(yàn)證完畢。

USB3.0介紹

總線、接口和協(xié)議

這里首先提幾個(gè)概念,大家應(yīng)該常見(jiàn)到:

USB3.0協(xié)議

USB3.0接口

USB3.0總線

是不是很懵逼?

其實(shí)理解了這幾個(gè)概念,對(duì)于USB的具體協(xié)議就可以有得放矢,不需要看整個(gè)復(fù)雜又冗長(zhǎng)的協(xié)議,針對(duì)自己的崗位去選擇。

總線是一組傳輸通道,是各種邏輯器件構(gòu)成的傳輸數(shù)據(jù)的通道,一般由由數(shù)據(jù)線、地址線、控制線等構(gòu)成。接口是一種連接標(biāo)準(zhǔn),又常常被稱(chēng)之為物理接口。協(xié)議就是傳輸數(shù)據(jù)的規(guī)則。

我們通常說(shuō)的USB,既可以是USB信號(hào),也可以是USB接口、USB總線,還可以是USB協(xié)議。之所以這么復(fù)雜,主要原因就是每個(gè)人對(duì)概念認(rèn)知的差異。舉個(gè)簡(jiǎn)單的例子,USB總線說(shuō)的是一組傳輸通道,而USB接口是一種連接標(biāo)準(zhǔn),兩者之間的關(guān)系就是USB接口的設(shè)備都要通過(guò)USB總線來(lái)進(jìn)行通信,而USB總線上走的設(shè)備并不全是USB接口的,像集成USB聲卡,走的就是USB總線,但是沒(méi)有走USB接口。在這里USB總線提供了一種通道,這個(gè)通道上可以有不同的符合這種通道要求的接口設(shè)備或信號(hào)(USB信號(hào)或Audio信號(hào))。

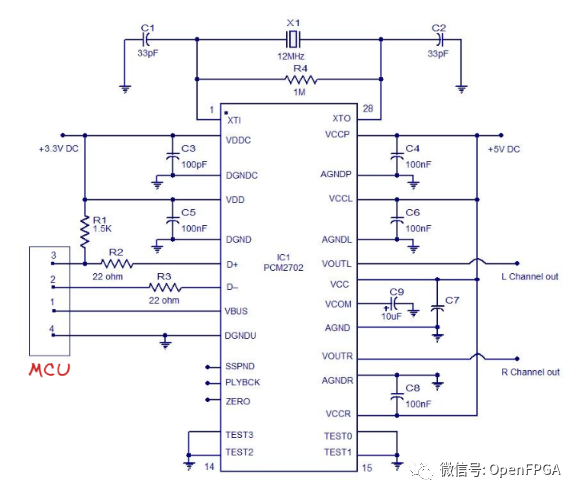

USB板載聲卡

對(duì)于USB聲卡,外置聲卡時(shí)走的就是USB接口,板載聲卡時(shí)時(shí)走的USB總線而不包含USB接口(物理層滿(mǎn)足要求即可)。

所以總結(jié)一下:

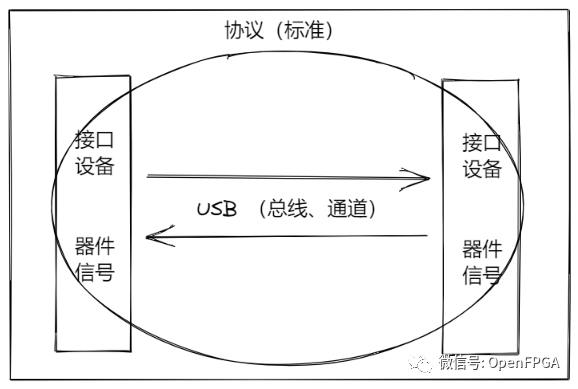

協(xié)議即總體框架,定義接口設(shè)備、器件及信號(hào)、總線及通道之間需要滿(mǎn)足的關(guān)系,即要實(shí)現(xiàn)信號(hào)的傳輸,所有這些組成成員必須通力合作,各自滿(mǎn)足協(xié)議要求的各種必要條件。

對(duì)于USB,下圖可以說(shuō)明這三者關(guān)系:

通過(guò)上面的分析,后面會(huì)在簡(jiǎn)單介紹USB3.0中規(guī)定的幾個(gè)重要方面。

USB3.0的分層機(jī)制

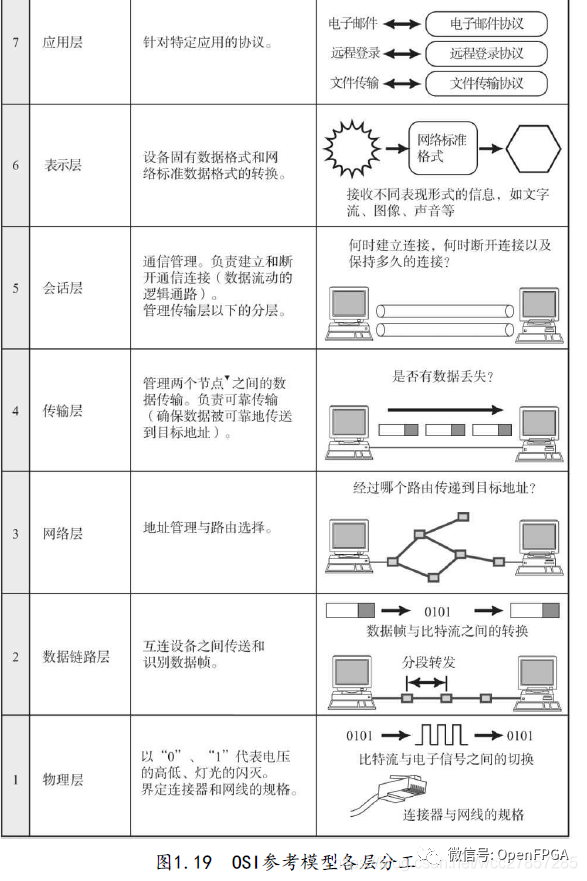

大家都知道PCIe具有三層結(jié)構(gòu)(事務(wù)層(Transaction Layer),數(shù)據(jù)鏈路層(Data Link Layer)和物理層(Physical Layer)),TCP/IP五層結(jié)構(gòu)(物理層、數(shù)據(jù)鏈路層、網(wǎng)絡(luò)層、傳輸層、應(yīng)用層),為什么復(fù)雜協(xié)議都具有分層結(jié)構(gòu)呢?

這個(gè)由來(lái)主要來(lái)源于OSI五層參考模型(例說(shuō)七層OSI參考模型)。

即使簡(jiǎn)單的RS232也是遵守上面的分層結(jié)構(gòu),只不過(guò)RS232只規(guī)定了物理層,所以現(xiàn)實(shí)中很少有人用分層結(jié)構(gòu)進(jìn)行分析。

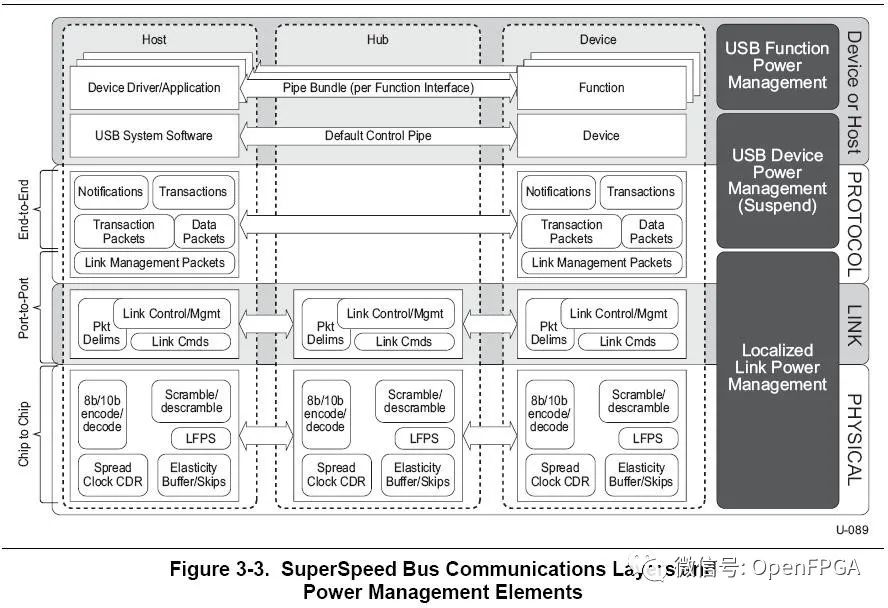

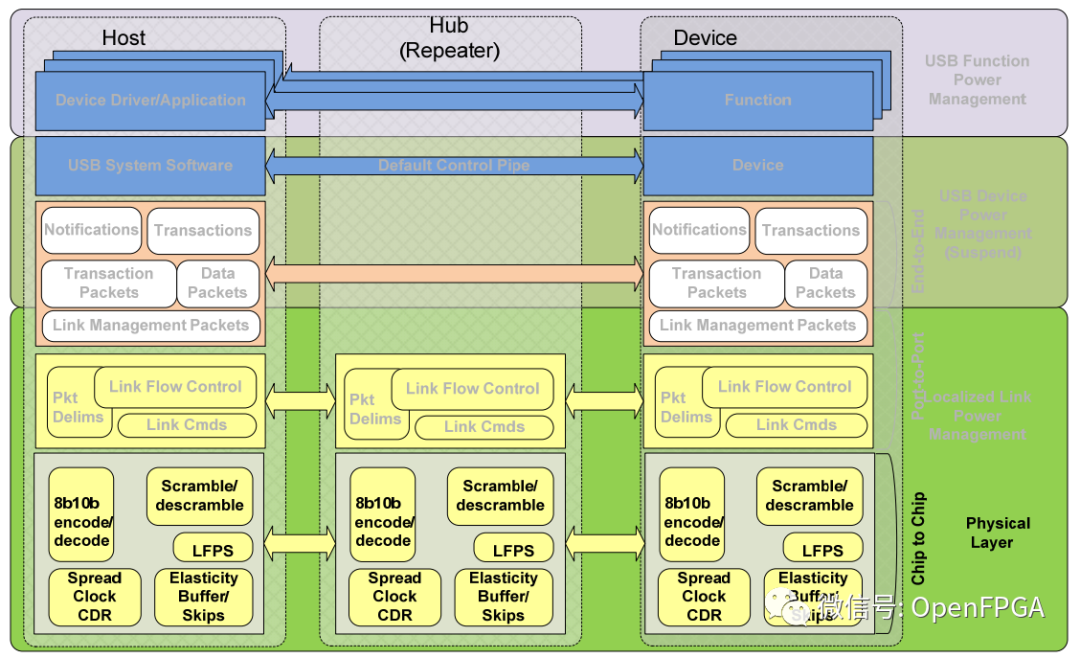

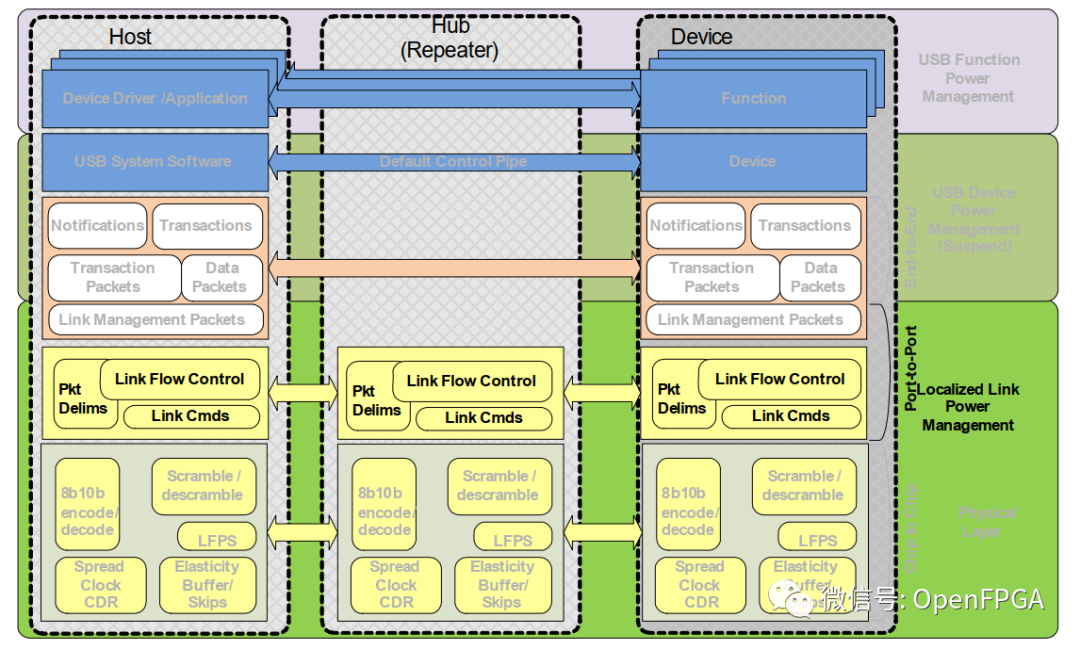

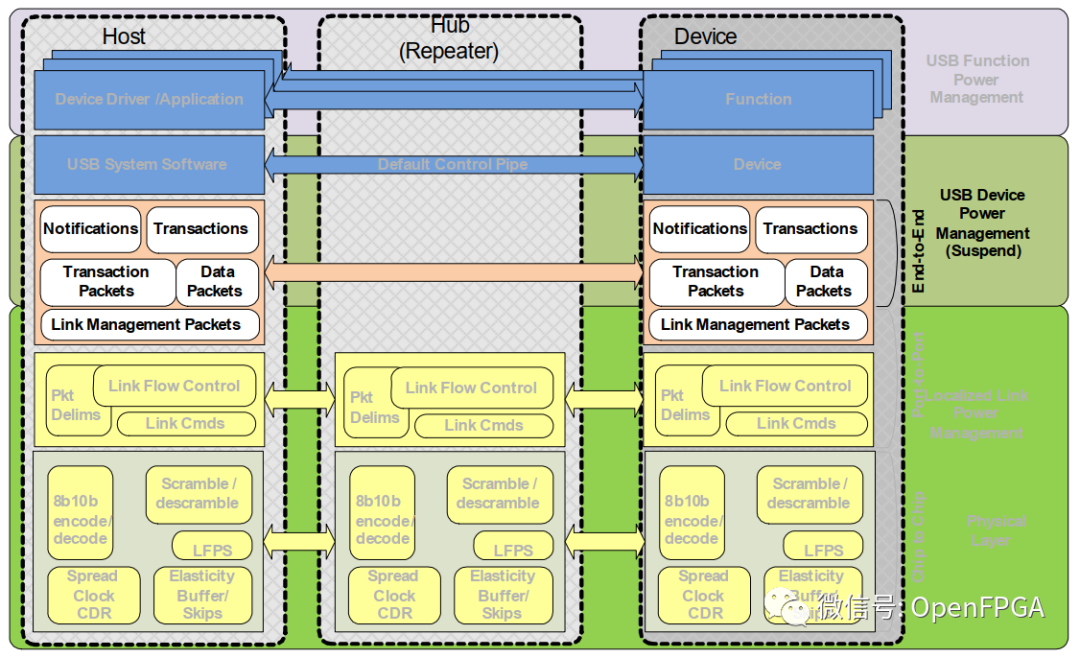

USB3.0的分層機(jī)制其實(shí)和PCIe類(lèi)似(協(xié)議層(Protocol Layer),鏈路層(Link Layer)和物理層(Physical Layer)),從某種意義上看,可以把USB3.0看做是PCIe變形版本。下圖是分層的通訊結(jié)構(gòu):

這種分層結(jié)構(gòu)即方便標(biāo)準(zhǔn)化,又方便擴(kuò)展,所以現(xiàn)今大部分協(xié)議都遵循OSI參考模型,希望大家可以理解一下這個(gè)模型(推薦的文章中有很多形象的解釋?zhuān)?/p>

以上部分解釋包含了個(gè)人理解,為了通俗易懂,有些表述不是很準(zhǔn)確,希望大家留言交流,下面就很俗套的簡(jiǎn)單講解官方的文檔了。

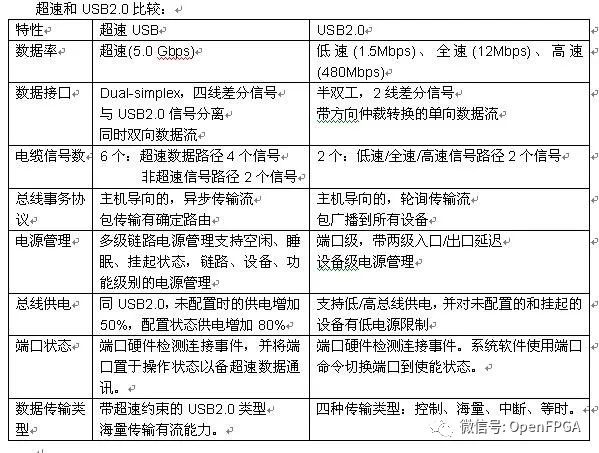

USB3.0 與USB2.0的特性比較

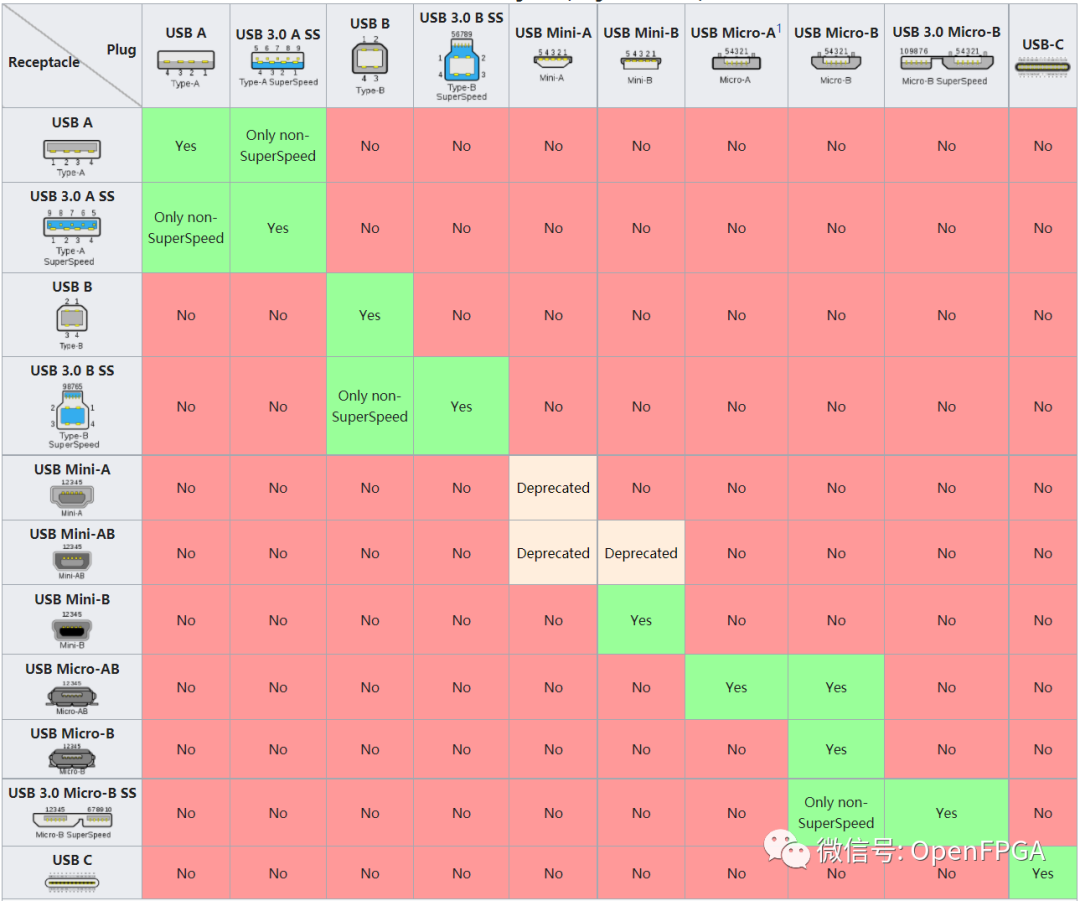

硬件接口

物理層

高亮顯示部分:

本層主要定義了高速組件之間互操作性所需的電氣層參數(shù)。

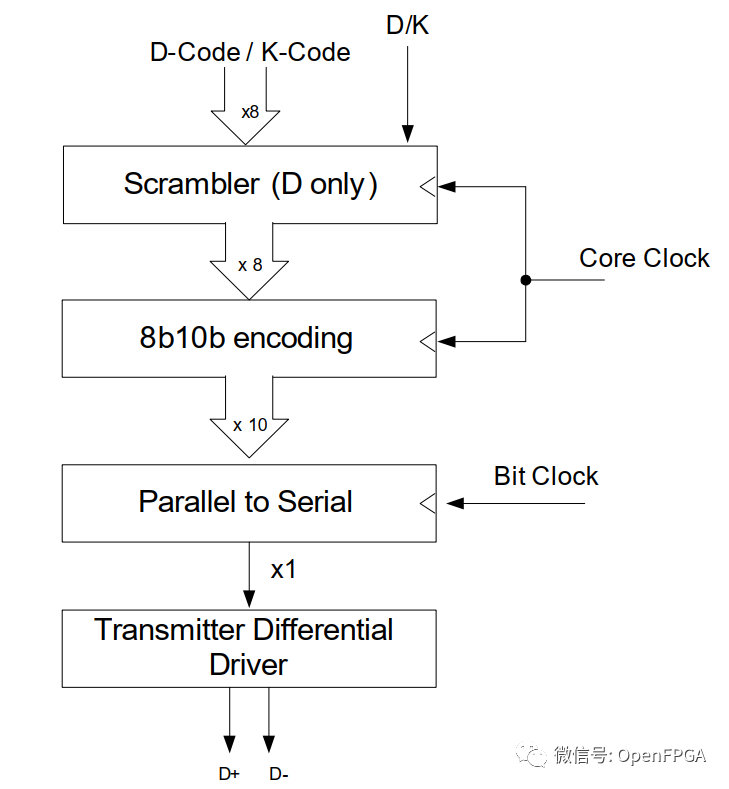

物理層Tx框圖

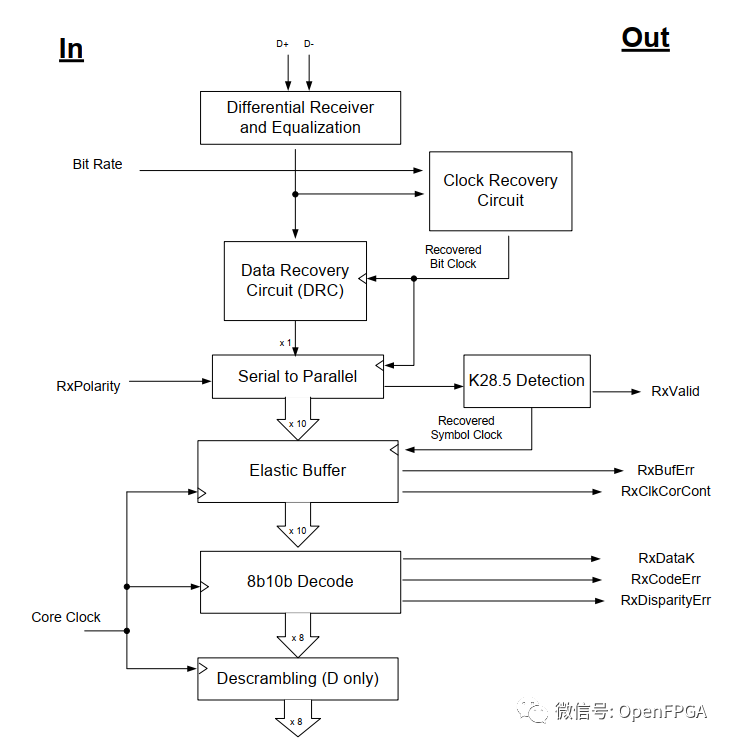

物理層Rx框圖

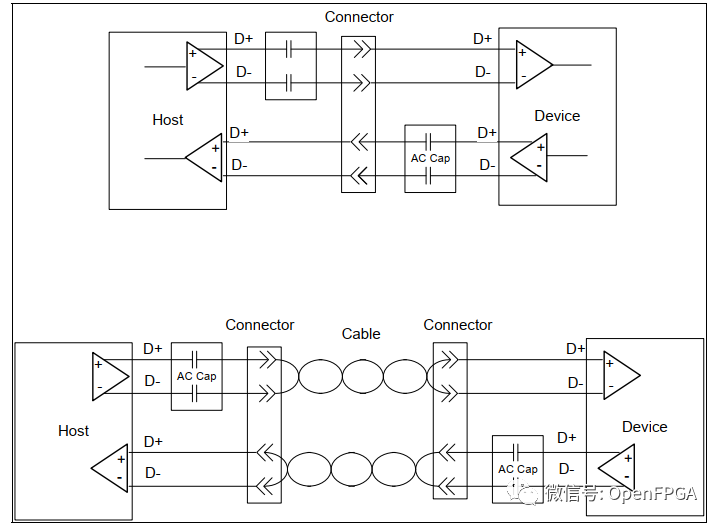

不帶電纜(頂部)和帶電纜(底部)的通道示意圖

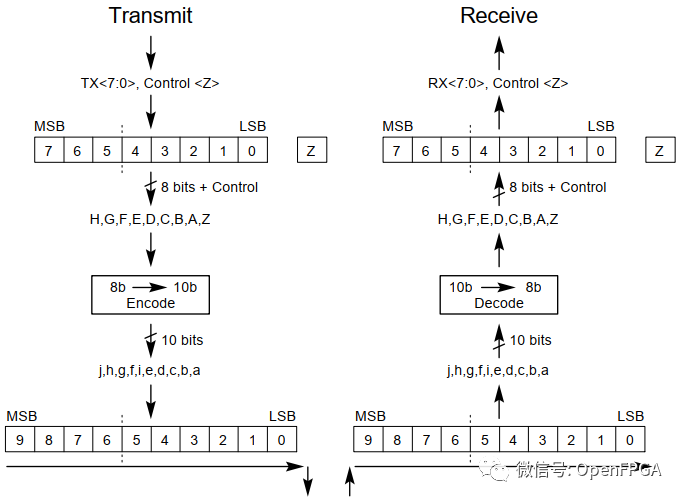

USB3.0使用8b/10b傳輸代碼。該傳輸代碼的定義與ANSI X3.230-1994(也稱(chēng)為ANSI INCITS 230-1994)第11條中規(guī)定的定義相同。

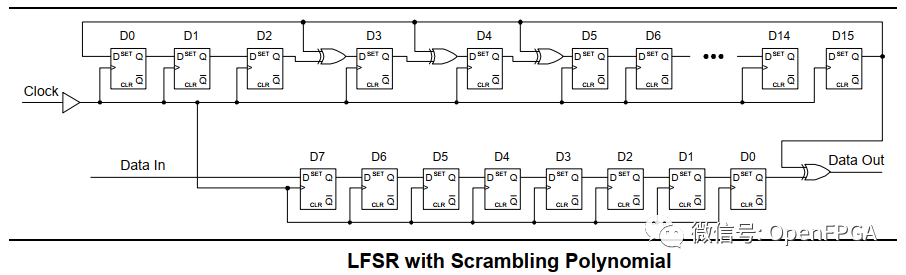

加擾功能使用線性反饋移位寄存器(LFSR)實(shí)現(xiàn)。在發(fā)送端,加擾應(yīng)用于8b/10b編碼之前的字符。在接收端,對(duì)8b/10b解碼后的字符應(yīng)用解擾。無(wú)論何時(shí)發(fā)送或接收COM符號(hào),LFSR都會(huì)重置。

以上就是物理層大致的規(guī)定,詳情請(qǐng)見(jiàn)《USB3.0協(xié)議規(guī)范(英文完整版)(第六節(jié))》。

Link Layer鏈路層

高亮顯示部分:

Link Layer鏈路層主要包括:

?數(shù)據(jù)包幀

?鏈路命令

?鏈路管理和流量控制

?鏈路錯(cuò)誤規(guī)則/恢復(fù)

?重置

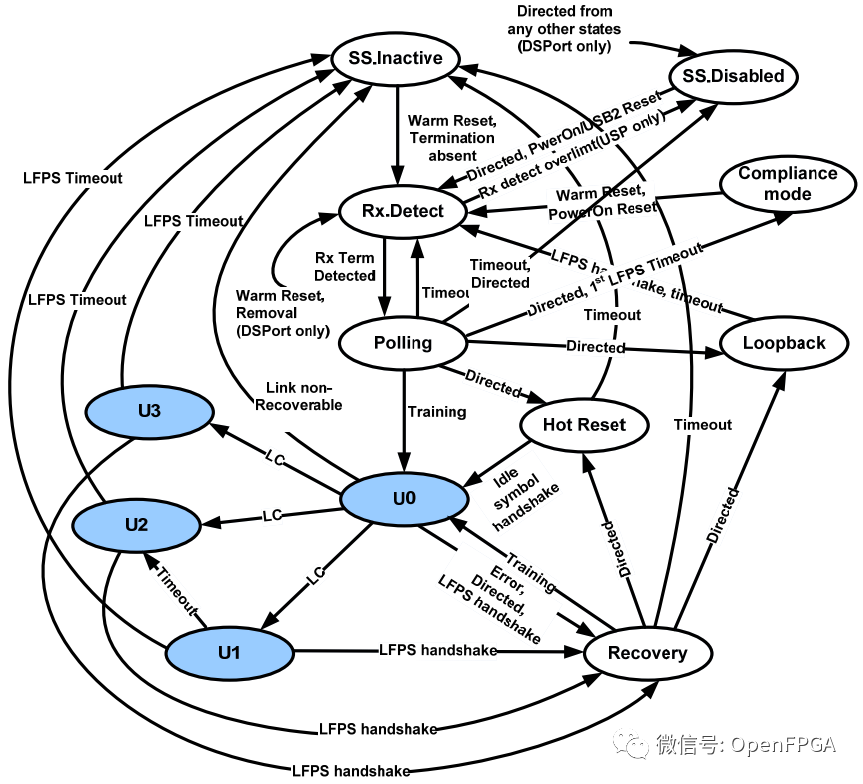

?鏈路狀態(tài)機(jī)描述

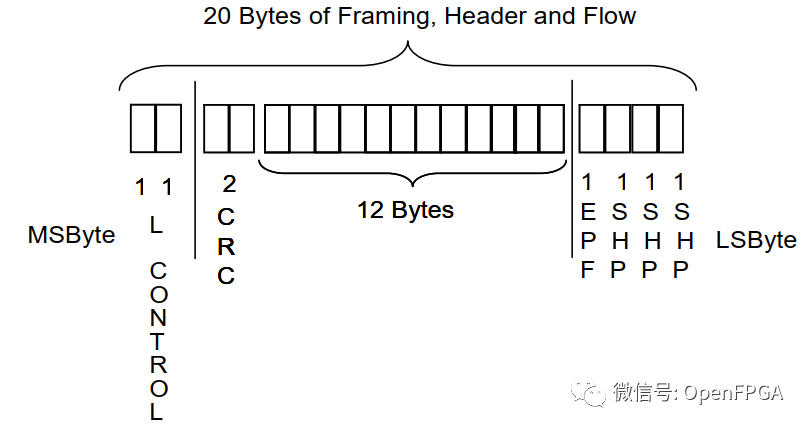

具有幀符號(hào)、CRC-16和鏈路控制字的分組報(bào)頭

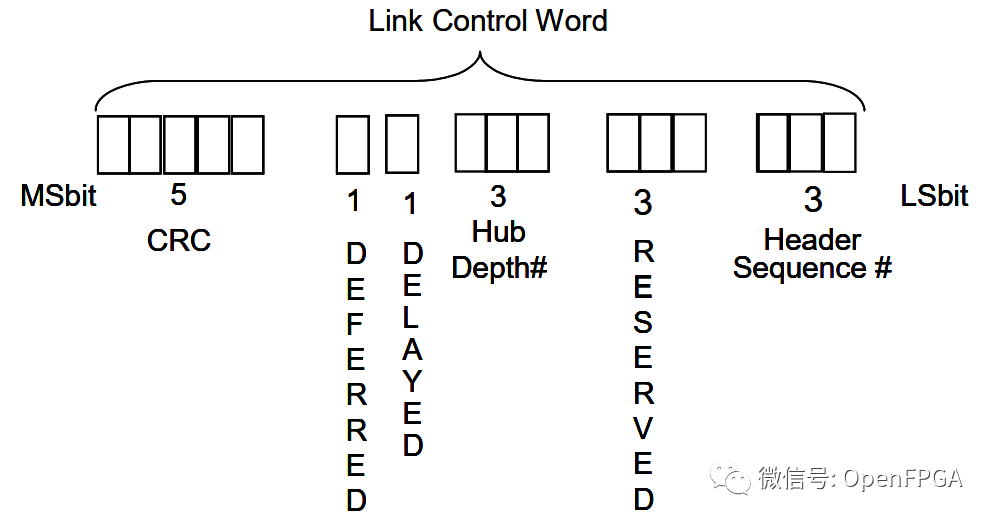

鏈接控制字

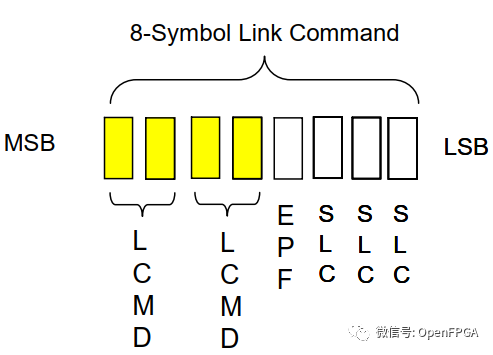

鏈接命令結(jié)構(gòu)

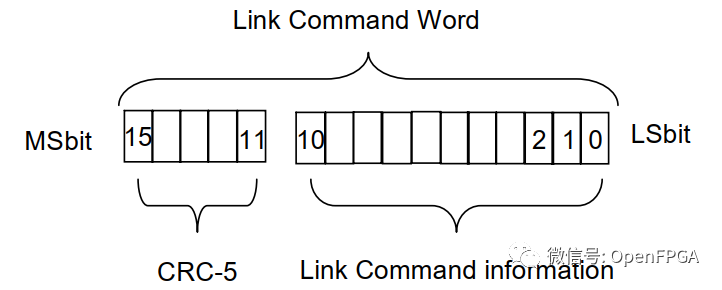

鏈接命令字結(jié)構(gòu)

鏈路訓(xùn)練和狀態(tài)機(jī)的狀態(tài)圖

協(xié)議層

高亮顯示部分:

協(xié)議層主要包括:

?數(shù)據(jù)包類(lèi)型

?數(shù)據(jù)包的格式

?對(duì)主機(jī)和設(shè)備發(fā)送的數(shù)據(jù)包的預(yù)期響應(yīng)

?描述了四種USB 3.0事務(wù)類(lèi)型

?支持批量傳輸類(lèi)型的流式傳輸支持

?設(shè)備/主機(jī)可能接收/發(fā)送的各種響應(yīng)和數(shù)據(jù)包的定時(shí)參數(shù)

整個(gè)協(xié)議層非常復(fù)雜,數(shù)據(jù)包就差不多十幾種類(lèi)型,所以這里就不過(guò)多介紹了。

編輯:jq

-

主機(jī)

+關(guān)注

關(guān)注

0文章

1053瀏覽量

36741 -

RS232

+關(guān)注

關(guān)注

13文章

876瀏覽量

98293 -

PCIe

+關(guān)注

關(guān)注

16文章

1460瀏覽量

88402 -

數(shù)據(jù)包

+關(guān)注

關(guān)注

0文章

269瀏覽量

25594

原文標(biāo)題:FPGA和USB3.0通信-USB3.0協(xié)議介紹

文章出處:【微信號(hào):Open_FPGA,微信公眾號(hào):OpenFPGA】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

USB3.0接口轉(zhuǎn)換高性能圖像傳感和數(shù)據(jù)采集方案

PL27A1超高速USB3.0數(shù)據(jù)對(duì)拷線芯片資料

基于FPGA和USB3.0通信的UVC攝像機(jī)設(shè)計(jì)方案

FPGA和USB3.0通信-USB3.0協(xié)議簡(jiǎn)介

FPGA和USB3.0通信-USB3.0協(xié)議簡(jiǎn)介

評(píng)論