2.3DIC集成技術(shù)簡介

在2.3DIC集成工藝中,精細金屬線寬/線距(L/S)重分布層(RDL)基板(或有機轉(zhuǎn)接板)與積層封裝基板或高密度互連(HDI)板采用分開制造的方式,兩者完成各自制備后,通過焊點實現(xiàn)互連,并采用底部填充料進行保護,最終形成混合基板結(jié)構(gòu)。得益于臨時玻璃晶圓/面板的輔助制造工藝,精細金屬L/S基板能夠?qū)崿F(xiàn)2μm的線寬/線距規(guī)格,同時保持較高的生產(chǎn)良率。正是這種工藝優(yōu)勢,使得2.3DIC集成的互連密度高于2.1DIC集成。

- 專欄中科院半導(dǎo)體所

- 1天前

- 177

- 0

- 0

你常買的晶振,是怎么生產(chǎn)出來的呢

在電子設(shè)備的“心臟”深處,晶振如同精準的節(jié)拍器,為各類電路提供穩(wěn)定的時鐘信號。它看似簡單,實則凝聚著精密的工藝與科學(xué)原理。那么,這顆小小的元件究竟是如何從實驗室的理論模型蛻變?yōu)殡娮酉到y(tǒng)的核心呢?讓我們跟隨其生產(chǎn)流程,揭開這制造奧秘。一、原材料的“基因優(yōu)化”:石英晶體的誕生密碼晶振的核心是石英晶體,其本質(zhì)為高純度的二氧化硅(SiO?)。生產(chǎn)始于對石英原料的嚴苛

- 企業(yè)TKD泰晶科技

- 4天前

- 167

- 0

- 0

深度解析三星移動SoC先進封裝技術(shù)

在當(dāng)今競爭高度激烈的半導(dǎo)體市場中,移動應(yīng)用處理器(AP)被要求在愈發(fā)受限的裝配空間內(nèi)持續(xù)實現(xiàn)性能提升。隨著智能手機形態(tài)不斷向輕薄化演進、高性能計算需求的增長以及端側(cè)AI應(yīng)用的普及,使得更高的功耗被壓縮在更小的體積之中,進而導(dǎo)致功率密度上升、發(fā)熱問題加劇。同時,消費者對更長續(xù)航以及更輕薄機身的期待不斷提高。由此,移動AP的開發(fā)已不再局限于性能的漸進式提升,而是需通過結(jié)構(gòu)層面的演進,實現(xiàn)對有限內(nèi)部空間的更高效利用。

- 專欄三星半導(dǎo)體和顯示官方

- 6天前

- 516

- 0

- 0

集成電路制造中薄膜生長工藝的發(fā)展歷程和分類

薄膜生長是集成電路制造的核心技術(shù),涵蓋PVD、CVD、ALD及外延等路徑。隨技術(shù)節(jié)點演進,工藝持續(xù)提升薄膜均勻性、純度與覆蓋能力,支撐銅互連、高k柵介質(zhì)及應(yīng)變器件發(fā)展。未來將聚焦低溫沉積、三維結(jié)構(gòu)適配與新材料集成,實現(xiàn)性能與可靠性的協(xié)同提升。

- 專欄中科院半導(dǎo)體所

- 9天前

- 376

- 0

- 0

集成電路制造工藝中的刻蝕技術(shù)介紹

本文系統(tǒng)梳理了刻蝕技術(shù)從濕法到等離子體干法的發(fā)展脈絡(luò),解析了物理、化學(xué)及協(xié)同刻蝕機制差異,闡明設(shè)備與工藝演進對先進制程的支撐作用,并概述國內(nèi)外產(chǎn)業(yè)格局,體現(xiàn)刻蝕在高端芯片制造中的核心地位與技術(shù)挑戰(zhàn)。

- 專欄中科院半導(dǎo)體所

- 9天前

- 456

- 0

- 0

通過特定方法驗證T2PAK封裝散熱設(shè)計的有效性

盡管這些方案能有效降低PCB熱阻,但因需增加額外的制造工序而成本較高。相比之下,頂面散熱的T2PAK封裝可直接通過器件頂部高效散熱,無需額外的高成本制造工藝。這些研究結(jié)果進一步驗證了T2PAK散熱設(shè)計的有效性:通過優(yōu)化TIM壓縮量、機械夾緊結(jié)構(gòu)及選配均熱器,即可在緊湊型高功率應(yīng)用中實現(xiàn)低結(jié)殼熱阻(Rth(j-f))和高效散熱。

- 專欄安森美

- 11天前

- 1333

- 0

- 0

晶體諧振器與晶體振蕩器:從原理到應(yīng)用的深度解析

在電子系統(tǒng)中,時鐘信號是系統(tǒng)運行的“心跳”,而晶體諧振器與晶體振蕩器則是生成這一“心跳”的核心元件。盡管兩者均基于石英晶體的壓電效應(yīng),但它們在結(jié)構(gòu)、功能和應(yīng)用場景上存在本質(zhì)差異。本文將從原理、特性、應(yīng)用及選型策略四個維度,系統(tǒng)解析兩者的區(qū)別。一、定義與組成:被動元件與有源模塊的本質(zhì)差異?晶體諧振器(CrystalResonator)?晶體諧振器是純粹的被動元

- 企業(yè)TKD泰晶科技

- 11天前

- 502

- 0

- 0

原半導(dǎo)體“倒裝芯片(Flip - Chip)”焊界面退化的詳解;

【博主簡介】本人“ 愛在七夕時 ”,系一名半導(dǎo)體行業(yè)質(zhì)量管理從業(yè)者,旨在業(yè)余時間不定期的分享半導(dǎo)體行業(yè)中的:產(chǎn)品質(zhì)量、失效分析、可靠性分析和產(chǎn)品基礎(chǔ)應(yīng)用等相關(guān)知識。常言:真知不問出處,所分享的內(nèi)容如有雷同或是不當(dāng)之處,還請大家海涵。當(dāng)前在各網(wǎng)絡(luò)平臺上均以此昵稱為ID跟大家一起交流學(xué)習(xí)! 一講到“倒裝芯片(Flip-Chip,簡稱:FC)”,相信同行的朋友們并不陌生,它是一種無引腳結(jié)構(gòu)的芯片封裝技術(shù)。一般含有電路單元,它將

- 專欄愛在七夕時

- 12天前

- 3616

- 0

- 0

安森美T2PAK封裝功率器件換流回路設(shè)計建議

T2PAK應(yīng)用筆記重點介紹T2PAK封裝的貼裝及其熱性能的高效利用。內(nèi)容涵蓋以下方面:T2PAK封裝詳解:全面說明封裝結(jié)構(gòu)與關(guān)鍵規(guī)格參數(shù);焊接注意事項:闡述實現(xiàn)可靠電氣連接的關(guān)鍵焊接注意事項;濕度敏感等級(MSL)要求:明確器件在處理與存儲過程中的防潮防護規(guī)范;器件貼裝指南:提供器件貼裝的最佳實踐建議。我們已經(jīng)介紹了

- 專欄安森美

- 26天前

- 928

- 0

- 0

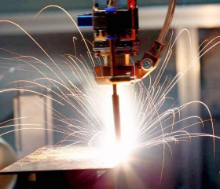

錫金結(jié)合的熔點奧秘:精密焊接領(lǐng)域的熱控技術(shù)核心與應(yīng)用

在微電子封裝、軍工電子、精密醫(yī)療設(shè)備等高端制造領(lǐng)域,錫與金的結(jié)合焊接是保障產(chǎn)品可靠性的關(guān)鍵工藝環(huán)節(jié)。純金熔點高達 1064℃,純錫熔點為 232℃,而二者按特定比例形成的合金(如經(jīng)典的金錫共晶合金)熔點僅為 280℃左右,遠低于兩種純金屬的熔點。這種 “低熔點效應(yīng)” 并非偶然,而是合金晶體結(jié)構(gòu)、原子相互作用與熱力學(xué)規(guī)律共同作用的結(jié)果。這一特性不僅解決了精密元器件焊接中的熱損傷難題,更成為高端精密焊接技術(shù)發(fā)展的核心支撐。本文將從科學(xué)原理、應(yīng)用價值、技術(shù)適配三個維度,深度解析錫金結(jié)合的熔點奧秘,探討其在精密焊接領(lǐng)域的技術(shù)應(yīng)用,以及大研智造激光錫球焊設(shè)備如何精準匹配這一特殊焊接需求。

- 大研智造

- 1月前

- 547

- 0

- 0

初入職場:TCXO與OCXO的區(qū)別解析

作為一名初入電子行業(yè)的職場新人,面對技術(shù)文檔中頻繁出現(xiàn)的TCXO(溫度補償晶體振蕩器)和OCXO(恒溫晶體振蕩器)術(shù)語,你是否感到困惑?這兩種晶體振蕩器雖然都用于提供穩(wěn)定的時鐘信號,但在工作原理、性能特點和應(yīng)用場景上存在顯著差異。本文將為你詳細解析它們的區(qū)別,助你快速掌握關(guān)鍵知識。一、工作原理:主動恒溫vs.被動補償TCXO和OCXO的核心區(qū)別在于應(yīng)對溫度變

- 企業(yè)TKD泰晶科技

- 1月前

- 675

- 0

- 0

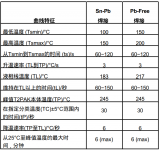

安森美T2PAK封裝功率器件貼裝方法

T2PAK應(yīng)用筆記重點介紹T2PAK封裝的貼裝及其熱性能的高效利用。內(nèi)容涵蓋以下方面:T2PAK封裝詳解:全面說明封裝結(jié)構(gòu)與關(guān)鍵規(guī)格參數(shù);焊接注意事項:闡述實現(xiàn)可靠電氣連接的關(guān)鍵焊接注意事項;濕度敏感等級(MSL)要求:明確器件在處理與存儲過程中的防潮防護規(guī)范;器件貼裝指南:提供器件貼裝的最佳實踐建議。第一篇介紹了T2PAK封裝基礎(chǔ)知識,本文將繼續(xù)介紹器件貼裝方法。

- 專欄安森美

- 1月前

- 1.1w

- 0

- 0

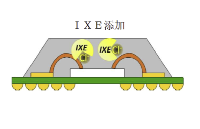

革命性突破!東亞合成IXE系列離子捕捉劑如何重塑電子封裝材料穩(wěn)定性

在高度精密化的現(xiàn)代電子制造業(yè)中,微小離子污染可能引發(fā)災(zāi)難性后果。東亞合成公司推出的IXE系列離子捕捉劑,正以其獨特的材料科學(xué)創(chuàng)新,為IC封裝和柔性電路板制造提供關(guān)鍵解決方案。

- 企業(yè)智美行科技

- 1月前

- 1408

- 0

- 0

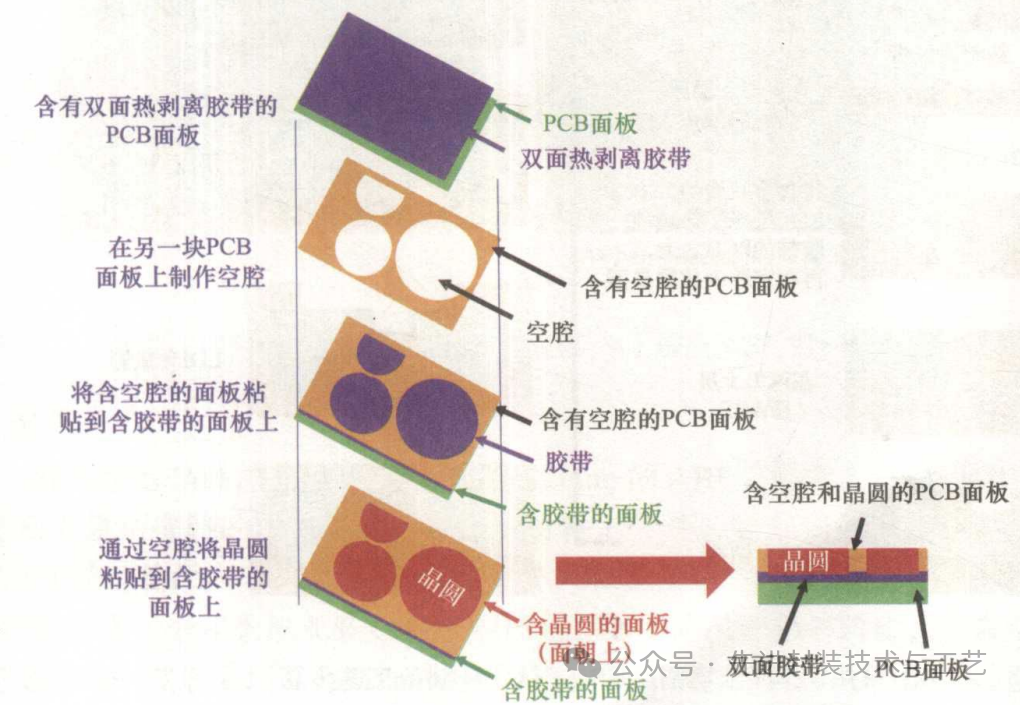

晶圓級扇出型封裝的三大核心工藝流程

在后摩爾時代,扇出型晶圓級封裝(FOWLP) 已成為實現(xiàn)異構(gòu)集成、提升I/O密度和縮小封裝尺寸的關(guān)鍵技術(shù)路徑。與傳統(tǒng)的扇入型(Fan-In)封裝不同,F(xiàn)OWLP通過將芯片重新排布在重構(gòu)晶圓上,利用塑封料(EMC) 擴展芯片面積,從而在芯片范圍之外提供額外的I/O連接空間。根據(jù)工藝流程的差異,F(xiàn)OWLP主要分為三大類:芯片先裝(Chip-First)面朝下、芯片先裝面朝上以及RDL先制。本文將深入剖析這三種工藝的具體流程、關(guān)鍵技術(shù)難點及優(yōu)劣勢對比。

- 專欄深圳市賽姆烯金科技有限公司

- 1月前

- 1010

- 0

- 0

晶振儲存指南

在電子設(shè)備中,晶振如同心臟般重要,它為電路提供穩(wěn)定的時鐘信號,確保設(shè)備精準運行。然而,晶振的儲存環(huán)境直接影響其性能和壽命,不當(dāng)?shù)膬Υ婵赡軐?dǎo)致頻率偏移、焊接困難甚至設(shè)備故障。本文將深入探討晶振的儲存方法,幫助您避免常見問題,確保晶振在關(guān)鍵時刻發(fā)揮最佳作用。一、晶振儲存的核心要素:溫度與濕度控制晶振對溫度和濕度極為敏感。溫度波動會改變晶體的物理特性,導(dǎo)致頻率穩(wěn)定

- 企業(yè)TKD泰晶科技

- 1月前

- 765

- 0

- 0

3D IC設(shè)計中的信號完整性與電源完整性分析

對更高性能和更強功能的不懈追求,推動半導(dǎo)體行業(yè)經(jīng)歷了多個變革時代。最新的轉(zhuǎn)變是從傳統(tǒng)的單片SoC轉(zhuǎn)向異構(gòu)集成先進封裝IC,包括3D IC。這項新興技術(shù)有望助力半導(dǎo)體公司延續(xù)摩爾定律。

- 專欄西門子EDA

- 1月前

- 1.2w

- 0

- 0

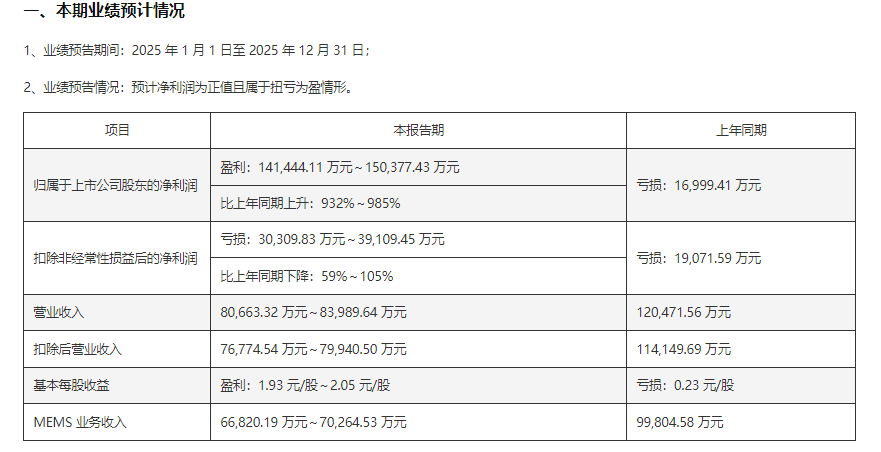

國產(chǎn)MEMS芯片代工龍頭企業(yè)賽微電子:預(yù)計2025年凈利潤達15億元,增長985%

? 1月27日,國產(chǎn)MEMS芯片代工龍頭企業(yè)賽微電子,披露業(yè)績預(yù)告,公司預(yù)計2025年歸母凈利潤14.1億元至15.0億元,同比增長932%至985%,較去年同期虧損1.70億元實現(xiàn)扭虧為盈;預(yù)計扣非凈虧損3.03億元至3.91億元,同比下降59%至105%;預(yù)計營業(yè)收入8.07億元至8.40億元,較去年同期有所下降。MEMS業(yè)務(wù)方面,本報告期預(yù)計營收為6.68~7.03億元,上年同期為9.98億元。 ? ? 報告期內(nèi),賽微科技公司營業(yè)收入、MEMS業(yè)務(wù)收入下降、歸屬于上市公司股東的凈利潤大幅增長的主要原

- 傳感器專家網(wǎng)

- 1月前

- 3217

- 0

- 0

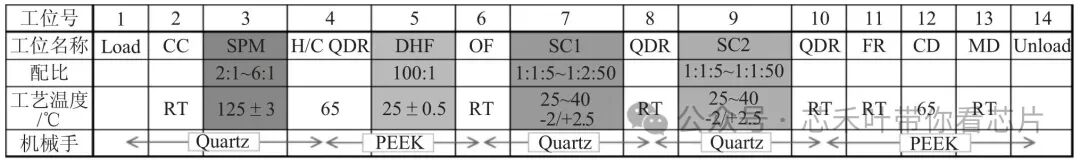

集成電路制造中常用濕法清洗和腐蝕工藝介紹

集成電路濕法工藝是指在集成電路制造過程中,通過化學(xué)藥液對硅片表面進行處理的一類關(guān)鍵技術(shù),主要包括濕法清洗、化學(xué)機械拋光、無應(yīng)力拋光和電鍍四大類。這些工藝貫穿于芯片制造的多個關(guān)鍵環(huán)節(jié),直接影響器件性能與良率。

- 專欄深圳市賽姆烯金科技有限公司

- 1月前

- 1732

- 0

- 0

半導(dǎo)體行業(yè)知識專題九:半導(dǎo)體測試設(shè)備深度報告

(一)測試設(shè)備貫穿半導(dǎo)體制造全流程半導(dǎo)體測試設(shè)備是集成電路產(chǎn)業(yè)鏈核心裝備,涵蓋晶圓測試、封裝測試及功能驗證等環(huán)節(jié)。半導(dǎo)體測試設(shè)備貫穿于集成電路制造的全生命周期,且因半導(dǎo)體生產(chǎn)流程極其復(fù)雜,為了防止壞品流入下一道高成本工序,測試必須分段進行,主要在晶圓制造后的CP測試與封裝后的FT測試兩大核心環(huán)節(jié)發(fā)揮決定性作用:CP測試(CircuitProbing/Wafe

- 企業(yè)漢通達

- 1月前

- 1761

- 0

- 0