【博主簡(jiǎn)介】本人“愛(ài)在七夕時(shí)”,系一名半導(dǎo)體行業(yè)質(zhì)量管理從業(yè)者,旨在業(yè)余時(shí)間不定期的分享半導(dǎo)體行業(yè)中的:產(chǎn)品質(zhì)量、失效分析、可靠性分析和產(chǎn)品基礎(chǔ)應(yīng)用等相關(guān)知識(shí)。常言:真知不問(wèn)出處,所分享的內(nèi)容如有雷同或是不當(dāng)之處,還請(qǐng)大家海涵。當(dāng)前在各網(wǎng)絡(luò)平臺(tái)上均以此昵稱為ID跟大家一起交流學(xué)習(xí)!

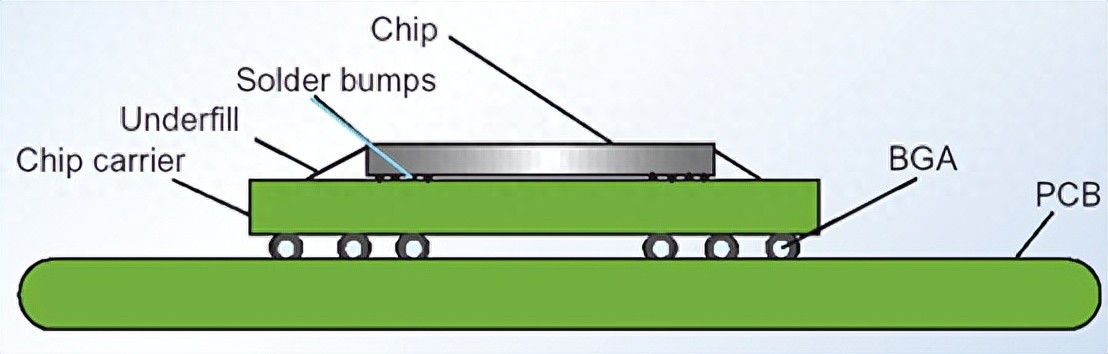

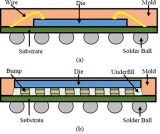

一講到“倒裝芯片(Flip-Chip,簡(jiǎn)稱:FC)”,相信同行的朋友們并不陌生,它是一種無(wú)引腳結(jié)構(gòu)的芯片封裝技術(shù)。一般含有電路單元,它將芯片有源面(即帶有電路的一面)朝下,通過(guò)凸點(diǎn)與基板直接連接,而不是傳統(tǒng)的引腳連接方式。其原理是在芯片的 I/O 焊盤上直接沉積,或者通過(guò) RDL 布線后沉積凸塊(包括錫鉛球、無(wú)鉛錫球、銅柱凸點(diǎn)及金凸點(diǎn)等),然后將芯片翻轉(zhuǎn),進(jìn)行加熱,使熔融的焊料與基板或框架相結(jié)合,將芯片的 I/O 扇出成所需求的封裝過(guò)程。

因?yàn)樾酒寡b(FC)焊工藝采用焊料凸點(diǎn)式的芯片鍵合,也稱為可控塌陷芯片連接,這種倒裝技術(shù)為微電路器件提供了一種高密度、低電感的導(dǎo)電路徑,芯片倒裝焊接由三部分組成:芯片表面的凸點(diǎn)下金屬層(UBM)、基板表面的頂層金屬層(TSM)、焊料球。芯片與焊料球的結(jié)合如圖所示、芯片倒裝(FC)焊位置如下圖所示:

而芯片表面的UBM 焊盤,由起著不同作用的三層金屬膜構(gòu)成:芯片焊盤表面的黏附層、焊料潤(rùn)濕層、氧化保護(hù)層。倒裝焊一般采用載流焊工藝,焊球通過(guò)固→液→固的變化,使焊料球牢固地與芯片鍵合在一起,典型的焊球尺寸是寬 100~250μm,高50~200μm。焊料球多采用PbSn、PbIn兩類焊料;UBM多層金屬結(jié)構(gòu)中,黏附/阻擋層采用Cr/CrCu或TiW 結(jié)構(gòu),潤(rùn)濕層采用Cu、Ni或Ag,氧化保護(hù)層采用Au;TSM金屬化層一般選擇Ti/Au。

在以上這種焊點(diǎn)相關(guān)界面(如 Under Bump Metallurgy (UBM) 和 Top Surface Metallurgy (TSM) 與焊料球界面等)出現(xiàn)性能下降的情況,主要表現(xiàn)為鍵合界面接觸電阻增大、鍵合強(qiáng)度下降以及在溫度循環(huán)條件下鍵合界面易發(fā)生開裂等問(wèn)題 時(shí),即芯片倒裝(FC)的焊界面退化,也是本章節(jié)要跟大家分享的主要內(nèi)容。

一、倒裝芯片(FC)焊界面退化的機(jī)理

因?yàn)樾酒寡b焊點(diǎn)在穩(wěn)態(tài)溫度條件下的失效,主要表現(xiàn)為Under Bump Metallurgy (UBM) 和Top Surface Metallurgy (TSM) 與焊料球界面處因金屬間化合物持續(xù)生長(zhǎng),所導(dǎo)致的鍵合界面接觸電阻增大及鍵合強(qiáng)度下降。此外,在溫度循環(huán)條件下,該鍵合界面也易發(fā)生開裂。此類失效機(jī)理與UBM/TSM的材料選擇、結(jié)構(gòu)設(shè)計(jì)、幾何尺寸、焊料成分、基板材料以及工作環(huán)境溫度密切相關(guān)。

1、金屬間化合物生長(zhǎng)

金屬間化合物的形成主要集中于UBM/TSM界面以及焊料體內(nèi)部。其形成機(jī)理源于再流焊工藝過(guò)程中界面處金屬原子的相互擴(kuò)散。具體而言,在進(jìn)行倒裝焊時(shí),芯片和基板上的大量金屬原子會(huì)溶解到液態(tài)焊料中。這些原子首先在UBM/TSM界面處形成初始的金屬間化合物層,其形成速率和厚度取決于基體金屬在液態(tài)焊料中的溶解度。當(dāng)焊料冷卻固化時(shí),焊料中過(guò)飽和的基體金屬會(huì)析出,在焊料內(nèi)部形成分散的金屬間化合物顆粒。因此,在再流焊過(guò)程中,若工藝控制不當(dāng),導(dǎo)致焊料與芯片、焊料與基板之間的金屬間擴(kuò)散過(guò)度,就會(huì)在UBM/TSM界面形成過(guò)厚的脆性金屬間化合物層,從而造成焊點(diǎn)性能退化,并為后續(xù)使用中界面處的開裂埋下隱患。

2、溫度循環(huán)影響

焊接溫度對(duì)倒裝焊料凸點(diǎn)的失效部位具有顯著影響。研究表明:對(duì)于PbSn倒裝鍵合凸點(diǎn),當(dāng)焊接溫度T=340℃時(shí),凸點(diǎn)裂紋傾向于出現(xiàn)在芯片側(cè)的UBM/焊料界面附近(見下圖左);而當(dāng)焊接溫度升高至T=365℃時(shí),裂紋則轉(zhuǎn)而出現(xiàn)在基板側(cè)的TSM/焊料界面附近(見下圖右)。這種失效部位的轉(zhuǎn)移,歸因于在更高溫度下,芯片側(cè)TSM界面的AuSn金屬間化合物會(huì)加速生長(zhǎng),導(dǎo)致該區(qū)域成為新的薄弱環(huán)節(jié)。

在影響芯片倒裝焊凸點(diǎn)可靠性的諸多因素中,Au元素的作用尤為關(guān)鍵。當(dāng)Au元素進(jìn)入PbSn焊料后,會(huì)迅速與Sn反應(yīng)形成Au/Sn金屬間化合物(如AuSn?),導(dǎo)致焊料脆化,進(jìn)而引發(fā)兩類主要問(wèn)題:

(1)脆性金屬間化合物厚度的增加,以及界面處Sn元素被大量消耗,共同導(dǎo)致焊點(diǎn)的機(jī)械性能顯著下降。

(2)在脆性金屬間化合物層附近,由于Sn的消耗會(huì)形成富Pb的軟質(zhì)區(qū),該區(qū)域在熱循環(huán)應(yīng)力作用下,極易成為裂紋萌生和擴(kuò)展的路徑。

二、倒裝芯片(FC)焊界面退化的影響因素

出現(xiàn)以上焊界面退化的主要影響因素有以下三點(diǎn):

1、材料相關(guān)因素

a. UBM/TSM材料

Under Bump Metallurgy (UBM) 和 Top Surface Metallurgy (TSM) 的材料選擇對(duì)焊界面退化影響顯著。不同的UBM/TSM材料在再流焊過(guò)程中,與焊料之間的金屬間化合物形成情況和性能不同,其材料特性決定了金屬間化合物的生長(zhǎng)速率、種類和分布,進(jìn)而影響鍵合界面的接觸電阻和強(qiáng)度。例如,某些UBM/TSM材料可能更容易與焊料形成脆性金屬間化合物層,導(dǎo)致焊點(diǎn)性能退化。

b. 焊料成分

焊料的成分決定了金屬間化合物的種類和形成過(guò)程。不同成分的焊料在再流焊過(guò)程中,基體金屬在液態(tài)焊料中的溶解度不同,原子擴(kuò)散和反應(yīng)情況也不同,從而影響金屬間化合物層的厚度和性能。合適的焊料成分可以控制金屬間化合物的生長(zhǎng),減少焊界面退化的風(fēng)險(xiǎn)。

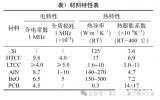

c. 基板材料

基板材料的熱膨脹系數(shù)等特性與芯片不匹配時(shí),會(huì)導(dǎo)致熱應(yīng)力產(chǎn)生。在工作環(huán)境溫度變化時(shí),熱膨脹系數(shù)的差異會(huì)加大芯片與基板之間的熱應(yīng)力失配,加速焊界面退化。同時(shí),基板材料的某些特性也可能影響金屬間化合物的形成和分布。

2、結(jié)構(gòu)與工藝因素

a. UBM/TSM結(jié)構(gòu)設(shè)計(jì)與幾何尺寸

UBM/TSM的結(jié)構(gòu)設(shè)計(jì)、幾何尺寸會(huì)影響金屬間化合物的形成和分布。合理的結(jié)構(gòu)設(shè)計(jì)和幾何尺寸可以控制金屬間化合物的析出位置和生長(zhǎng)方向,避免在UBM/TSM界面形成過(guò)厚的脆性金屬間化合物層。例如,特定的結(jié)構(gòu)設(shè)計(jì)可以使金屬原子在擴(kuò)散過(guò)程中更均勻地分布,減少局部金屬間化合物的過(guò)度生長(zhǎng)。

b. 焊接溫度與工藝控制

焊接溫度對(duì)倒裝焊料凸點(diǎn)的失效部位具有顯著影響。在再流焊過(guò)程中,若工藝控制不當(dāng),如焊接溫度過(guò)高或保溫時(shí)間過(guò)長(zhǎng),會(huì)導(dǎo)致焊料與芯片、焊料與基板之間的金屬間擴(kuò)散過(guò)度,從而在UBM/TSM界面形成過(guò)厚的脆性金屬間化合物層,造成焊點(diǎn)性能退化,并為后續(xù)使用中界面處的開裂埋下隱患。此外,焊接溫度的均勻性也會(huì)影響焊界面的質(zhì)量。

3、工作環(huán)境因素

工作環(huán)境溫度的變化,特別是溫度循環(huán),會(huì)產(chǎn)生熱應(yīng)力。溫度循環(huán)產(chǎn)生的應(yīng)變?cè)诼闫吔翘幾顬閲?yán)重,會(huì)加大基板和硅片之間熱膨脹系數(shù)嚴(yán)重失配造成的影響,使得鍵合界面易發(fā)生開裂。同時(shí),溫度循環(huán)也會(huì)加速金屬間化合物的生長(zhǎng),進(jìn)一步導(dǎo)致焊界面退化。

另外,因界面退化會(huì)導(dǎo)致芯片與基板之間的電氣連接可靠性下降,可能引發(fā)系統(tǒng)故障。因此,需通過(guò)改進(jìn)材料配方、優(yōu)化工藝參數(shù)等措施,降低退化風(fēng)險(xiǎn)。

三、倒裝芯片(FC)焊界面退化的解決措施

倒裝芯片焊界面退化的解決措施可歸納為以下四方面,結(jié)合工藝優(yōu)化、材料改進(jìn)和設(shè)備調(diào)整實(shí)現(xiàn):

1、激光加熱技術(shù)

激光 + 測(cè)溫同軸精準(zhǔn)控溫的倒裝芯片焊接技術(shù),能嚴(yán)格控制溫度曲線、保證凸點(diǎn)潤(rùn)濕均勻性,同時(shí)規(guī)避熱膨脹系數(shù)失配導(dǎo)致的應(yīng)力損傷、金屬間化合物(IMC)異常生長(zhǎng)及細(xì)間距凸點(diǎn)橋接等問(wèn)題,有助于減少焊界面退化的可能性。邁射科技半導(dǎo)體激光加熱技術(shù)采用激光、測(cè)溫同軸設(shè)計(jì),溫度探測(cè)響應(yīng)時(shí)間僅 1ms,能實(shí)時(shí)捕捉加工區(qū)域的溫度變化,避免溫度滯后導(dǎo)致的控溫偏差。

2、清洗工藝

倒裝芯片通過(guò)回流焊焊接在基板上后,因需用填充料對(duì)裸片進(jìn)行填充,所以需要對(duì)芯片和基材之間狹小空間里的助焊劑殘留物進(jìn)行清洗,以防止填充時(shí)出現(xiàn)分層、空洞和條紋等界面缺陷,為底部填充提供適當(dāng)?shù)臐?rùn)濕度,防止空洞產(chǎn)生,一定程度上保障焊界面的穩(wěn)定性。

3、材料與結(jié)構(gòu)優(yōu)化

可通過(guò)選擇高純度填充料和焊料,提升界面潤(rùn)濕性和機(jī)械強(qiáng)度,從而在倒裝芯片設(shè)計(jì)中采用更緊湊的凸點(diǎn)布局,降低焊點(diǎn)應(yīng)力集中。

4、設(shè)備與工藝協(xié)同

引入智能溫控系統(tǒng),精確控制回流焊溫度曲線,減少熱沖擊對(duì)焊界的影響。同時(shí)還需要結(jié)合自動(dòng)化設(shè)備提升封裝對(duì)位精度,降低因人為誤差導(dǎo)致的虛焊風(fēng)險(xiǎn)。

通過(guò)上述措施,可系統(tǒng)提升倒裝芯片焊界質(zhì)量,減少退化風(fēng)險(xiǎn)。

四、總結(jié)一下

倒裝芯片(FC)焊界面退化的核心是金屬間化合物(IMC)過(guò)度生長(zhǎng)、熱機(jī)械疲勞、電遷移、界面空洞 / 分層四大機(jī)制疊加,最終導(dǎo)致接觸電阻上升、機(jī)械強(qiáng)度驟降、焊點(diǎn)開裂 / 脫落。可通過(guò)UBM 選材、焊料優(yōu)化、回流 / 底部填充工藝控制、結(jié)構(gòu)應(yīng)力優(yōu)化可顯著提升可靠性,可為倒裝芯片(FC)工藝技術(shù)能力的提升貢獻(xiàn)出不小的力量。

審核編輯 黃宇

-

半導(dǎo)體

+關(guān)注

關(guān)注

339文章

31008瀏覽量

265495 -

封裝

+關(guān)注

關(guān)注

128文章

9297瀏覽量

148882 -

倒裝芯片

+關(guān)注

關(guān)注

1文章

122瀏覽量

16860

發(fā)布評(píng)論請(qǐng)先 登錄

Flip-Chip倒裝焊芯片原理與優(yōu)點(diǎn)

倒裝芯片應(yīng)用的設(shè)計(jì)規(guī)則

倒裝芯片的特點(diǎn)和工藝流程

倒裝焊芯片(Flip-Chip)是什么意思

RFID封裝工藝:Flip Chip和wire bonding

半導(dǎo)體集成電路焊球倒裝是什么意思?有哪些作用?

漢思新材料研發(fā)生產(chǎn)半導(dǎo)體 Flip chip 倒裝芯片封裝用底部填充材料

倒裝焊器件封裝結(jié)構(gòu)設(shè)計(jì)

芯片倒裝Flip Chip封裝工藝簡(jiǎn)介

淺談芯片倒裝Flip Chip封裝工藝

倒裝芯片(flip chip)算先進(jìn)封裝嗎?未來(lái)發(fā)展怎么樣?

倒裝封裝(Flip Chip)工藝:半導(dǎo)體封裝的璀璨明星!

半導(dǎo)體“倒裝芯片(Flip - Chip)”焊界面退化的詳解;

半導(dǎo)體“倒裝芯片(Flip - Chip)”焊界面退化的詳解;

評(píng)論