來源:先進封裝技術與工藝

在后摩爾時代,扇出型晶圓級封裝(FOWLP) 已成為實現異構集成、提升I/O密度和縮小封裝尺寸的關鍵技術路徑。與傳統的扇入型(Fan-In)封裝不同,FOWLP通過將芯片重新排布在重構晶圓上,利用塑封料(EMC) 擴展芯片面積,從而在芯片范圍之外提供額外的I/O連接空間。根據工藝流程的差異,FOWLP主要分為三大類:芯片先裝(Chip-First)面朝下、芯片先裝面朝上以及RDL先制。本文將深入剖析這三種工藝的具體流程、關鍵技術難點及優劣勢對比。

01芯片先裝面朝下工藝

這是最早實現商業化量產的FOWLP工藝,以英飛凌的eWLB技術為代表。其核心邏輯是先將芯片貼裝在臨時載板上,再進行塑封和重布線。

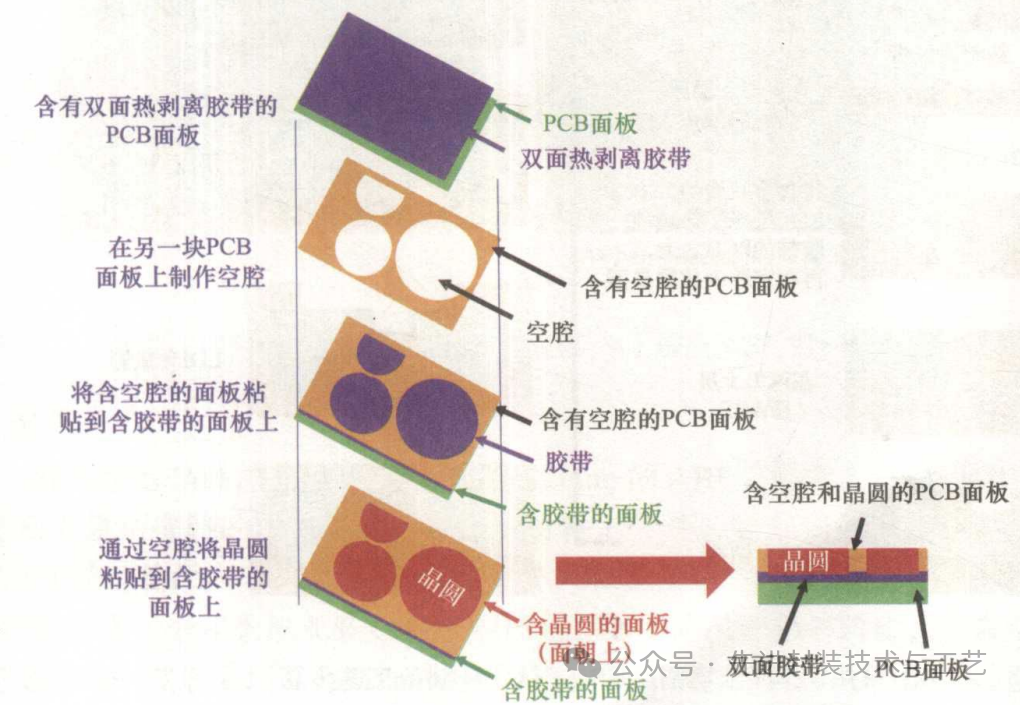

該工藝的典型流程起始于一個臨時載板,通常為金屬或硅材質。首先,在載板上層壓一層熱釋放膠帶。接著,利用高精度的貼片機將經過測試的良品芯片(KGD)以有源面朝下的方式精確放置在膠帶上。

隨后進行壓縮模塑,將塑封料填充在芯片周圍,形成重構晶圓。在塑封固化后,通過加熱使熱釋放膠帶失去粘性,從而將重構晶圓與臨時載板分離(即解鍵合)。此時,芯片的有源面和塑封料表面處于同一平面。

接下來,通過物理氣相沉積(PVD) 濺射Ti/Cu作為種子層,利用光刻和電鍍工藝制作重布線層(RDL) 和鈍化層。最后,在RDL的末端制作凸點下金屬層(UBM) 并植入焊球(Solder Balls),經切割后完成封裝。

芯片先裝FOWLP工藝流程示意圖

技術挑戰: 此工藝最大的痛點在于芯片偏移(Die Shift)。在塑封過程中,流動的塑封料會對芯片產生推力,導致芯片位置偏離預設坐標。此外,重構晶圓在固化冷卻過程中,由于硅芯片與塑封料的熱膨脹系數(CTE) 差異,會產生嚴重的翹曲(Warpage)。這種位置偏移和翹曲會導致后續光刻對準困難,造成RDL與芯片焊盤連接失效,嚴重影響良率。

02芯片先裝面朝上工藝

為了應對面朝下工藝中的部分局限性,面朝上工藝應運而生。其流程差異主要在于芯片的放置方向和互連方式。

在此流程中,芯片以有源面朝上的方式通過芯片貼裝膜(DAF) 固定在載板上。在進行壓縮模塑覆蓋整個芯片后,不需要立即解鍵合。相反,必須通過研磨工藝減薄塑封層,直到暴露出芯片表面的銅柱或以其他方式顯露電極。

隨后,在平整的塑封面上制作RDL,通過電鍍通孔連接到芯片電極。這種方式可以通過增加銅柱的高度來適應3D封裝的需求。

技術優劣: 面朝上工藝通過銅柱延伸了連接距離,有利于散熱和應力緩沖。然而,研磨過程控制精度要求極高,一旦研磨過度損傷芯片電路,或者研磨不足導致連接開路,都會導致報廢。此外,芯片背部貼裝在載板上,雖然減少了部分水平偏移,但垂直方向的共面性仍是挑戰。

03RDL先制工藝

隨著高性能計算對I/O密度和多層RDL需求的增加,RDL先制工藝(亦稱Chip-Last)逐漸成為高端封裝(如臺積電InFO技術)的首選。與前兩者不同,該工藝先在載板上制作RDL,再貼裝芯片。

流程首先在涂有犧牲層(Sacrificial Layer) 的載板上,通過PVD和電鍍工藝制作精細的RDL線路和介電層。這一步類似晶圓廠后道工藝,可以實現極小的線寬線距(L/S)。RDL制作完成后,將芯片通過倒裝(Flip-Chip) 或直接鍵合的方式貼裝在RDL上。隨后進行塑封,并在塑封體背部進行研磨或開孔。最后,去除載板并釋放犧牲層,露出RDL的接觸焊盤用于植球。

FOWLP上的RDL

核心優勢:

良率提升:由于RDL是在平整的載板上預先制作的,若RDL出現缺陷,可以由光學檢測剔除,避免了將昂貴的良品芯片(KGD) 貼裝在壞的RDL上,從而顯著降低了成本風險。

高密度互連:避免了芯片先裝工藝中塑封后的表面不平整問題,能在載板上實現更精細的布線(例如2μm/2μm L/S),非常適合高密度集成的應用處理器(AP) 封裝。

在上述三種FOWLP工藝中,芯片先裝(面朝下) 因其工藝路徑短、成本低,依然是中低端市場的主流選擇,但必須嚴格控制芯片偏移和翹曲問題。芯片先裝(面朝上) 則在特定的3D堆疊場景中由于銅柱互連的存在占有一席之地。而RDL先制盡管流程較長、成本較高,但憑借其對已知良品載板的篩選能力以及對高密度布線的支持,已確立了其在高性能計算和高端移動終端封裝領域的統治地位。

隨著板級扇出型封裝(FOPLP) 的興起,這些工藝正逐漸從晶圓級向大尺寸面板級轉移,這對光刻設備的焦深、貼片機的速度以及電鍍均勻性提出了更嚴苛的挑戰。未來的競爭焦點將集中在如何在擴大面板尺寸以降低成本的同時,通過材料創新和應力模擬來有效抑制翹曲,實現高可靠性的異構集。

-

工藝流程

+關注

關注

7文章

118瀏覽量

16844 -

晶圓級封裝

+關注

關注

5文章

46瀏覽量

11795 -

FOWLP

+關注

關注

1文章

18瀏覽量

10191

原文標題:晶圓級扇出型封裝(FOWLP):三大核心工藝流程與技術壁壘深度解析

文章出處:【微信號:深圳市賽姆烯金科技有限公司,微信公眾號:深圳市賽姆烯金科技有限公司】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

晶圓級扇出型封裝的三大核心工藝流程

晶圓級扇出型封裝的三大核心工藝流程

評論