CDCE6214:超低功耗時鐘發生器的卓越之選

在電子設計領域,時鐘發生器是確保系統穩定運行的關鍵組件之一。今天,我們要深入探討一款性能出色的超低功耗時鐘發生器——CDCE6214。它具有眾多優秀特性,適用于多種應用場景,接下來讓我們詳細了解一下。

文件下載:cdce6214.pdf

特性亮點

高性能低抖動

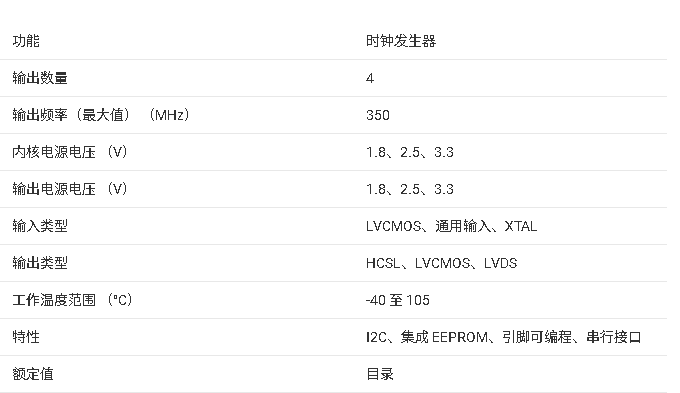

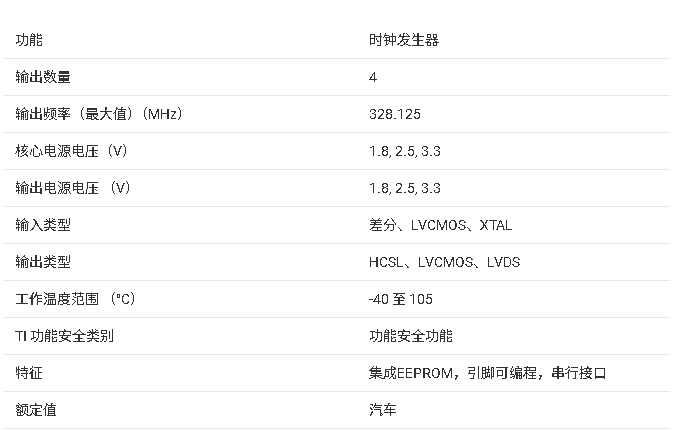

CDCE6214 采用可配置的高性能、低功耗 Frac - N PLL,在不同模式下展現出極低的抖動。在整數模式下,差分輸出典型抖動為 350fs,最大 600fs;LVCMOS 輸出典型抖動為 1.05ps,最大 1.5ps。在分數模式下,差分輸出典型抖動為 1.7ps,最大 2.1ps;LVCMOS 輸出典型抖動為 2.0ps,最大 4.0ps。如此低的抖動性能,能夠為系統提供穩定、精確的時鐘信號。

廣泛的兼容性

它支持 PCIe Gen1/2/3/4 帶 SSC 和 Gen 1/2/3/4/5/6 不帶 SSC,這使得它在不同的 PCIe 應用中都能游刃有余。同時,它還具有通用的時鐘輸入,支持差分 AC - 耦合或 LVCMOS(10MHz 至 200MHz)以及晶體(10MHz 至 50MHz)輸入,為設計提供了更多的靈活性。

靈活的輸出配置

該時鐘發生器擁有四個通道分頻器,可產生高達五種獨特的輸出頻率,范圍從 24kHz 到 328.125MHz。OUT0 - OUT4 引腳支持 LVDS - like、LP - HCSL 或 LVCMOS 輸出的組合,并且具備無毛刺輸出分頻器切換和輸出通道同步功能。此外,還可以通過 GPIO 和寄存器單獨啟用輸出,方便用戶根據實際需求進行配置。

頻率微調選項

CDCE6214 提供 DCO 模式,頻率增量或減量的步長可達 10ppb 或更小,同時具有完全集成的、可配置的環路帶寬(100kHz 至 1.6MHz),能夠滿足不同系統對頻率精度的要求。

低功耗與小尺寸

典型功耗方面,4 輸出通道為 65mA,1 輸出通道為 23mA,展現出出色的低功耗特性。其采用 24 引腳 VQFN(4mm × 4mm)封裝,小尺寸設計節省了 PCB 空間,適合對空間要求較高的應用。

應用場景

CDCE6214 的應用范圍十分廣泛,涵蓋了多個領域:

- PCIe 時鐘:支持 PCIe Gen 1 - Gen 6 時鐘,為高速數據傳輸提供穩定的時鐘信號。

- 數據中心與企業計算:在數據中心和企業級計算設備中,確保系統的時鐘同步和穩定性。

- PC 與筆記本電腦:為電腦的各種組件提供精確的時鐘,保證系統的正常運行。

- 企業級多功能打印機:在打印機的控制和數據傳輸過程中,提供穩定的時鐘支持。

- 測試與測量手持設備:滿足手持設備對低功耗和高精度時鐘的需求。

詳細解析

引腳配置與功能

CDCE6214 共有 24 個引腳,不同引腳具有不同的功能。例如,POWER 類引腳包括 DAP(芯片接地散熱引腳)、VDD_REF(參考輸入和數字電源)、VDD_VCO(PLL/VCO 電源)等;INPUT BLOCK 類引腳如 PRIREF_P、PRIREF_N 等用于提供外部時鐘輸入;OUTPUT BLOCK 類引腳則用于輸出不同類型的時鐘信號;DIGITAL CONTROL / INTERFACES 類引腳如 GPIO1、SDA/GPIO2 等用于設備的控制和通信。

規格參數

絕對最大額定值

在使用過程中,需要注意其絕對最大額定值,如電源電壓(VDD_REF、VDD_VCO 等)范圍為 - 0.3V 至 3.63V,輸入電壓范圍為 - 0.3V 至 VDD_REF + 0.3V 等。超出這些范圍可能會導致設備永久性損壞。

推薦工作條件

推薦的工作條件包括電源電壓(VDD_VCO、VDDO_12 等為 1.71V 至 3.465V)、環境溫度( - 40°C 至 105°C)等。在這些條件下,設備能夠正常、穩定地工作。

其他特性參數

還包括 EEPROM 特性(編程周期、數據保留時間)、參考輸入特性(單端、差分、晶體模式)、PLL 特性(頻率范圍、增益等)、輸出特性(抖動、隔離度等)等,這些參數為我們深入了解和使用該設備提供了詳細的依據。

功能模塊

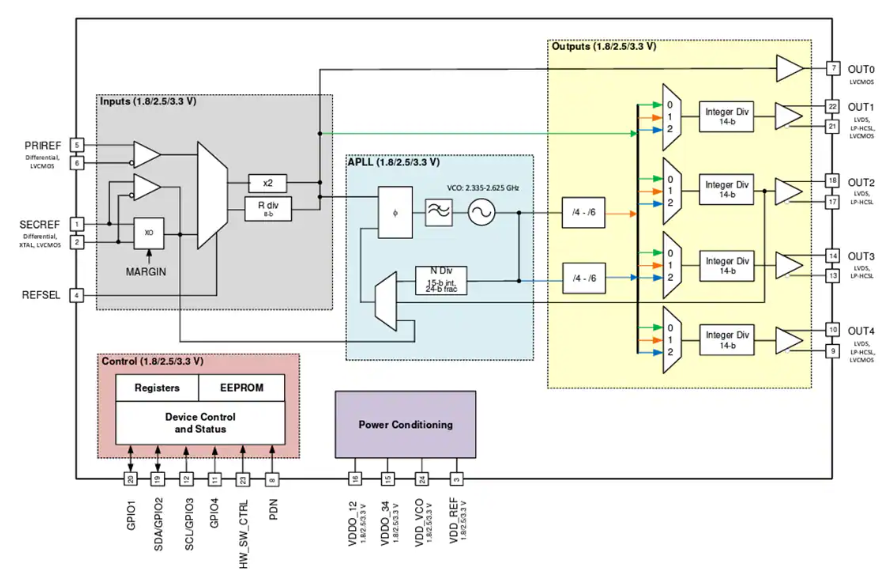

參考模塊

該模塊支持多種輸入模式,包括 XTAL、差分和單端 LVCMOS 輸入。通過參考 MUX 可以選擇不同的參考時鐘,還可以使用參考分頻器或時鐘倍增器對參考時鐘進行進一步處理。輸出時鐘可以旁路到 OUT0 和其他輸出通道,為設計提供了更多的靈活性。

鎖相環(PLL)

CDCE6214 具有完全集成的 PLL 電路,支持整數和分數 - N PLL 模式,以及不同階的 MASH 操作。PFD 工作頻率在 1MHz 至 100MHz 之間,VCO 頻率范圍為 2335MHz 至 2625MHz。同時,還支持 0.25% 和 0.5% 的中心和下展擴頻時鐘(SSC)生成,能夠有效降低電磁干擾。

時鐘分配

VCO 輸出連接到時鐘分配網絡,該網絡包含多個分頻器和多路復用器。輸出通道具有可配置的差分和單端緩沖器,支持多種輸出信號標準(LVDS - like、LP - HCSL、LVCMOS),輸出頻率范圍廣泛,能夠滿足不同系統的需求。

電源管理

內部具有低 dropout 調節器(LDO),每個電源引腳可以獨立配置為 1.8V、2.5V 或 3.3V。每個模塊都提供了電源關閉位,可以在不需要時禁用模塊以節省功耗。

控制引腳

通過多個 LVCMOS 輸入引腳對設備進行控制,如 HW_SW_CTRL 用于 EEPROM 頁面選擇,PDN/SYNCN 用于設備復位或同步等。這些引腳的合理配置可以實現不同的工作模式。

編程與配置

I2C 接口

CDCE6214 可以通過 I2C 串行接口進行配置,支持標準模式(100kHz)和快速模式(400kHz)。不同的工作模式下,I2C 目標地址可能不同,并且可以通過 EEPROM 對設備的 I2C 地址進行編程。

EEPROM

設備內部包含 EEPROM,具有循環冗余校驗(CRC)功能。推薦的編程步驟包括讀取出廠默認配置、修改寄存器位、解鎖 EEPROM 等。可以通過寄存器提交方法或 EEPROM 直接訪問方法將配置寫入 EEPROM。

應用與實現

典型應用電路

在典型應用中,使用 I2C 接口和 25MHz 晶體輸入時,需要將晶體兩端連接到相應引腳,REFSEL 引腳下拉選擇二次輸入,HW_SW_CTRL 引腳根據是否使用 EEPROM 進行相應設置。同時,需要為各個電源引腳提供合適的電源,并使用上拉電阻將 I2C 數據線和時鐘線連接到 VDD_REF。

設計注意事項

在設計過程中,需要注意電源的上電順序,推薦同時施加所有 VDD 電源或先施加 VDDREF。同時,要對電源進行適當的去耦處理,使用鐵氧體磁珠隔離不同電源,并根據布局優化去耦電容的配置。在 PCB 布局方面,要隔離輸入和輸出,避免阻抗突變,合理放置去耦電容和過孔,以確保設備的性能和穩定性。

總結

CDCE6214 作為一款超低功耗時鐘發生器,具有高性能、低抖動、廣泛兼容性、靈活配置等眾多優點,適用于多種應用場景。在實際設計過程中,我們需要深入了解其引腳功能、規格參數、工作模式和編程方法,同時注意電源管理和 PCB 布局等方面的問題,以充分發揮其性能優勢,為我們的電子設計帶來更多的便利和可能性。

各位電子工程師們,在您的設計中是否也遇到過時鐘發生器的選型和設計難題呢?您對 CDCE6214 有什么看法或疑問,歡迎在評論區留言討論。

-

超低功耗

+關注

關注

5文章

272瀏覽量

19129 -

時鐘發生器

+關注

關注

1文章

352瀏覽量

70131

發布評論請先 登錄

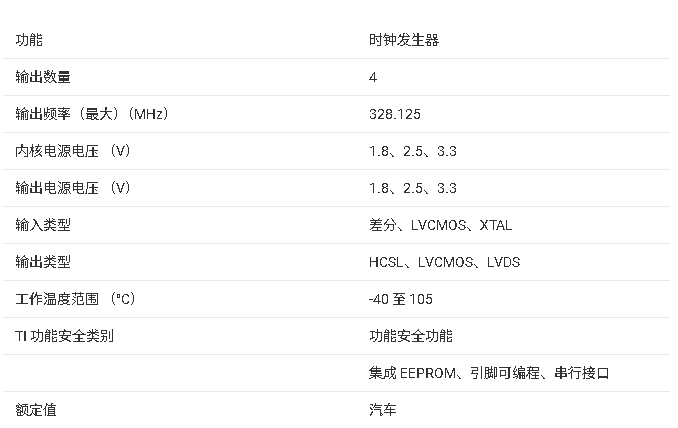

CDCI6214超低功耗時鐘發生器(具有PCIe支持、四路可編程輸出和EEPROM)數據表

德州儀器CDCE6214Q1TM超低功耗時鐘發生器技術解析

?CDCE6214Q1TM 超低功耗時鐘發生器技術文檔總結

CDCE6214:超低功耗時鐘發生器的卓越之選

CDCE6214:超低功耗時鐘發生器的卓越之選

評論