LMK3H2104與LMK3H2108:PCIe時鐘生成的理想之選

在電子設計領域,時鐘發生器對于確保系統的穩定運行至關重要。今天,我們要深入探討的是德州儀器(TI)推出的LMK3H2104和LMK3H2108這兩款4輸出和8輸出的PCIe Gen 1 - 7兼容低抖動通用BAW時鐘發生器。

文件下載:lmk3h2108.pdf

1. 核心特性

1.1 集成BAW諧振器

這兩款器件集成了BAW諧振器,無需外部XTAL/XO,大大簡化了設計,減少了外部元件的使用,降低了成本和電路板空間。

1.2 靈活的輸出頻率

通過2個分數輸出分頻器(FOD)和各個通道分頻器,可實現高達400MHz的輸出頻率。這種靈活性使得它們能夠滿足各種不同的應用需求,無論是高速通信還是高性能計算。

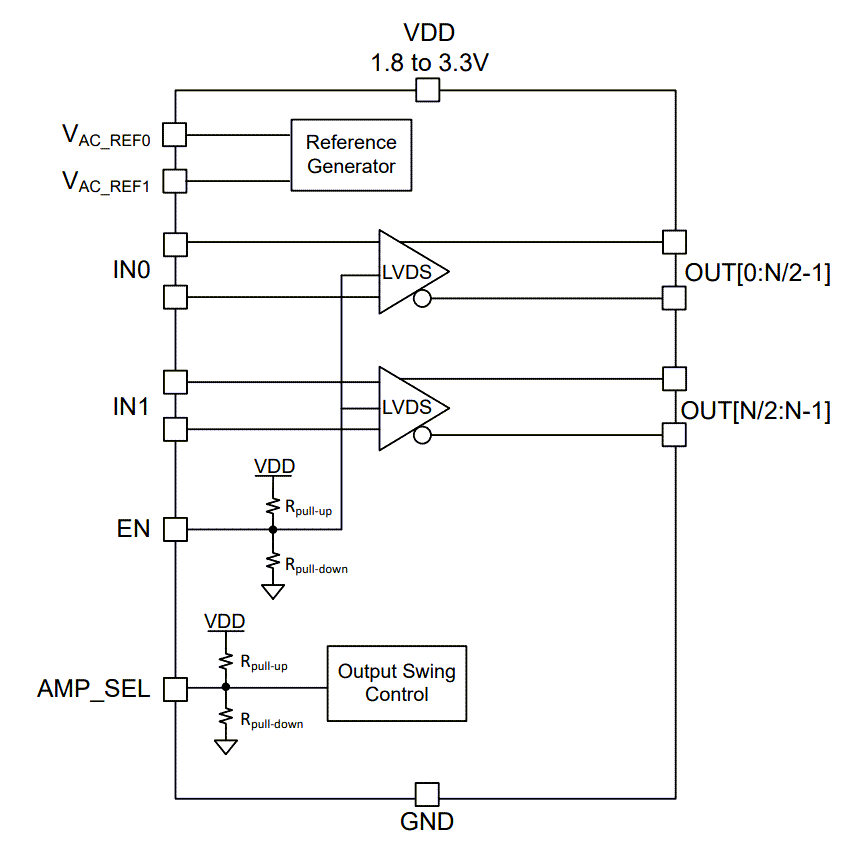

1.3 多樣的輸出格式

支持1.2/1.8/2.5/3.3V LVCMOS、DC - 或AC - 耦合LVDS、可編程擺幅的LP - HCSL等多種輸出格式,還可從LP - HCSL衍生出LVPECL、CML等其他格式。這意味著它們可以與不同類型的設備進行接口,具有廣泛的適用性。

1.4 極低的抖動

- PCIe Gen 5 CC帶SSC抖動最大為61fs

- PCIe Gen 6 CC帶SSC抖動最大為36.4fs

- PCIe Gen 7 CC帶SSC抖動最大為25.5fs

如此低的抖動確保了時鐘信號的穩定性和準確性,對于高速數據傳輸和高精度系統至關重要。

1.5 PCIe兼容性

支持PCIe Gen 1到Gen 7,滿足了不同版本PCIe接口的時鐘需求,為系統的升級和兼容性提供了保障。

1.6 可配置的SSC

支持可編程的 - 0.05%到 - 3%下擴和±0.025%到±1.5%中心擴,以及預設的 - 0.1%、 - 0.25%、 - 0.3%和 - 0.5%下擴。這種可配置性有助于減少電磁干擾(EMI),提高系統的電磁兼容性。

1.7 靈活的電源供應

每個VDD和VDDO引腳都可以獨立連接到1.8、2.5或3.3V,為設計提供了更大的靈活性,可根據具體應用需求進行電源配置。

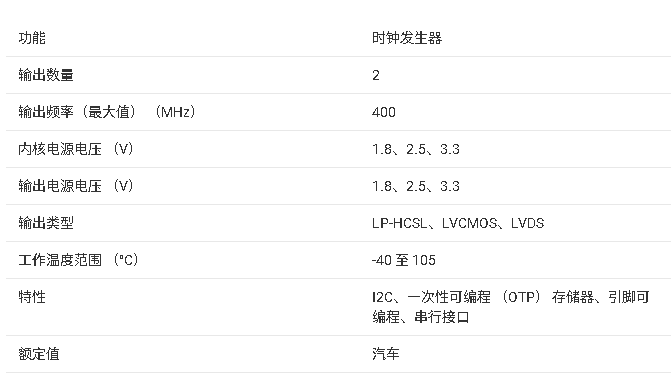

1.8 寬溫度范圍

能夠在 - 40到105°C的環境溫度下工作,適用于各種惡劣的工業和汽車應用場景。

2. 應用領域

2.1 高性能計算服務器主板

在高性能計算服務器中,需要高精度、低抖動的時鐘信號來確保各個組件的同步運行。LMK3H2104和LMK3H2108的低抖動特性和高兼容性使其成為服務器主板時鐘生成的理想選擇。

2.2 NIC、SmartNIC和硬件加速

網絡接口卡(NIC)、智能網絡接口卡(SmartNIC)和硬件加速設備需要高速、穩定的時鐘信號來處理大量的數據。這兩款時鐘發生器能夠滿足這些設備對時鐘信號的嚴格要求。

2.3 PCIe Gen 1到Gen 7時鐘生成

無論是舊版本的PCIe接口還是最新的Gen 7接口,LMK3H2104和LMK3H2108都能提供符合標準的時鐘信號,確保PCIe設備的正常運行。

2.4 通用時鐘生成和XO/XTAL替換

它們還可以作為通用時鐘發生器使用,替代傳統的XO/XTAL,簡化設計并提高性能。

3. 詳細規格

3.1 絕對最大額定值

- 設備電源電壓(VDD): - 0.3到3.9V

- 輸出電源電壓(VDDO): - 0.3到3.9V

- 輸出引腳電壓(V OUT):根據不同情況有所不同,但都有明確的限制范圍

在設計時,必須確保電源電壓在這些絕對最大額定值范圍內,以避免設備損壞。

3.2 ESD額定值

- 人體模型(HBM):±2000V

- 帶電設備模型(CDM):±500V

這表明它們具有一定的靜電防護能力,但在實際操作中,仍需采取適當的ESD防護措施。

3.3 推薦工作條件

- 設備電源電壓(VDD)和輸出電源電壓(VDDO):1.8、2.5或3.3V ± 5%

- 環境溫度(TA): - 40到105°C

- 結溫(TJ): - 40到110°C

在推薦工作條件下使用設備,可以確保其性能和可靠性。

3.4 電氣特性

包括總頻率誤差、老化引起的頻率誤差、時鐘輸入要求、輸出電壓、輸出阻抗等多項電氣特性。這些特性對于評估設備的性能和進行電路設計非常重要。

4. 功能描述

4.1 功能框圖

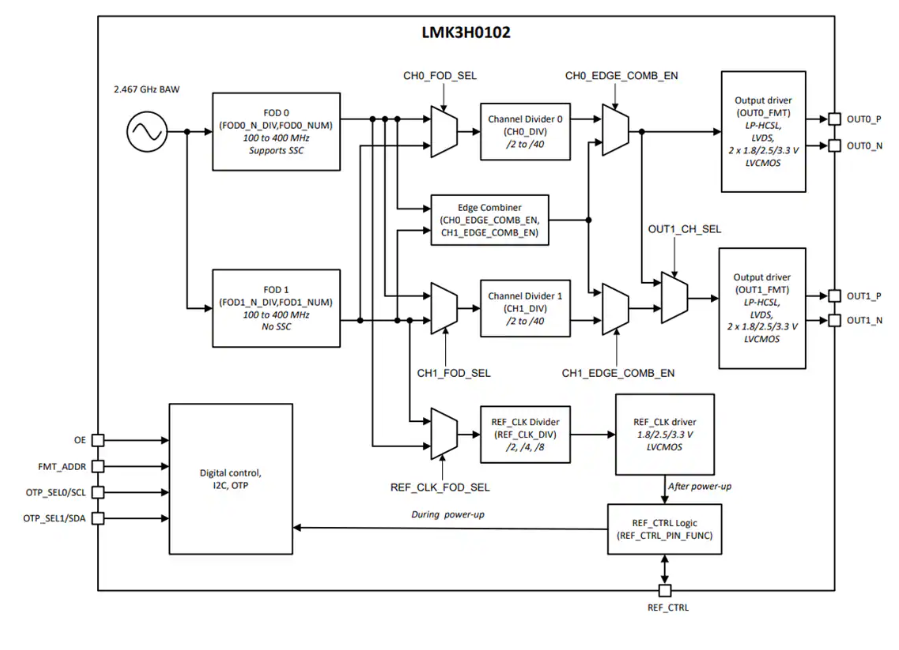

從功能框圖可以看出,每個輸出組都可以獨立選擇時鐘源,如IN0、IN1、IN2、FOD0、FOD1或邊緣組合器。多個GPI和GPIO引腳提供了靈活的引腳控制,方便用戶根據具體需求進行配置。

4.2 GPI/GPIO功能

GPI和GPIO引腳具有多種功能,如輸出使能組控制、I2C地址選擇、動態OTP選擇等。通過合理配置這些引腳,可以實現對設備的靈活控制。

4.3 OTP功能

支持一次性可編程(OTP)非易失性存儲器,可進行自定義和工廠預編程。OTP分為“基礎”部分和“頁面”部分,每個頁面可以通過特定的引腳選擇。這使得設備在不同的應用場景下可以快速加載不同的配置。

4.4 電源供應

每個電源引腳都有明確的分配和電壓要求,并且可以根據需要選擇是否連接電源。在設計電源電路時,需要根據具體的應用需求和設備規格進行合理的電源配置。

4.5 輸出使能和禁用

每個輸出都有獨立的輸出禁用寄存器位,還有全局OE位來控制所有輸出。輸出可以分配到不同的OE組,通過GPI/GPIO引腳進行控制。輸出使能遵循AND邏輯,確保輸出的準確控制。

4.6 狀態信號

包括CLK_READY、INx_LOS、輸出頻率檢測、CRC_ERROR等狀態信號。這些信號可以幫助用戶了解設備的工作狀態,進行故障診斷和系統監控。

5. 應用與實現

5.1 設計步驟

在進行應用設計時,需要考慮電源電壓、輸入行為、頻率規劃和輸出格式選擇等多個方面。例如,在頻率規劃時,需要根據所需的輸出頻率確定FOD頻率,并合理配置相關寄存器。

5.2 布局建議

為了獲得最佳的性能,布局時需要遵循一些準則,如隔離輸入和輸出、使用GND屏蔽、合理放置去耦電容等。良好的布局可以減少電磁干擾,提高信號的穩定性。

6. 總結

LMK3H2104和LMK3H2108以其集成的BAW諧振器、靈活的輸出頻率和格式、極低的抖動以及廣泛的兼容性等特性,成為PCIe時鐘生成和通用時鐘應用的理想選擇。在實際設計中,我們需要充分了解它們的特性和規格,合理進行配置和布局,以確保系統的穩定運行和高性能。大家在使用過程中遇到任何問題,歡迎在評論區交流討論。

發布評論請先 登錄

LMK3H2108超低抖動時鐘發生器

LMK3H2104超低抖動時鐘發生器

Texas Instruments LMK3H0102無基準時鐘發生器數據手冊

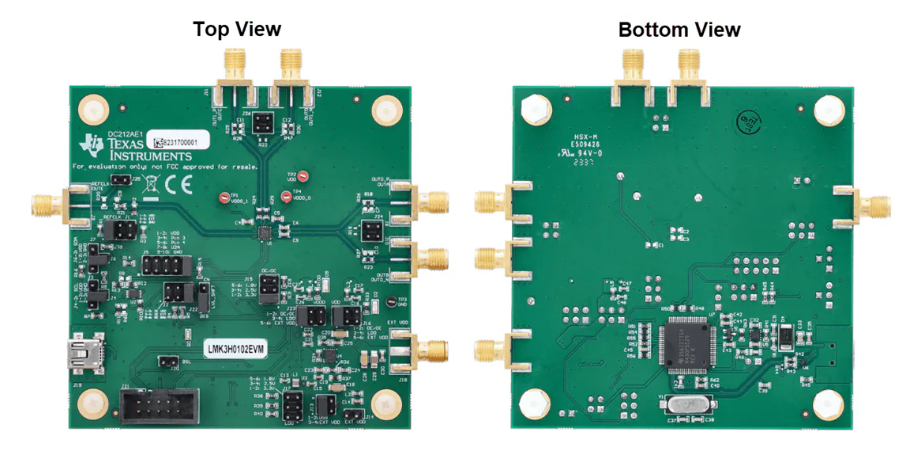

LMK3H0102EVM評估模塊深度解析與技術應用指南

?LMK3H2104 4-Output PCIe時鐘發生器技術文檔總結

?LMK3H0102-Q1 參考無晶體時鐘發生器技術文檔總結

LMK1D2106/LMK1D2108 LVDS時鐘緩沖器技術解析與應用指南

LMK3H2104與LMK3H2108:PCIe時鐘生成的理想之選

LMK3H2104與LMK3H2108:PCIe時鐘生成的理想之選

評論