汽車級時鐘緩沖器LMK00334-Q1:PCIe應用的理想之選

在汽車電子領域,隨著高級駕駛輔助系統(ADAS)、信息娛樂系統等的不斷發展,對時鐘信號的穩定性和低抖動性提出了更高的要求。今天,我們就來詳細了解一款專為汽車應用設計的時鐘緩沖器——LMK00334-Q1。

文件下載:lmk00334-q1.pdf

一、產品概述

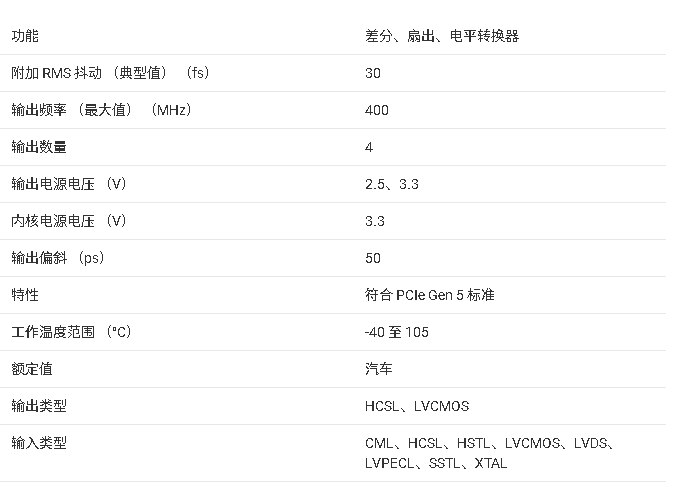

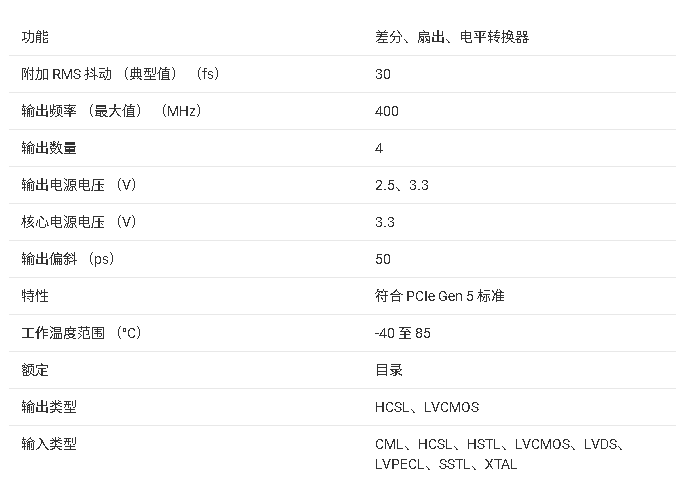

LMK00334-Q1是一款四輸出時鐘緩沖器和電平轉換器,適用于PCIe Gen 1至Gen 5應用。它具有低抖動、高電源抑制比(PSRR)等特點,能夠為汽車電子系統提供穩定可靠的時鐘信號。該器件經過AEC-Q100認證,可在-40°C至105°C的寬溫度范圍內工作,滿足汽車應用的嚴苛環境要求。

二、產品特性

2.1 輸入特性

- 3:1輸入復用器:提供兩個通用輸入和一個晶體輸入,可靈活選擇時鐘源。通用輸入可接受LVPECL、LVDS、CML、SSTL等多種信號類型,最高工作頻率可達400 MHz;晶體輸入可接受10 - 40 MHz的晶體或單端時鐘。

- 低抖動性能:在100 MHz時,PCIe Gen3/Gen4的附加均方根相位抖動典型值僅為30 fs RMS,有效降低了時鐘信號的抖動,提高了系統的穩定性。

2.2 輸出特性

- 雙輸出組:包含兩個輸出組,每組有兩個差分輸出,輸出類型可選擇HCSL或Hi-Z,滿足不同應用的需求。

- LVCMOS輸出:具有同步使能輸入,可實現無短脈沖操作,確保輸出信號的質量。

2.3 電源特性

- 獨立輸出電源:采用3.3 V ± 5%的核心電源((V_{CC}))和三個獨立的3.3 V或2.5 V ± 5%的輸出電源((VCCO)),可根據實際需求靈活配置,降低功耗。

- 高PSRR:在156.25 MHz時,PSRR可達 -72 dBc,有效抑制電源紋波對時鐘信號的影響。

2.4 封裝與溫度范圍

- 32引腳WQFN封裝:尺寸為5 mm × 5 mm,體積小巧,便于PCB布局。

- 寬溫度范圍:工業溫度范圍為 -40°C至 +105°C,適應各種惡劣的工作環境。

三、應用場景

3.1 信息娛樂系統

在汽車信息娛樂系統中,如車載信息通訊系統(Telematics)和中控臺信息娛樂控制單元(Head Unit),需要穩定的時鐘信號來保證音頻、視頻等數據的傳輸和處理。LMK00334-Q1的低抖動特性能夠有效提高信號的質量,確保信息娛樂系統的流暢運行。

3.2 高級駕駛輔助系統(ADAS)

ADAS系統對時鐘信號的精度和穩定性要求極高,例如自動駕駛控制器需要精確的時鐘來同步傳感器數據和執行器動作。LMK00334-Q1能夠為ADAS系統提供可靠的時鐘信號,提高系統的安全性和可靠性。

四、詳細設計要點

4.1 時鐘輸入設計

-

輸入選擇:通過CLKin_SEL[1:0]引腳可選擇不同的時鐘輸入源,具體選擇方式如下表所示: CLKin_SEL1 CLKin_SEL0 SELECTED INPUT 0 0 CLKin0, CLKin0* 0 1 CLKin1, CLKin1* 1 X OSCin -

輸入要求:為了獲得最佳的相位噪聲和抖動性能,建議輸入信號的差分擺率不低于3 V/ns。對于單端輸入,可采用AC或DC耦合方式,并在輸入引腳附近放置50 Ω負載電阻進行信號衰減和線路端接。

4.2 晶體接口設計

-

負載電容計算:晶體接口的負載電容((C{L}))通常在18 - 20 pF之間,但實際的負載電容值會受到器件的OSCin輸入電容((C{IN}))和PCB雜散電容((C{STRAY}))的影響。可根據以下公式計算離散負載電容(C{1})和(C{2})的值: [C{L}=left(C{1} × C{2}right) /left(C{1}+C{2}right)+C{IN}+C{STRAY }] 通常取(C{1}=C{2}),則可簡化為: [C{1}=left(C{L}-C{IN}-C{STRAY }right) × 2]

-

晶體功耗控制:為了避免晶體過驅動,需要確保晶體的功耗不超過其制造商規定的最大驅動電平。可通過外部電阻(R_{LIM })來限制晶體的驅動電平,建議起始值為1.5 kΩ。

4.3 時鐘輸出設計

- 輸出使能:HCSL輸出緩沖器可通過CLKout_EN [1:0]引腳進行使能或禁用,當CLKout_EN為0時,輸出為HCSL;當CLKout_EN為1時,輸出為Hi-Z。

- 輸出端接:對于HCSL輸出,在DC耦合操作時,應在驅動器輸出附近使用50 Ω電阻接地進行端接,以防止信號反射。

4.4 電源設計

- 電源旁路:(V_{CC})和(VCCO)電源引腳應分別使用0.1 μF或0.01 μF的高頻旁路電容,并在器件附近放置1 - 10 μF的去耦電容,以減小電源噪聲。

- 電源功耗計算:根據器件的不同配置,可通過以下公式計算總電源功耗((P{TOTAL}))和IC功耗((P{DEVICE})): [P{TOTAL }=left(V{CC} × I_{CCTOTAL }right)+left(V{CCOA } × I_{CCOBANK }right)+left(V{CCOB} × I_{CCOBANK }right)+left(V{CCO C} × I{CCO{C}}right)] [P{DEVICE }=P{TOTAL }-N × P_{RTHCSL }] 其中,(P{RT_HCSL })為HCSL輸出端接電阻的功耗。

4.5 布局設計

- 布線規則:在PCB布局時,應盡量縮短旁路電容與電源引腳之間的連接,采用低阻抗連接將電容的另一端接地。對于HCSL輸出,應在驅動器輸出附近使用50 Ω電阻接地進行端接。

- 熱管理:為了確保器件的可靠性和性能,需要注意熱管理。可在PCB上設計散熱焊盤和多個過孔連接到接地層,以提高散熱效率。建議在器件的背面設計一個約2平方英寸的銅面積作為簡單的散熱器。

五、總結

LMK00334-Q1作為一款專為汽車應用設計的時鐘緩沖器,具有低抖動、高PSRR、寬溫度范圍等優點,能夠滿足汽車電子系統對時鐘信號穩定性和可靠性的要求。在實際設計中,我們需要根據具體的應用需求,合理選擇時鐘輸入源、優化晶體接口設計、正確配置輸出端接和電源旁路等,以充分發揮該器件的性能優勢。同時,良好的PCB布局和熱管理也是確保系統穩定運行的關鍵。希望本文能夠為電子工程師在設計汽車PCIe應用時提供一些有價值的參考。你在使用LMK00334-Q1或其他時鐘緩沖器時遇到過哪些問題呢?歡迎在評論區分享你的經驗和見解。

發布評論請先 登錄

LMK00334四路輸出PCIe第1代至第5代時鐘緩沖器和電平轉換器數據表

LMK00334-Q1四路輸出PCIe第1代至第5代時鐘緩沖器和電平轉換器數據表

?LMK00334-Q1 四輸出時鐘緩沖器和電平轉換器技術文檔總結

?LMK00334四輸出時鐘緩沖器與電平轉換器技術文檔總結

汽車級時鐘緩沖器LMK00334-Q1:PCIe應用的理想之選

汽車級時鐘緩沖器LMK00334-Q1:PCIe應用的理想之選

評論