探索LMK3H0102-Q1:PCIe時鐘生成的理想之選

在電子設計領域,時鐘發生器對于確保系統的穩定運行至關重要。今天,我們將深入探討一款高性能的時鐘發生器——LMK3H0102-Q1,它專為PCIe Gen 1 - 7應用而設計,具備諸多卓越特性。

文件下載:lmk3h0102-q1.pdf

產品概述

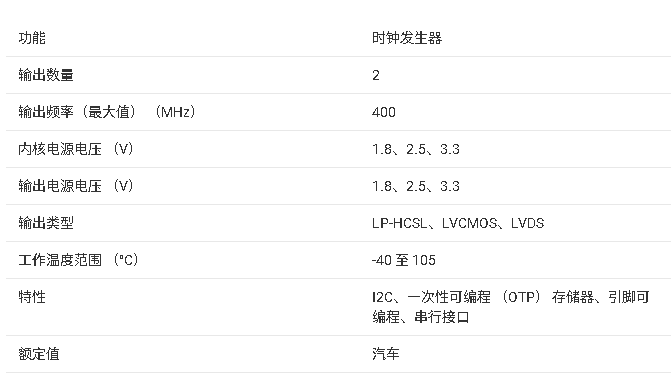

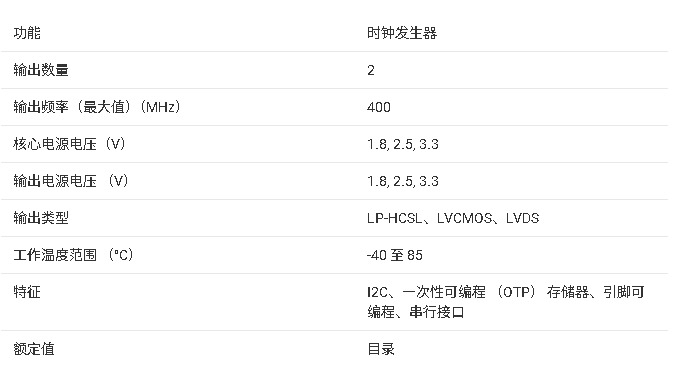

LMK3H0102-Q1是一款符合AEC - Q100 Grade 2標準的汽車級參考無時鐘發生器,支持擴展頻譜時鐘(SSC)。它采用TI專有的體聲波(BAW)技術,無需外部晶體或時鐘參考,就能提供±25ppm的時鐘輸出。該器件可同時提供兩個SSC時鐘、兩個非SSC時鐘,或一個SSC時鐘和一個非SSC時鐘,全面滿足PCIe Gen 1至Gen 7的合規要求。

關鍵特性剖析

1. 高可靠性與寬溫范圍

該器件通過了AEC - Q100 Grade 2認證,適用于汽車應用。其環境溫度范圍為–40°C至105°C,能在惡劣的汽車環境中穩定工作。同時,它具備功能安全能力,提供相關文檔以輔助功能安全系統設計。

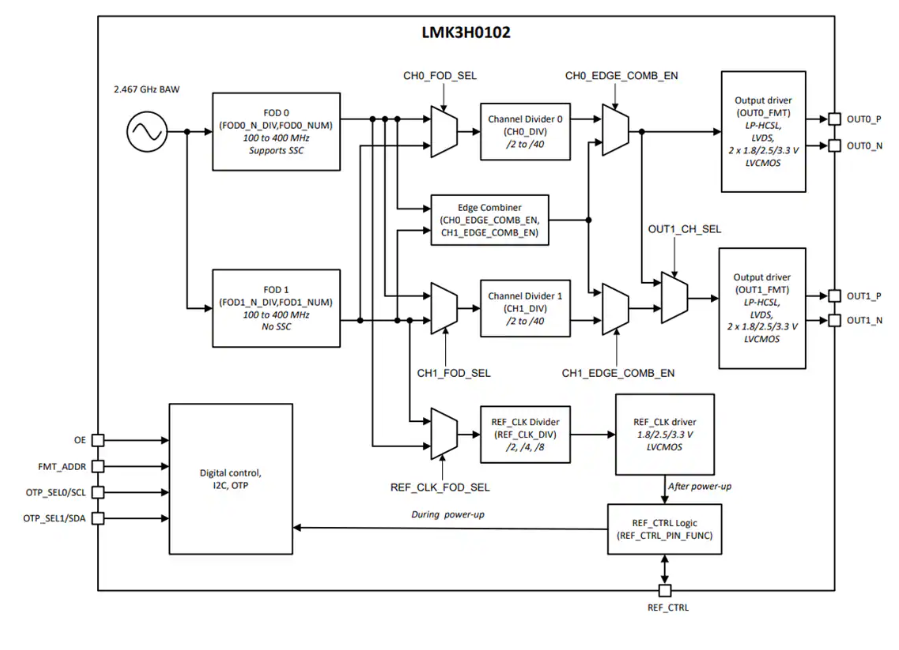

2. 靈活的頻率生成

- 雙FOD設計:內部集成兩個分數輸出分頻器(FOD),每個FOD可產生100MHz至400MHz的頻率。通過兩個通道分頻器,可將FOD頻率進一步分頻至2.5MHz至200MHz。若要生成200MHz以上的頻率,可啟用邊緣組合器,此時通道分頻器將被旁路,生成的頻率范圍為200MHz至400MHz。

- 多輸出格式支持:支持LP - HCSL(85Ω或100Ω)、LVDS和1.8V、2.5V、3.3V LVCMOS輸出格式。LVCMOS輸出支持最高200MHz的頻率,且OUT0和OUT1引腳可實現AC - LVDS、DC - LVDS、LP - HCSL和LVCMOS的組合。

3. 低抖動與可編程SSC

- 超低PCIe抖動:在SSC模式下,PCIe Gen 5、Gen 6和Gen 7的通用時鐘抖動分別低至57.5fs、34.5fs和29.6fs,遠低于PCIe標準的限制。

- 可編程SSC調制深度:提供預編程的–0.1%、–0.25%、–0.3%和–0.5%下擴頻選項,以及寄存器可編程的–0.1%至–3%下擴頻或±0.05%至±1.5%中心擴頻選項。

4. 其他特性

- 電源靈活性:支持1.8V至3.3V的電源電壓,內部LDO在500kHz開關噪聲下具有–93.1dBc的PSNR,為LP - HCSL輸出提供穩定的電源。

- 低輸出至輸出偏斜:輸出至輸出偏斜小于50ps,確保時鐘信號的同步性。

- 故障安全數字輸入引腳:增強了系統的可靠性。

應用領域廣泛

LMK3H0102-Q1可替代多達5個晶體振蕩器(XO),廣泛應用于ADAS域控制器、車輛儀表集群、自動駕駛、高性能計算、駕駛員監控系統、汽車網關、IVI、LiDAR和雷達等領域。

詳細設計與配置

1. 功能模式

該器件支持兩種功能模式,由REF_CTRL引腳在上電時決定:

- OTP模式:當REF_CTRL引腳拉高時,進入OTP模式。通過OTP_SEL0和OTP_SEL1引腳選擇四個OTP頁面之一,默認輸出頻率為100MHz。

- I2C模式:當REF_CTRL引腳拉低時,進入I2C模式。通過修改活動寄存器來配置器件,若需要非默認配置,則每次上電時都需寫入寄存器。

2. 編程與寄存器配置

通過I2C接口,主機(如DSP、微控制器、FPGA等)可對LMK3H0102-Q1進行配置和監控。器件寄存器包含多個控制位,可用于控制和監控各個功能模塊。部分寄存器內容存儲在內部EFUSE中,由TI一次性編程,不可重寫,但可通過I2C寄存器接口后續更改寄存器值。

3. 輸出格式與控制

- 輸出格式選擇:支持LP - HCSL、LVDS和LVCMOS等多種輸出格式。在OTP模式下,可通過FMT_ADDR引腳和相關寄存器設置輸出格式;在I2C模式下,通過相應寄存器進行配置。

- 輸出使能控制:支持同步輸出使能(OE),OE引腳默認低電平有效,可通過配置控制OUT0和OUT1的輸出。同時,可通過寄存器設置OE引腳的極性。

應用設計要點

1. 頻率規劃

在設計LMK3H0102-Q1配置時,首先要確定所需的FOD頻率。若輸出頻率大于200MHz,兩個頻率必須相同且不能使用SSC;若兩個輸出頻率相同且SSC設置相同,可僅使用一個FOD;若一個輸出需要SSC而另一個不需要,則SSC輸出使用FOD0,非SSC輸出使用FOD1。

2. 電源供應

- 上電時序:VDD引腳為控制引腳、串行接口和REF_CTRL引腳供電,任何上拉電阻必須連接到與VDD相同的域。若輸出未使用,將相應的VDDO_x軌連接到VDD。當VDD和VDDO_x軌電壓相同時,建議直接連接;若不同,VDD必須先上升,VDDO_x在不超過5ms后上升。

- 去耦電容:為每個電源引腳靠近放置0.1μF或1μF的電容,使用單獨的鐵氧體磁珠隔離VDD和VDDO電源。

3. 布局設計

- 輸出隔離:使用GND屏蔽隔離輸出,將所有輸出作為差分對布線。當生成多個頻率時,隔離相鄰輸出。

- 阻抗匹配:盡量避免扇入和扇出區域的阻抗突變。使用五個過孔將散熱墊連接到實心GND平面,優先選擇全通式過孔。

總結

LMK3H0102-Q1憑借其高可靠性、靈活的頻率生成能力、低抖動和可編程SSC等特性,成為PCIe時鐘生成的理想選擇。在設計過程中,工程師需根據具體應用需求,合理進行頻率規劃、電源供應和布局設計,以充分發揮該器件的性能優勢。大家在使用LMK3H0102-Q1的過程中,遇到過哪些有趣的挑戰呢?歡迎在評論區分享你的經驗和見解。

發布評論請先 登錄

LMK3H0102無基準可編程時鐘發生器

LMK3H0102無基準2差分或5單端輸出PCIe第1代到第6代兼容可編程BAW時鐘發生器數據表

Texas Instruments LMK3H0102無基準時鐘發生器數據手冊

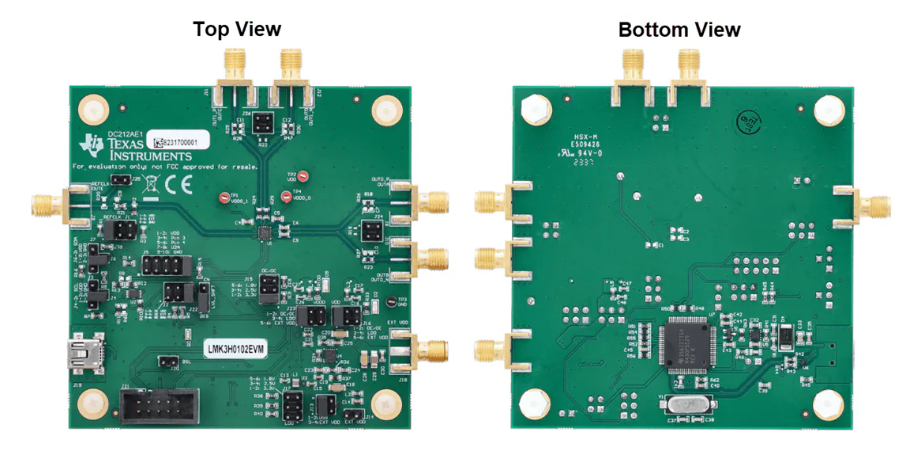

LMK3H0102EVM評估模塊深度解析與技術應用指南

?LMK3H0102-Q1 參考無晶體時鐘發生器技術文檔總結

?LMK3H0102 參考無源2差分或5單端輸出PCIe Gen 1-7兼容可編程BAW時鐘發生器總結

探索LMK3H0102-Q1:PCIe時鐘生成的理想之選

探索LMK3H0102-Q1:PCIe時鐘生成的理想之選

評論