LMK3H2104 是一款基于 BAW 的時鐘發生器,不需要任何外部 XTAL 或 XO。該器件可用作PCIe時鐘發生器或通用時鐘發生器。2 個 FOD(分數輸出分頻器)同時提供頻率靈活性、低功耗和低抖動。

LMK3H2104具有多達 4 個差分輸出和 2 個 LVCMOS 輸出或多達 10 個 LVCMOS 輸出。該器件還有一個時鐘輸入。時鐘輸入提供時鐘復用和緩沖能力。每個輸出組可以獨立選擇任何時鐘源。

*附件:lmk3h2104.pdf

GPI 和 GPIO 引腳提供了額外的控制靈活性。這些引腳可以配置為單獨的OE、分組OE、I2C地址選擇、OTP頁面選擇、PWRGD/PWRDN#、狀態輸出和其他功能。

該器件支持一次性可編程 (OTP) 非易失性存儲器,可定制和工廠預編程。

特性

- 集成 BAW 諧振器

- 無需外部 XTAL/XO

- 靈活的輸出頻率

- 2 個分數輸出分頻器 (FOD),獨立通道分頻器

- 高達 400MHz 的輸出頻率

- 靈活的輸出格式

- 1.2/1.8/2.5/3.3V LVCMOS

- 直流或交流耦合LVDS

- LP-HCSL 具有可編程擺動。LVPECL、CML等格式可衍生自LP-HCSL

- 極低抖動

- 最大 61 秒 PCIe Gen 5 CC,帶 SSC 抖動

- 最大 36.4fs PCIe Gen 6 CC,帶 SSC 抖動

- 最大 25.5 秒 PCIe Gen 7 CC,帶 SSC 抖動

- 符合 PCIe Gen 1 至 Gen 7 標準

- 可配置的 SSC

- 可編程 -0.05% 至 -3% 的下行價差和 ±0.025% 至 ±1.5% 的中心價差,或預設的 -0.1%、-0.25%、-0.3% 和 -0.5% 的下行價差

- 1 個輸入 (LMK3H2104),可旁路到任何輸出

- 最大啟動時間 5ms

- 當器件電源關閉時,故障安全輸入引腳可以拉高

- 靈活的電源

- 每個VDD引腳可以獨立連接到= 1.8、2.5或3.3V

- 每個VDDO引腳可以獨立連接,設置為1.8、2.5或3.3V

- -40 至 105°C 環境溫度

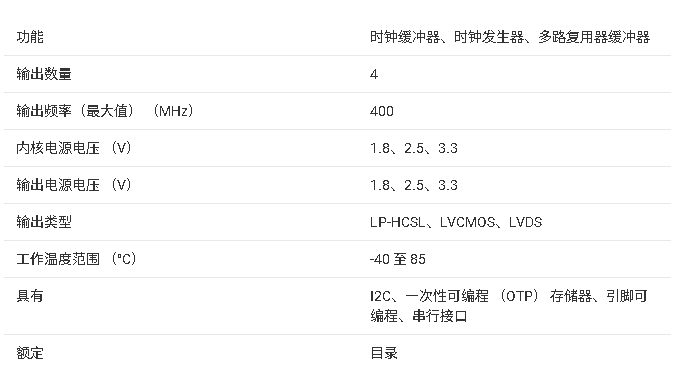

參數

?1. 產品概述?

LMK3H2104是一款基于BAW(體聲波)諧振器的低抖動時鐘發生器,無需外部晶體或振蕩器(XTAL/XO),專為PCIe Gen 1-7設計,同時支持通用時鐘生成。關鍵特性包括:

- ?集成BAW諧振器?:無需外部時鐘源。

- ?靈活輸出?:4路差分輸出(支持LP-HCSL、LVDS、LVCMOS等格式),最高頻率400MHz。

- ?超低抖動?:PCIe Gen 5/6/7下分別最大61fs、36.4fs、25.5fs(含SSC)。

- ?可編程SSC?:支持-0.05%至-3%下擴頻或±0.025%至±1.5%中心擴頻。

- ?快速啟動?:最大啟動時間5ms。

?2. 主要應用?

- 高性能計算服務器主板

- 網絡接口卡(NIC)、智能NIC及硬件加速

- PCIe Gen 1-7時鐘生成

- 通用時鐘生成與XTAL/XO替代

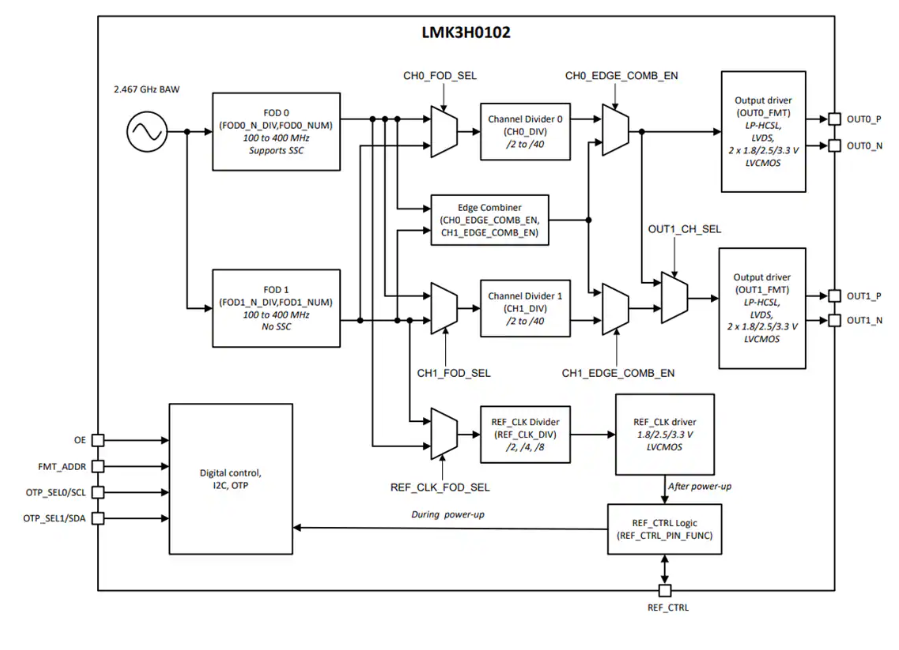

?3. 功能模塊?

- ?時鐘輸入?:1路差分輸入(可配置為單端或GPI)。

- ? FOD(分數輸出分頻器) ?:2個獨立FOD支持頻率靈活調整。

- ?輸出分配?:每路輸出可獨立選擇時鐘源(IN0、FOD0、FOD1或邊沿組合器)。

- ?控制接口?:支持I2C、OTP(一次性可編程存儲器)及GPI/GPIO引腳配置。

?4. 關鍵參數?

- ?電源電壓?:1.8V/2.5V/3.3V(各VDD/VDDO引腳獨立配置)。

- ?溫度范圍?:-40°C至105°C。

- ?封裝?:24引腳QFN(4mm×4mm)。

?5. 高級功能?

- ?動態OTP頁切換?:支持4種預編程配置的實時切換。

- ?輸出同步?:支持全同步、自同步或無同步模式。

- ?電源管理?:支持低功耗模式與復位模式。

- ?狀態監控?:提供時鐘丟失(LOS)、頻率錯誤檢測及CRC校驗等狀態信號。

?6. 設計支持?

- ?布局建議?:推薦隔離電源、優化去耦電容布局,并確保熱焊盤良好接地。

- ?應用示例?:典型PCIe應用中可生成多路100MHz LP-HCSL時鐘,相位噪聲性能優異(如100MHz下典型相位噪聲圖所示)。

?7. 文檔與支持?

該文檔全面覆蓋了LMK3H2104的硬件設計、功能配置及性能參數,適用于高速時鐘系統的集成與調試。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

分頻器

+關注

關注

43文章

537瀏覽量

53679 -

時鐘發生器

+關注

關注

1文章

353瀏覽量

70149 -

PCIe

+關注

關注

16文章

1470瀏覽量

88844 -

LVCMOS

+關注

關注

1文章

142瀏覽量

12030

發布評論請先 登錄

相關推薦

熱點推薦

符合PCIe Gen1,Gen2和Gen3標準的9端口PCIe時鐘發生器

SI52147-EVB,用于PoE無線接入點的時鐘發生器評估板。 Si52147是一款符合PCIe Gen1,Gen2和Gen3標準的9端口PCIe

發表于 08-27 14:27

Texas Instruments LMK3H0102無基準時鐘發生器數據手冊

Texas Instruments LMK3H0102無基準時鐘發生器是符合PCIe Gen 1至Gen 6標準的雙路輸出無基準時鐘發生器,支持擴頻

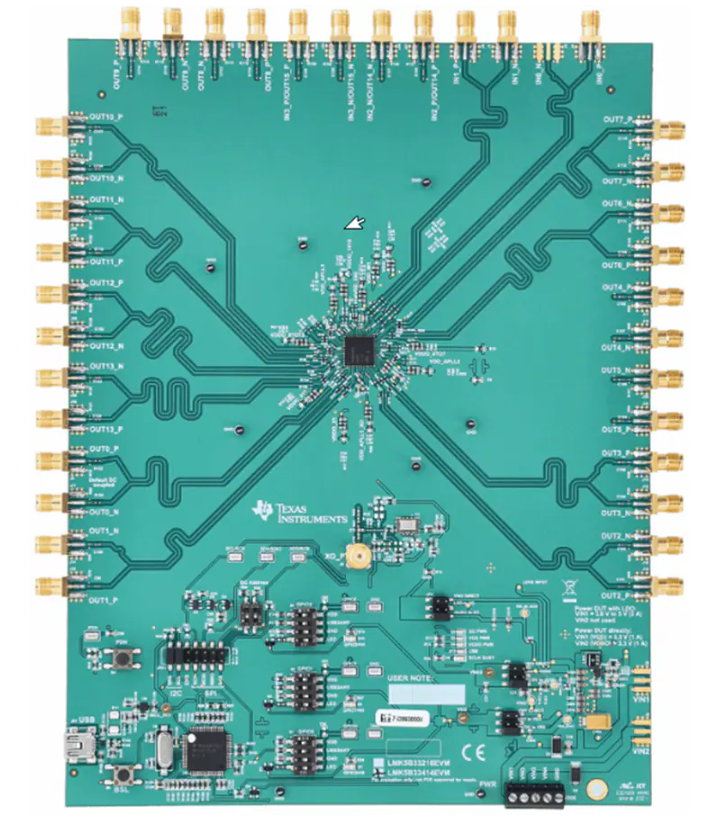

LMK5B33414EVM網絡時鐘發生器評估模塊技術解析

Texas Instruments LMK5B33414EVM時鐘發生器和合成器評估模塊 (EVM) 是一個用于對LMK5B33414網絡時鐘發生器和同步

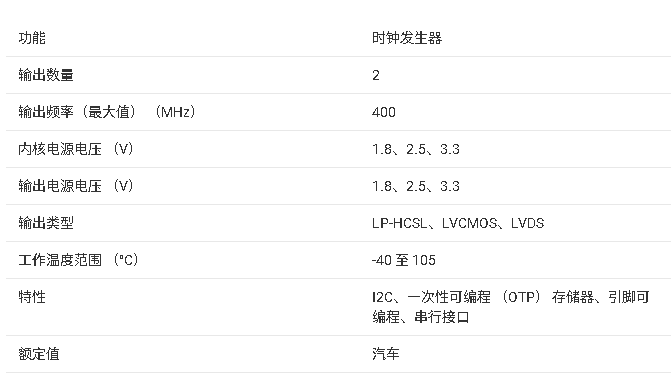

?LMK3H0102-Q1 參考無晶體時鐘發生器技術文檔總結

LMK3H0102-Q1 是一款符合 PCIe Gen 1 至 Gen 7 標準的 2 輸出無基準時鐘發生器,支持擴頻時鐘 (SSC)。該器件基于 TI 專有的體聲波 (BAW)

LMK3H2104與LMK3H2108:PCIe時鐘生成的理想之選

LMK3H2104與LMK3H2108:PCIe時鐘生成的理想之選 在電子設計領域,時鐘發生器對于確保系統的穩定運行至關重要。今天,我們要深

探索LMK3H2104和LMK3H2108:高性能時鐘發生器的卓越之選

探索LMK3H2104和LMK3H2108:高性能時鐘發生器的卓越之選 在當今的電子系統設計中,時鐘信號的穩定性、低抖動性以及靈活性是至關重要的。德州儀器(TI)推出的

探索LMK3H0102-Q1:PCIe時鐘生成的理想之選

探索LMK3H0102-Q1:PCIe時鐘生成的理想之選 在電子設計領域,時鐘發生器對于確保系統的穩定運行至關重要。今天,我們將深入探討一款高性能的

探索LMK3H0102:PCIe時鐘生成的理想選擇

探索LMK3H0102:PCIe時鐘生成的理想選擇 在電子設計領域,時鐘發生器對于確保系統的穩定運行至關重要。今天,我們將深入探討一款高性能的時鐘發

LMK03806:超低抖動時鐘發生器的技術解析與應用指南

LMK03806:超低抖動時鐘發生器的技術解析與應用指南 在電子設計領域,時鐘發生器的性能對于系統的穩定性和數據傳輸的準確性起著至關重要的作用。德州儀器(Texas Instrumen

9FGV0441:PCIe Gen 1 - 4 應用的低功耗時鐘發生器

9FGV0441:PCIe Gen 1 - 4 應用的低功耗時鐘發生器 在當今的電子設備中,時鐘發生器是確保系統穩定運行的關鍵組件之一。對于 PCI

9FGV0441:PCIe Gen 1 - 4應用的低功耗時鐘發生器

9FGV0441是一款專為PCIe Gen 1、2、3和4應用設計的4輸出極低功耗時鐘發生器。它集成了輸出端接,提供 (Zo = 100

?LMK3H2104 4-Output PCIe時鐘發生器技術文檔總結

?LMK3H2104 4-Output PCIe時鐘發生器技術文檔總結

評論