探究PLL1705與PLL1706:3.3V雙PLL多時鐘發生器的卓越性能

在電子設備的復雜世界中,時鐘發生器就像是設備的“心臟起搏器”,為整個系統提供穩定而精準的時鐘信號。今天,我們就來深入探討一下德州儀器(Texas Instruments)推出的兩款低相位噪聲、高性能的3.3V雙PLL多時鐘發生器——PLL1705和PLL1706。

文件下載:pll1705.pdf

關鍵特性一覽

輸入輸出特性

PLL1705和PLL1706采用27 - MHz主時鐘輸入,能產生多個系統時鐘輸出。以音頻系統時鐘為例,SCKO0固定為33.8688 MHz,SCKO1可在44.1 kHz時進行頻率選擇(16.9344 MHz或33.8688 MHz),SCKO2為256 fS,SCKO3為384 fS,并且支持多種采樣頻率(32、44.1、48、64、88.2、96 kHz)。這樣豐富的輸出選擇,能滿足不同音頻設備對時鐘頻率的多樣化需求。

誤差與抖動控制

這兩款芯片的輸出時鐘具有零PPM誤差,典型的時鐘抖動僅為50 ps,確保了輸出時鐘的高精度和穩定性。在對時鐘精度要求極高的音頻DAC和ADC等設備中,這樣低的抖動性能顯得尤為重要,能有效減少信號失真,提升音頻質量。

電源與控制方式

它們采用3.3V單電源供電,降低了功耗和設計復雜度。PLL1705支持并行控制,適合需要快速響應和簡單控制邏輯的應用場景;而PLL1706則支持串行控制,更便于與微控制器等設備進行通信,實現靈活的配置和控制。

電氣特性詳解

數字輸入輸出

數字輸入輸出方面,輸入邏輯與CMOS兼容,具有明確的輸入電壓范圍(VIH為0.7VDD,VIL為0.3VDD)和輸入電流限制(IIH和IIL)。輸出邏輯同樣為CMOS,輸出電壓和電流也有相應的規格要求(如VOH、VOL),以確保與其他數字電路的良好兼容性。

主時鐘特性

主時鐘頻率穩定在27 MHz左右(26.73 - 27.27 MHz),輸入電平(VIH、VIL)和輸入電流(IIH、IIL)都有嚴格的范圍限制。輸出電壓為3.5 Vp - p,上升時間和下降時間均為2.0 ns,占空比在45% - 55%(晶體振蕩)或50%(外部時鐘)之間,時鐘抖動典型值為50 ps,上電時間為0.5 - 1.5 ms。這些特性保證了主時鐘信號的質量和穩定性。

PLL交流特性

PLL交流特性方面,不同的系統時鐘輸出頻率根據采樣頻率進行調整,輸出上升時間和下降時間均為2.0 ns,占空比在45% - 55%之間,輸出時鐘抖動在50 - 100 ps之間。頻率穩定時間和上電時間也有明確的規格,確保了系統時鐘的快速穩定和可靠運行。

引腳功能與連接

引腳功能

芯片的引腳功能豐富多樣,包括模擬地(AGND)、數字地(DGND1 - 3)、電源引腳(VCC、VDD1 - 3)、時鐘輸出引腳(MCKO1、MCKO2、SCKO0 - 3)以及控制引腳(FS1、FS2、SR、CSEL等)。每個引腳都有其特定的功能,例如CSEL用于SCKO1頻率選擇控制,FS1和FS2在PLL1705中用于采樣頻率組控制,在PLL1706中則用于串行控制的數據輸入和位時鐘輸入。

連接注意事項

在連接時,要注意電源的旁路電容選擇和布局,建議使用一個公共接地連接以避免閂鎖或其他電源相關問題。對于主時鐘輸入,可以選擇晶體振蕩器或外部時鐘輸入,但如果使用外部時鐘,XT2必須開路。同時,為了避免影響PLL1705/6的抖動性能,建議在所有輸出時鐘上使用外部緩沖器。

工作原理剖析

時鐘生成機制

PLL1705/6由雙PLL時鐘和主時鐘發生器組成,從27 - MHz主時鐘生成四個系統時鐘和兩個緩沖的27 - MHz時鐘。主時鐘可以是晶體振蕩器或外部輸入,通過PLL的相位檢測、環路濾波和VCO等環節,實現對系統時鐘頻率的精確控制。

控制模式

PLL1705采用并行控制模式,通過FS1、FS2和SR引腳進行采樣頻率組選擇和采樣率選擇;PLL1706采用串行控制模式,通過ML、MC和MD三個引腳進行控制,通過16位程序寄存器實現各種功能的配置,如時鐘輸出的使能/禁用、采樣頻率和采樣率的選擇等。

應用領域與優勢

應用場景

PLL1705和PLL1706在MPEG - 2應用中表現出色,如DVD播放器、多媒體PC的DVD附加卡、數字HDTV系統和機頂盒等。它們能從27 - MHz視頻時鐘為CD - DA DSP、DVD DSP、卡拉OK DSP和DAC等提供音頻系統時鐘,滿足這些設備對時鐘信號的高精度和穩定性要求。

優勢體現

這兩款芯片通過消除外部組件,為客戶節省了成本和空間,同時實現了高性能音頻DAC和ADC所需的極低抖動性能。在實際應用中,它們能有效提升音頻設備的音質和穩定性,為用戶帶來更好的使用體驗。

作為電子工程師,在設計相關音頻設備時,我們需要充分考慮PLL1705和PLL1706的這些特性和優勢,根據具體的應用需求選擇合適的芯片和控制方式,合理進行引腳連接和電路布局,以確保設備的性能和穩定性。你在實際應用中是否遇到過類似時鐘發生器的設計挑戰呢?又是如何解決的呢?歡迎在評論區分享你的經驗和見解。

-

時鐘發生器

+關注

關注

1文章

306瀏覽量

70052

發布評論請先 登錄

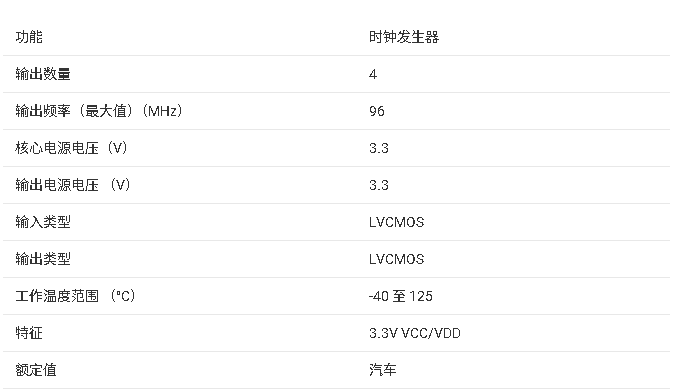

PLL1706 3.3V 雙路 PLL 多時鐘發生器

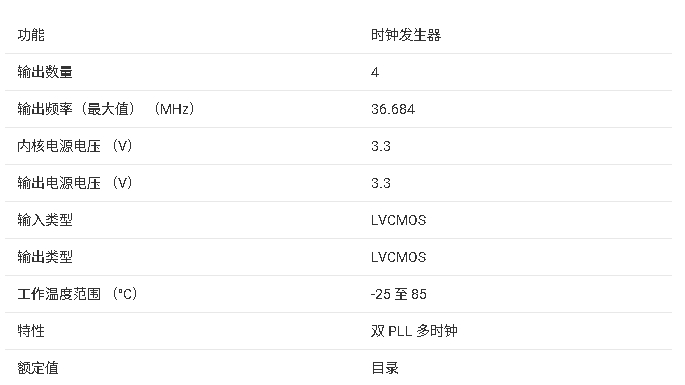

PLL1705 3.3V 雙路 PLL 多時鐘發生器

PLL1705/PLL1706雙通道PLL多時鐘發生器數據表

PLL1707/PLL1708 3.3V雙通道PLL多時鐘發生器數據表

探究PLL1705與PLL1706:3.3V雙PLL多時鐘發生器的卓越性能

探究PLL1705與PLL1706:3.3V雙PLL多時鐘發生器的卓越性能

評論