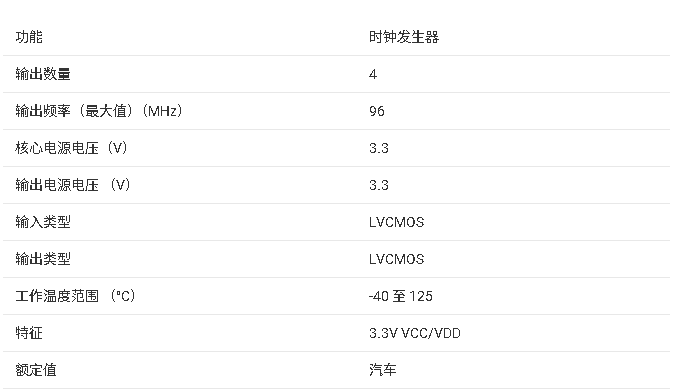

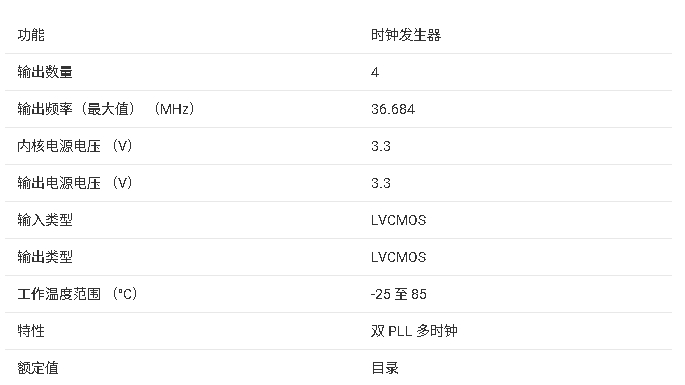

德州儀器PLL1707和PLL1708:低抖動多時鐘發生器的卓越之選

在電子設計領域,時鐘發生器是確保系統穩定運行的關鍵組件。今天,我們就來深入探討德州儀器(Texas Instruments)推出的兩款低成本、高性能的鎖相環(PLL)多時鐘發生器——PLL1707和PLL1708。

文件下載:pll1708.pdf

1. 特性亮點

1.1 時鐘輸入與輸出

- 這兩款芯片均采用27 - MHz主時鐘輸入,能夠產生四個系統時鐘和兩個27 - MHz緩沖時鐘。

- PLL1707和PLL1708在音頻系統時鐘生成上各有特點。PLL1707針對常規的采樣頻率(如32 kHz、44.1 kHz、48 kHz等)提供了精確的時鐘輸出;而PLL1708則支持更豐富的采樣頻率,包括16 kHz、22.05 kHz等,并且在SCKO1輸出上有更多的頻率可選配置。

1.2 低抖動與高精度

- 它們具備零PPM誤差輸出時鐘,能有效降低時鐘信號的相位噪聲。時鐘抖動典型值僅為50 ps,這種低抖動性能對于高性能音頻數模轉換器(DAC)和模數轉換器(ADC)至關重要,能夠確保音頻信號的高質量轉換。

1.3 電源與控制方式

- 采用3.3 - V單電源供電,降低了電源設計的復雜性和功耗。

- PLL1707采用并行控制方式,通過引腳FS1、FS2和SR等進行硬件控制;PLL1708則采用串行控制方式,通過三線接口(MS、MC、MD)實現軟件控制,這種差異為不同設計需求提供了多樣化的選擇。

1.4 封裝與溫度范圍

- 封裝形式為20引腳的SSOP(150 mil),并且是無鉛產品,符合環保要求。

- 工作溫度范圍為 - 25°C至85°C,能夠適應大多數工業和消費電子應用場景。

1.5 低抖動技術原理探討

時鐘抖動是指時鐘頻率的不穩定性,會造成數據傳輸的時序問題,甚至導致系統崩潰。PLL1707和PLL1708能實現低抖動性能,可能是在設計上對產生抖動的常見因素進行了有效控制。時鐘抖動通常由晶振、晶振驅動和包含時鐘的電路總線中傳輸的噪聲這三個方面的因素造成。德州儀器可能在晶振的選擇上采用了高精度、穩定性好的晶體,減少了由于晶振本身不穩定帶來的隨機抖動。在晶振驅動電路設計上,優化了電路結構,提高了驅動的穩定性。同時,對于電路總線中的噪聲,可能采用了濾波技術、合理的PCB布局和布線等方式,降低了噪聲對時鐘信號的干擾。例如,對于隨機抖動,可能采用了固體穩定潤層(TCXO)或電容篩選電路等濾波技術;對于周期性抖動,可能改進了電源抑制結構或使用了更佳的起始設計策略。

2. 電氣特性

2.1 數字輸入/輸出

- 輸入邏輯電平與CMOS兼容,VIH(邏輯高電平輸入)最小值為0.7VDD,VIL(邏輯低電平輸入)最大值為0.3VDD。

- 輸出邏輯電平在不同負載電流下有明確規定,如VOH(邏輯高電平輸出)在IOH = - 4 mA時為VDD - 0.4 V,VOL(邏輯低電平輸出)在IOL = 4 mA時為0.4 V。

2.2 主時鐘特性

- 主時鐘頻率范圍為26.73 MHz至27.27 MHz,典型值為27 MHz。

- 輸入電平VIH為0.7 VCC,VIL為0.3 VCC,輸入電流在不同輸入電壓下有相應的限制。

- 輸出電壓為Vp - p,上升時間和下降時間在20%至80%和80%至20%的VDD變化范圍內典型值為2.0 ns,占空比在晶體振蕩時為45% - 55%,外部時鐘時為50%。

2.3 PLL交流特性

- 不同的系統時鐘輸出(SCKO0 - SCKO3)有各自的頻率范圍和特性。例如,SCKO0輸出固定的33.8688 MHz時鐘,SCKO1在48 kHz采樣頻率下有多種可選頻率。

- 輸出上升時間和下降時間典型值為2.0 ns,輸出占空比為45% - 55%。

2.4 電氣特性優勢對實際應用的影響

PLL1707和PLL1708在電氣特性方面的優勢對實際應用有著重要影響。從數字輸入/輸出特性來看,與CMOS兼容的輸入邏輯電平使得它們能夠方便地與其他CMOS電路集成,降低了系統設計的復雜性。明確的輸出邏輯電平規定,保證了在不同負載電流下信號的穩定傳輸,提高了系統的可靠性。

主時鐘特性方面,精確的主時鐘頻率范圍和穩定的輸入輸出特性,為系統提供了穩定的時鐘源。例如,在一些對時鐘精度要求較高的音頻處理系統中,穩定的主時鐘能夠確保音頻信號的準確采樣和處理,避免出現音頻失真等問題。上升時間和下降時間短,占空比穩定,有助于提高信號的質量和時序精度。

PLL交流特性中,不同系統時鐘輸出的多樣化頻率選擇,能夠滿足不同應用場景的需求。在音頻系統中,可以根據不同的采樣頻率選擇合適的系統時鐘,實現高質量的音頻處理。輸出上升時間和下降時間短以及穩定的占空比,也有助于減少信號的失真和干擾,提高系統的性能。

3. 引腳功能與控制方式

3.1 引腳功能

- 兩款芯片的引腳功能有相似之處,也有差異。AGND為模擬地,VCC、VDD1 - VDD3為電源引腳,提供3.3 V電源。

- MCKO1和MCKO2輸出27 - MHz主時鐘,SCKO0 - SCKO3為系統時鐘輸出。

- 對于PLL1707,FS1、FS2和SR用于控制采樣頻率和采樣率,CSEL用于選擇SCKO1的頻率;對于PLL1708,MC、MD和MS用于串行控制,實現更多的功能配置。

3.2 控制方式

- PLL1707(并行模式):通過硬件引腳進行控制,操作簡單直觀。例如,通過FS1和FS2的不同電平組合可以選擇不同的采樣頻率組,SR引腳可以選擇采樣率,CSEL引腳可以選擇SCKO1的頻率。

- PLL1708(串行模式):采用三線接口進行串行控制,具有更高的靈活性。通過向16位程序寄存器寫入數據,可以實現采樣頻率選擇、采樣率選擇、時鐘輸出使能/禁用、電源管理以及SCKO1配置等功能。

4. 不同控制方式在實際應用中的選擇依據

在實際應用中選擇PLL1707的并行控制方式還是PLL1708的串行控制方式,需要綜合多方面因素考慮。從設計復雜度來看,如果設計團隊更熟悉硬件電路設計,且對控制邏輯的實時性要求較高,那么PLL1707的并行模式可能是更好的選擇。因為并行控制通過硬件引腳直接操作,不需要復雜的軟件編程,邏輯清晰,容易實現和調試,能夠快速響應控制信號的變化。

若設計需要實現復雜的功能配置和靈活的參數調整,并且系統具備一定的軟件處理能力,那么PLL1708的串行模式更具優勢。串行控制可以通過軟件編程向程序寄存器寫入不同的數據,實現多種功能的組合,例如可以根據不同的應用場景動態調整采樣頻率、時鐘輸出使能等,增強了系統的靈活性和可擴展性。

從成本角度考慮,如果對成本較為敏感且功能需求相對簡單,PLL1707的并行控制方式可以減少軟件設計和調試的成本,同時也不需要額外的串行接口控制器,降低了硬件成本。而對于一些對功能要求高、需要頻繁更改參數的高端應用,雖然PLL1708的串行控制可能需要增加一些軟件設計和串行接口的成本,但它帶來的功能優勢能夠滿足系統的需求,從整體性能和長遠來看可能更具性價比。 此外,在對系統體積有嚴格要求的應用中,PLL1708的串行控制方式可能更合適,因為它減少了硬件引腳的使用,有利于縮小PCB板的面積,實現小型化設計。

5. 工作原理

5.1 時鐘生成

- 芯片內部包含雙PLL時鐘和主時鐘發生器,能夠從27 - MHz主時鐘生成四個系統時鐘和兩個27 - MHz緩沖時鐘。

- 主時鐘可以是連接在XT1和XT2之間的晶體振蕩器,也可以是外部輸入到XT1的時鐘信號。當使用外部主時鐘時,XT2必須開路。

5.2 系統時鐘輸出控制

- SCKO0輸出固定的33.8688 - MHz時鐘,SCKO1的輸出頻率可以通過硬件或軟件控制進行選擇,如256 fS、384 fS、512 fS或768 fS(fs = 48 kHz)。

- SCKO2和SCKO3的輸出頻率由采樣頻率(fs)決定,在不同的采樣頻率下有相應的輸出頻率。

6. 應用場景

6.1 MPEG - 2應用

- 在基于MPEG - 2的系統中,如DVD刻錄機、硬盤錄像機、DVD播放機、多媒體PC的DVD擴展卡、數字高清電視系統和機頂盒等,PLL1707和PLL1708能夠從27 - MHz視頻時鐘為CD - DA DSP、DVD DSP、卡拉OK DSP、ADC和DAC等提供音頻系統時鐘。

6.2 音頻處理系統

- 其低抖動、高精度的時鐘輸出特性,使得它們在音頻處理系統中表現出色,能夠確保音頻信號的準確采樣和處理,提高音頻質量。

7. 在音頻處理系統中的應用案例和效果

在音頻處理系統中,PLL1707和PLL1708憑借其出色的性能有著廣泛的應用。雖然目前未找到直接的應用案例,但我們可以從其特性來推測可能的效果。

在專業音頻錄制設備中,如高端的數字音頻工作站(DAW),對時鐘的精度和穩定性要求極高。PLL1707和PLL1708的低抖動特性可以確保音頻信號的準確采樣。例如,在多軌錄音時,穩定的時鐘能夠保證各軌音頻信號的同步,避免出現相位偏差,從而提高錄制音頻的質量,使音頻更加純凈、清晰。

在音頻播放設備中,如高保真音響系統,這兩款芯片可以為DAC提供精確的時鐘信號。精確的時鐘有助于DAC更準確地還原音頻信號,減少失真和噪聲,提升音頻的動態范圍和音質表現,讓聽眾能夠享受到更逼真、細膩的音樂。

在一些音頻處理算法較為復雜的系統中,如音頻混音器、音頻特效處理器等,PLL1707和PLL1708的高速時鐘輸出和可靈活配置的特性能夠滿足系統對數據處理速度和多樣性的要求。它可以根據不同的算法需求,快速調整采樣頻率和時鐘輸出,確保音頻處理的實時性和準確性。

8. 注意事項

8.1 ESD防護

- 由于該集成電路容易受到靜電放電(ESD)的損害,在操作和安裝過程中必須采取適當的靜電防護措施,如佩戴防靜電手環、使用防靜電工作臺等。

8.2 電源設計

- 建議使用一個公共接地連接,以避免閂鎖效應或其他與電源相關的問題。

- 電源應盡可能靠近芯片進行旁路處理,以減少電源噪聲對芯片性能的影響。

8.3 負載電容

- 為了獲得良好的抖動性能,應盡量減少時鐘輸出的負載電容。建議通過緩沖器驅動時鐘輸出,特別是在SCKO0和SCKO1有較重負載的情況下,并通過分離或插入防護圖案來減少相互干擾。

總之,德州儀器的PLL1707和PLL1708以其豐富的功能、出色的性能和靈活的控制方式,為電子工程師在音頻和視頻系統設計中提供了優秀的解決方案。在實際應用中,合理選擇和使用這兩款芯片,并注意相關的設計要點,能夠為系統帶來穩定、可靠的時鐘信號,提升整個系統的性能。你在設計中是否使用過類似的時鐘發生器呢?歡迎在評論區分享你的經驗和見解。

-

德州儀器

+關注

關注

123文章

1970瀏覽量

145125

發布評論請先 登錄

PLL1708 3.3V 雙路 PLL 多時鐘發生器

PLL1707 3.3V 雙路 PLL 多時鐘發生器

PLL1707/PLL1708 3.3V雙通道PLL多時鐘發生器數據表

德州儀器PLL1707和PLL1708:低抖動多時鐘發生器的卓越之選

德州儀器PLL1707和PLL1708:低抖動多時鐘發生器的卓越之選

評論