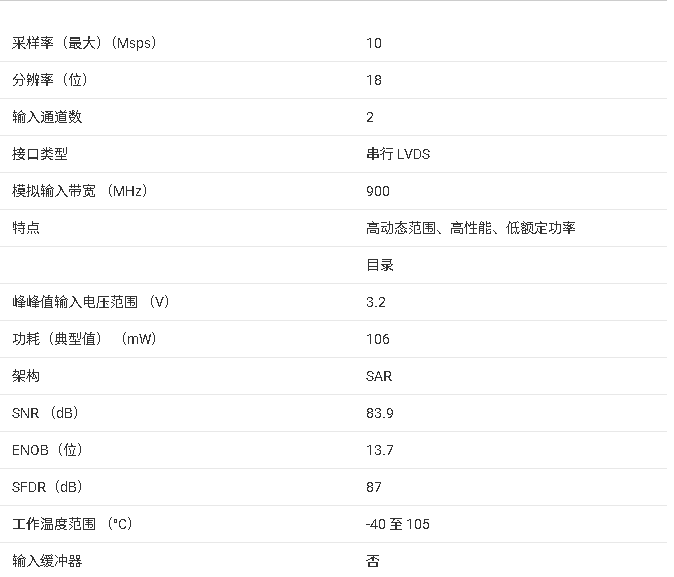

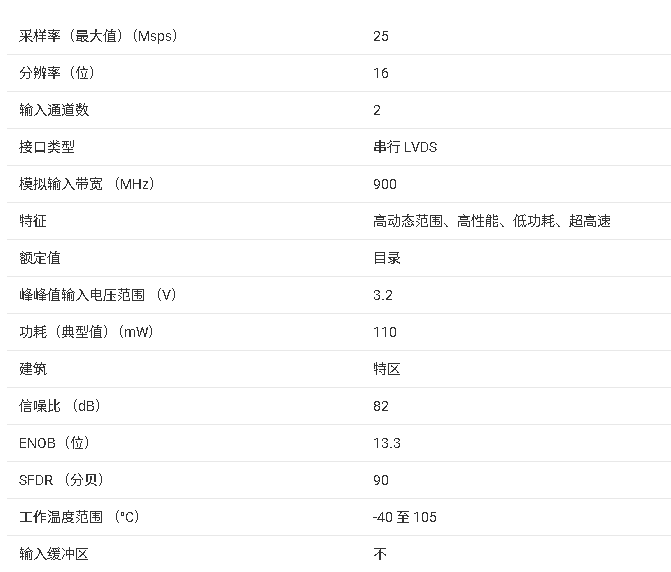

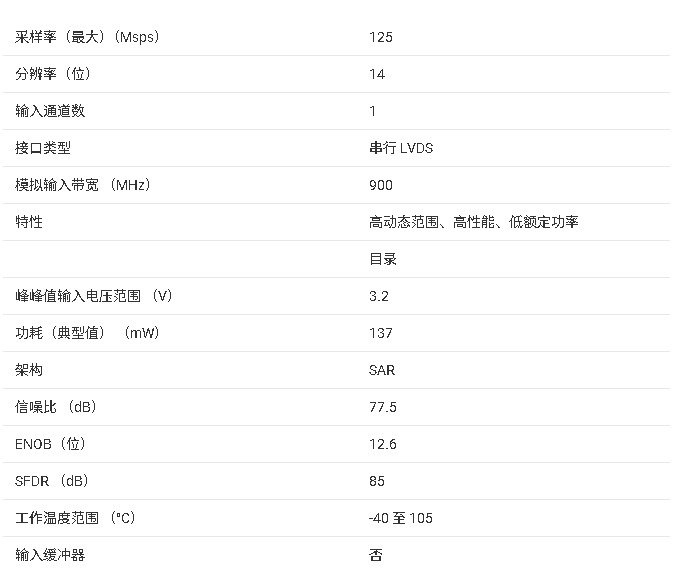

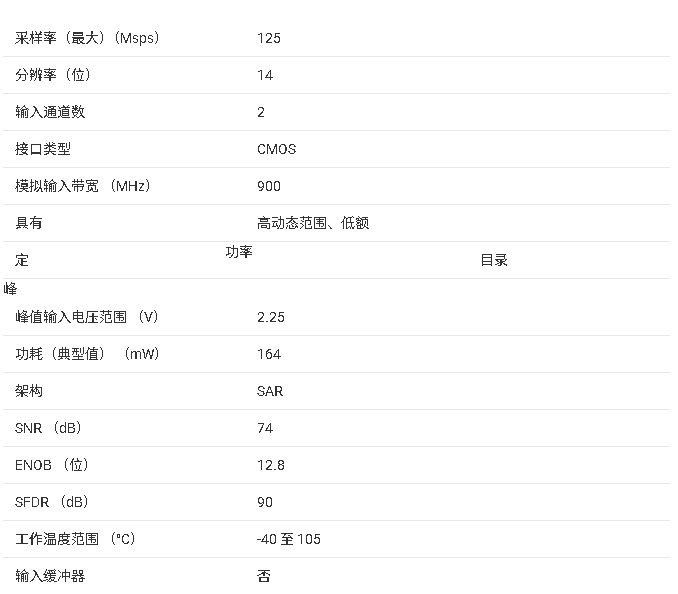

ADC3561、ADC3562、ADC3563 (ADC356x) 系列器件是一款低噪聲、超低功耗、16 位、10 MSPS 至 65 MSPS 的高速模數(shù)轉(zhuǎn)換器 (ADC)。這些器件專為低功耗而設(shè)計(jì),可提供–158 dBFS/Hz的噪聲頻譜密度,并結(jié)合出色的線性度和動(dòng)態(tài)范圍。ADC356x 提供良好的直流精度和 IF 采樣支持,使該器件適用于廣泛的應(yīng)用。高速控制環(huán)路受益于僅一個(gè)時(shí)鐘周期的短延遲。ADC在65 MSPS時(shí)僅消耗122 mW,功耗在較低采樣率下也能很好地?cái)U(kuò)展。

*附件:adc3562.pdf

ADC356x 使用串行 LVDS (SLVDS) 接口輸出數(shù)據(jù),從而最大限度地減少數(shù)字互連的數(shù)量。該設(shè)備支持雙通道、單通道和半通道選項(xiàng)。ADC356x 和 ADC358x 是一個(gè)引腳兼容系列,具有 16 位和 18 位分辨率以及不同的速度等級(jí)。這些器件采用 40 引腳 QFN 封裝 (5 x 5 mm),支持 -40 至 +105?C 的擴(kuò)展工業(yè)溫度范圍。

特性

- 16位10MSPS至65MSPS ADC

- 本底噪聲:–158 dBFS/Hz

- 低功耗:77 mW (10 MSPS) 至 122 mW (65 MSPS)

- 延遲:1個(gè)時(shí)鐘周期(1線SLVDS)

- 指定的 16 位,無缺失碼

- INL:± 3 LSB;DNL:± 0.7 LSB

- 參考:外部或內(nèi)部

- 輸入帶寬:900 MHz (3 dB)

- 工業(yè)溫度范圍:–40°C 至 +105°C

- 片內(nèi)雙頻數(shù)字濾波器(可選)

- 抽取 2、4、8、16、32

- 32 位 NCO

- 串行LVDS數(shù)字接口(2線、1線和1/2線)

- 小尺寸:40-WQFN(5 mm × 5 mm)封裝

- 光譜性能(f

在= 10 MHz):- 信噪比:81.9 dBFS

- SFDR:95dBc HD2、HD3

- SFDR:100-dBFS 最差雜散

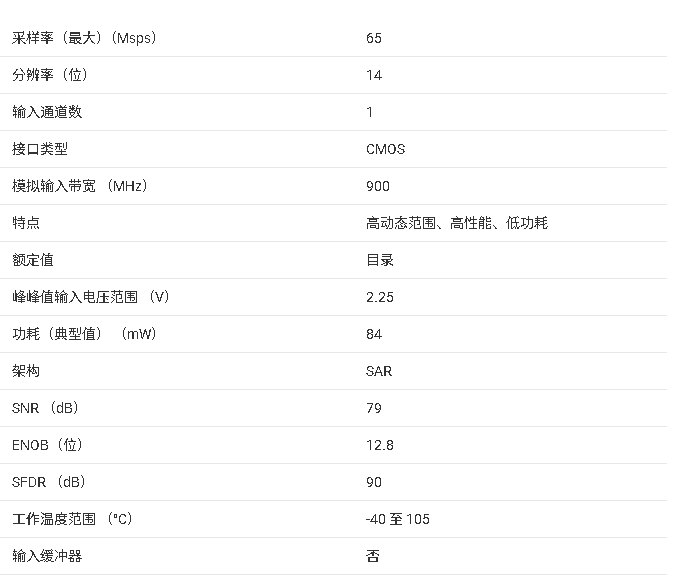

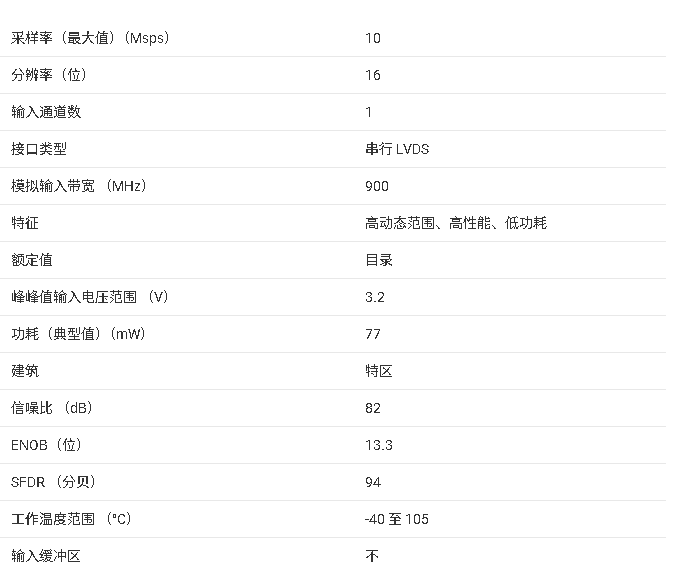

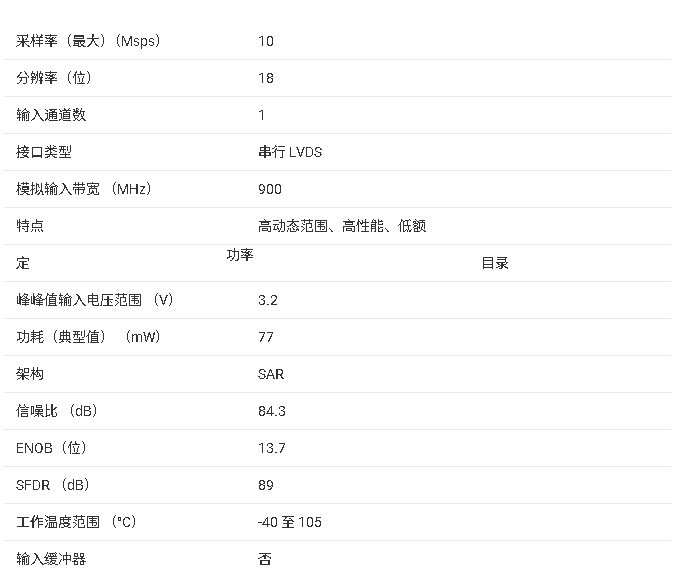

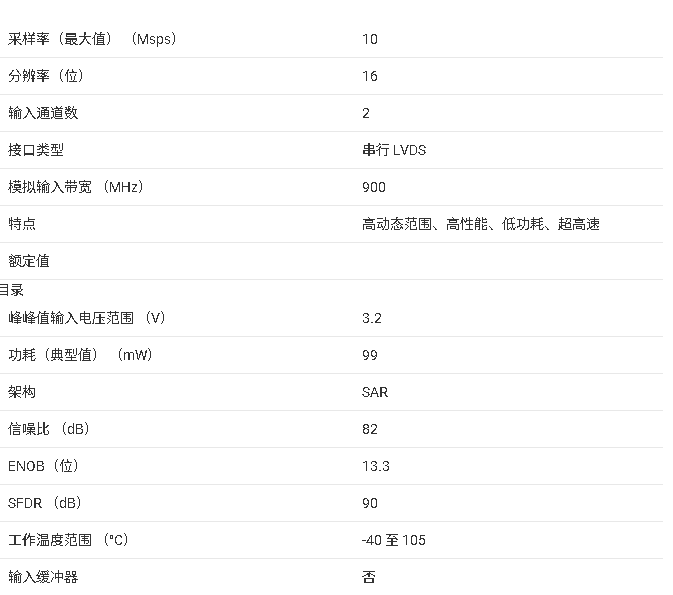

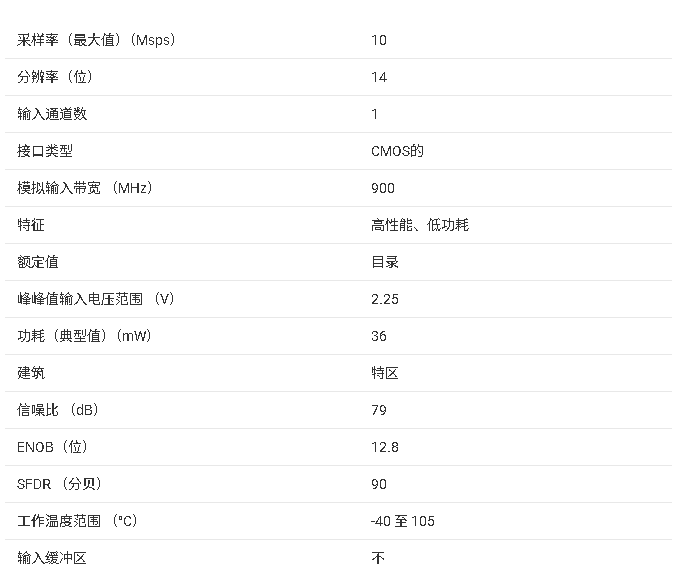

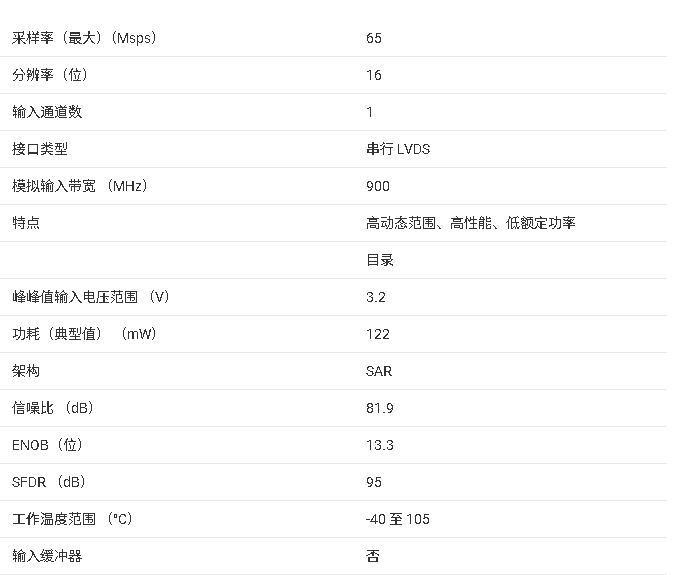

參數(shù)

方框圖

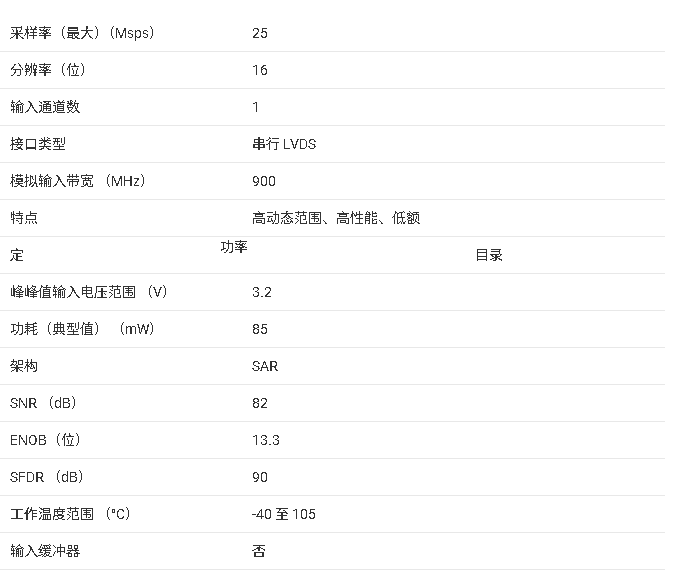

一、產(chǎn)品定位與核心屬性

ADC3562 是德州儀器 ADC356x 系列中的 16 位高速模數(shù)轉(zhuǎn)換器(ADC),專為低功耗、高動(dòng)態(tài)性能場(chǎng)景設(shè)計(jì),采樣速率固定為 25 MSPS,采用 40 引腳 WQFN(5mm×5mm)封裝,支持 - 40°C 至 + 105°C 工業(yè)級(jí)溫度范圍。其核心優(yōu)勢(shì)在于平衡了低噪聲(噪聲基底 - 154 dBFS/Hz)、低功耗(1 線 SLVDS 接口下典型功耗 85 mW)與高線性度,適用于工業(yè)監(jiān)測(cè)、電力質(zhì)量分析儀、儀器儀表等對(duì)采樣速率和能效有中等需求的場(chǎng)景,且與同系列 ADC3561(10 MSPS)、ADC3563(65 MSPS)引腳兼容,便于方案選型迭代。

二、關(guān)鍵性能參數(shù)

1. 精度與線性度

- 分辨率與完整性 :16 位無缺失碼,確保全量程信號(hào)轉(zhuǎn)換無遺漏。

- 線性誤差 :微分非線性(DNL)±0.4 LSB(典型值)、±0.85 LSB(最大值),積分非線性(INL)±3 LSB(典型值)、±5 LSB(最大值),有效降低信號(hào)失真。

- 直流特性 :偏移誤差(VOS_ERR)最小 32 LSB、最大 ±135 LSB,偏移漂移(VOS_DRIFT)0.009 LSB/°C;增益誤差(GAINERR)外接 1.6V 參考時(shí)典型值 - 0.25% FSR,內(nèi)置參考時(shí) - 1.9% FSR,增益漂移(GAINDRIFT)外接參考時(shí) 0.08 ppm/°C,溫漂特性優(yōu)異。

2. 動(dòng)態(tài)性能(典型值,外接 1.6V 參考,-1 dBFS 差分輸入)

- 信噪比(SNR) :1.1 MHz 輸入時(shí) 82.0 dBFS,10 MHz 輸入時(shí) 81.9 dBFS,20 MHz 輸入時(shí) 81.6 dBFS,40 MHz 輸入時(shí) 78.6 dBFS,高頻場(chǎng)景下仍保持良好信號(hào)純凈度。

- 無雜散動(dòng)態(tài)范圍(SFDR) :1.1 MHz 輸入時(shí) 86 dBc,5 MHz 輸入時(shí) 90 dBc(最大值),10 MHz 輸入時(shí) 89 dBc,有效抑制雜散干擾。

- 總諧波失真(THD) :1.1 MHz 輸入時(shí) 85 dBc,5 MHz 輸入時(shí) 89 dBc(最大值),20 MHz 輸入時(shí) 83 dBc,低失真特性適配高精度信號(hào)采集。

- 噪聲譜密度(NSD) :無輸入信號(hào)時(shí) - 154 dBFS/Hz,為微弱信號(hào)檢測(cè)提供基礎(chǔ)。

3. 功耗與接口特性

- 功耗 :模擬電源電流(I_AVDD)典型值 20 mA、最大值 27 mA;1 線 SLVDS 接口下 I/O 電源電流(I_IOVDD)典型值 27 mA、最大值 43 mA,1/2 擺幅模式下可降至 21 mA,功耗靈活可控。

- 延遲 :1 線 / 1/2 線 SLVDS 接口僅 1 個(gè)時(shí)鐘周期,2 線 SLVDS 接口 2 個(gè)時(shí)鐘周期,適配高速控制環(huán)路。

- 輸入帶寬 :3 dB 帶寬 900 MHz,支持中頻(IF)采樣,無需額外降頻電路。

三、硬件設(shè)計(jì)關(guān)鍵信息

1. 引腳功能與配置

- 模擬輸入 :AINP(引腳 12,正端)、AINM(引腳 13,負(fù)端)為差分輸入,共模電壓(VCM,引腳 8)固定 0.95 V(典型值),輸入阻抗 8 kΩ(100 kHz 時(shí))、電容 7 pF(100 kHz 時(shí)),滿量程輸入 3.2 Vpp(差分),需匹配驅(qū)動(dòng)電路輸出范圍。

- 電源引腳 :AVDD(引腳 5、15、36)為模擬 1.8 V 電源,IOVDD(引腳 21、30)為數(shù)字接口 1.8 V 電源,需獨(dú)立供電避免數(shù)字噪聲耦合至模擬電路;GND(含底部散熱焊盤)與 IOGND(引腳 26)需單點(diǎn)連接,降低接地噪聲。

- 控制與通信引腳 :

2. 參考電壓與時(shí)鐘設(shè)計(jì)

- 參考電壓選項(xiàng) :

- 外接 1.6 V 參考:直接接入 VREF(引腳 2),需搭配 10 μF+0.1 μF 旁路電容,負(fù)載電流約 1 mA。

- 外接 1.2 V 參考:接入 REFBUF(引腳 4),通過內(nèi)部增益緩沖生成 1.6 V 參考,負(fù)載電流 < 100 μA,需在 REFBUF 與 REFGND(引腳 3)間加 10 μF+0.1 μF 旁路電容。

- 內(nèi)置參考:生成 1.6 V 參考,輸出阻抗 8 Ω,額外消耗 1 mA 模擬電流,適合對(duì)成本敏感、精度要求中等的場(chǎng)景。

- 時(shí)鐘輸入 :支持差分(CLKP 引腳 6、CLKM 引腳 7)與單端輸入,差分模式可 AC 耦合(內(nèi)部自偏置),單端模式需 DC 耦合至 0.9 V 中心電壓,且未使用端需 AC 接地;時(shí)鐘占空比推薦 40%-60%,高擺率時(shí)鐘可降低孔徑抖動(dòng)(典型值 180 fs)。

3. 數(shù)字接口與數(shù)據(jù)處理

- SLVDS 接口 :支持 2 線、1 線、1/2 線模式,1 線模式下數(shù)據(jù)速率 400 MBPS(25 MSPS 時(shí)),2 線模式下 200 MBPS/lane,需外部輸入 DCLKIN 時(shí)鐘(差分,V_ID 200-650 mVpp),且與采樣時(shí)鐘頻率鎖定。

- 數(shù)字下變頻器(DDC) :可選 2/4/8/16/32 倍抽取,支持實(shí)抽取(低通濾波)與復(fù)抽取(含 32 位 NCO,頻率可調(diào)范圍 - FS/2 至 FS/2),復(fù)抽取時(shí)可通過 DB0/1 接口實(shí)現(xiàn)雙頻段輸出,抽取后延遲增加 21-23 個(gè)輸出時(shí)鐘周期(依抽取倍數(shù)而定)。

四、功能模塊與配置

1. 模擬前端優(yōu)化

- 自動(dòng)調(diào)零(Auto-Zero) :默認(rèn)啟用,可通過 SPI 寄存器(0x11,D0)關(guān)閉,有效降低 1/f 閃爍噪聲,提升低頻信號(hào)采集精度,4M 點(diǎn) FFT 測(cè)試顯示啟用后低頻段噪聲抑制顯著。

- 采樣干擾濾波器 :推薦根據(jù)輸入頻率選擇:DC-30 MHz 場(chǎng)景用 33 Ω 電阻 + 180 nH 電感 + 100 pF 電容;30-70 MHz 場(chǎng)景用 33 Ω 電阻 + 120 nH 電感 + 100 pF+82 pF 電容,吸收采樣開關(guān)產(chǎn)生的毛刺。

2. 數(shù)字功能配置

- 輸出格式化 :支持 14/16/18/20 位輸出分辨率,14 位時(shí)截?cái)?2 個(gè) LSB;數(shù)據(jù)格式可通過 SPI 寄存器(0x8F、0x92)配置為二進(jìn)制補(bǔ)碼(默認(rèn))或偏移二進(jìn)制。

- 測(cè)試模式 :支持斜坡(RAMP)、自定義固定模式,通過 0x14-0x16 寄存器配置,用于數(shù)字接口連通性測(cè)試,斜坡步長(zhǎng)需匹配 ADC 原生分辨率(16 位對(duì)應(yīng) 00100)。

- 電源管理 :支持全局電源關(guān)斷(功耗低至 5 mW,內(nèi)置參考)與局部模塊關(guān)斷(如時(shí)鐘緩沖、參考放大器),通過 0x08、0x09、0x0D 寄存器配置,平衡功耗與喚醒時(shí)間。

3. SPI 寄存器關(guān)鍵配置

- 接口配置 :0x07 寄存器選擇輸出接口映射(16 位 1 線 SLVDS 對(duì)應(yīng) 0x6C),0x13 寄存器加載 E-Fuse 配置(需等待 1 ms),0x19 寄存器設(shè)置 FCLK 源與分頻(復(fù)抽取時(shí) FCLK_SRC=1)。

- 抽取配置 :0x24 寄存器使能 DDC(D1=1)與數(shù)字通路(D2=1),0x25 寄存器設(shè)置抽取倍數(shù)(如 8 倍復(fù)抽取對(duì)應(yīng) 0x30),0x2A-0x2D、0x31-0x34 寄存器配置 NCO 頻率。

- 增益與相位 :0x26 寄存器設(shè)置 mixer 增益(復(fù)抽取推薦 6 dB 補(bǔ)償混合損耗),0x27、0x2E 寄存器調(diào)整 I/Q 輸出順序與延遲。

五、應(yīng)用設(shè)計(jì)與布局建議

1. 典型應(yīng)用電路

以工業(yè)監(jiān)測(cè)系統(tǒng)為例,前端采用 THS4541 全差分放大器(支持 DC-70 MHz,3.3 V/-1 V 供電時(shí)輸出擺幅 6.8 Vpp),搭配 DC-30 MHz 采樣干擾濾波器,ADC 配置外接 1.6 V 參考(VREF 引腳接 REF5016),數(shù)據(jù)通過 1 線 SLVDS 傳輸至 FPGA,時(shí)鐘采用差分晶振(如 Si5351,抖動(dòng) < 100 fs),確保動(dòng)態(tài)性能達(dá)標(biāo)。

2. 電源設(shè)計(jì)

- 推薦架構(gòu) :采用 “開關(guān)電源 + LDO” 組合,如 TPS62821(開關(guān)電源,效率 90%+)+TPS7A4701(LDO,噪聲 < 10 μVrms),AVDD 與 IOVDD 獨(dú)立供電,電源路徑上串聯(lián)鐵氧體磁珠(如 BLM18PG102SN1)抑制高頻噪聲。

- 旁路電容 :AVDD、IOVDD 引腳旁就近放置 10 μF(鉭電容)+0.1 μF(陶瓷電容),VREF 引腳旁放置 10 μF+0.1 μF 陶瓷電容,減少電壓紋波。

3. 布局 Guidelines

- 模擬信號(hào) :AINP/AINM、CLKP/CLKM 采用 100 Ω 差分布線,長(zhǎng)度匹配(誤差 <50 mil),避免過孔;與數(shù)字信號(hào)(如 DA0/1、DB0/1)間距> 200 mil,減少串?dāng)_。

- 參考電壓 :VREF、REFBUF 引腳旁路電容直接焊接在頂層,無過孔,REFGND 與模擬地單點(diǎn)連接。

- 散熱 :底部散熱焊盤(GND PAD)需通過過孔連接至內(nèi)層地平面,確保結(jié)溫(T_J)不超過 105°C(推薦結(jié)溫 < 85°C 以延長(zhǎng)壽命)。

-

adc

+關(guān)注

關(guān)注

100文章

7511瀏覽量

555913 -

模數(shù)轉(zhuǎn)換器

+關(guān)注

關(guān)注

26文章

4013瀏覽量

130100 -

控制環(huán)路

+關(guān)注

關(guān)注

1文章

55瀏覽量

9816 -

噪聲頻譜

+關(guān)注

關(guān)注

0文章

28瀏覽量

2252

發(fā)布評(píng)論請(qǐng)先 登錄

使用ADC3562的時(shí)候,電復(fù)位之后默認(rèn)兩線制,同時(shí)DA0和DA1均有數(shù)據(jù)輸出,但是沒有給輸入,為什么?

ADC3568/ADC3569 ADC 產(chǎn)品文檔總結(jié)

ADC3669 產(chǎn)品技術(shù)文檔總結(jié)

ADC3683-SP 技術(shù)文檔總結(jié)

ADC354x 系列技術(shù)文檔總結(jié)

ADC3561/3562/3563 技術(shù)文檔總結(jié)

ADC3581 技術(shù)文檔總結(jié)

ADC3661 技術(shù)文檔總結(jié)

ADC3681 技術(shù)文檔總結(jié)

ADC3662 技術(shù)文檔總結(jié)

ADC3564 技術(shù)文檔總結(jié)

ADC3644 技術(shù)文檔總結(jié)

ADC3541技術(shù)文檔總結(jié)

ADC3563 單通道、16位、65MSPS、低噪聲、超低功耗、低延遲ADC技術(shù)手冊(cè)

ADC3562 技術(shù)文檔總結(jié)

ADC3562 技術(shù)文檔總結(jié)

評(píng)論