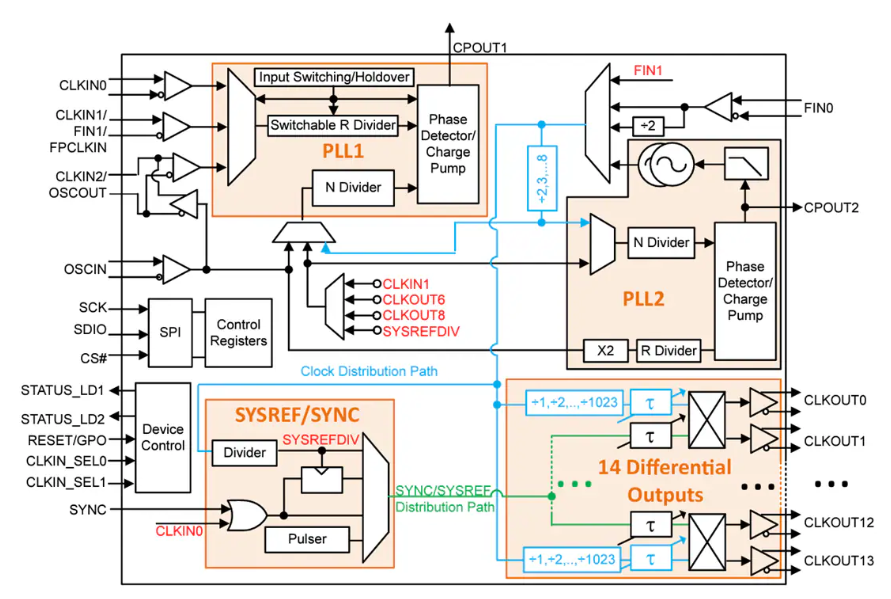

該CDC7005是一款高性能、低相位噪聲和低偏斜時(shí)鐘同步器和抖動(dòng)清除器,可將壓控晶體振蕩器(VCXO)頻率與基準(zhǔn)時(shí)鐘同步。可編程預(yù)分頻器 M 和 N 為參考時(shí)鐘與 VCXO 的頻率比提供了高度的靈活性:VCXO_IN/REF_IN = (NxP)/M。VCXO_IN時(shí)鐘的工作頻率高達(dá) 800 MHz。通過(guò)選擇外部VCXO和環(huán)路濾波器組件,可以調(diào)整PLL環(huán)路帶寬和阻尼因子,以滿足不同的系統(tǒng)要求。五個(gè)差分LVPECL輸出中的每一個(gè)都可通過(guò)串行外設(shè)接口(SPI)進(jìn)行編程。SPI允許單獨(dú)控制每個(gè)輸出的頻率和使能/禁用狀態(tài)。該器件在 3.3V 環(huán)境中運(yùn)行。內(nèi)置鎖存器確保所有輸出同步。

該CDC7005的工作溫度范圍為 –40°C 至 85°C。

*附件:cdc7005.pdf

特性

- 高性能 1:5 PLL 時(shí)鐘同步器

- 兩個(gè)時(shí)鐘輸入:VCXO_IN時(shí)鐘與REF_IN時(shí)鐘同步

- 同步頻率高達(dá) 800 MHz (VCXO_IN)

- 支持五個(gè)差分LVPECL輸出

- 每個(gè)輸出頻率可通過(guò) x1、/2、/4、/8 /16 進(jìn)行選擇

- 所有輸出都是同步的

- 集成低噪聲OPA,用于外部低通濾波器

- 低 PLL 環(huán)路帶寬的高效抖動(dòng)屏蔽

- 低相位噪聲特性

- 相位調(diào)整的可編程延遲

- 預(yù)分流器環(huán)帶寬調(diào)整

- SPI可控分頻設(shè)置

- 上電控制強(qiáng)制LVPECL輸出在VCC <1.5 V時(shí)為3態(tài)

- 3.3V 電源

- 采用 64 引腳 BGA(0.8 mm 間距 - ZVA)或 48 引腳 QFN (RGZ) 封裝

- 工業(yè)溫度范圍 –40°C 至 85°C

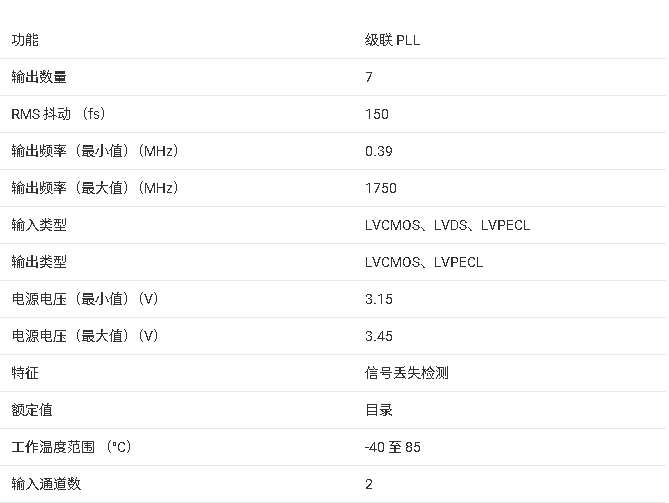

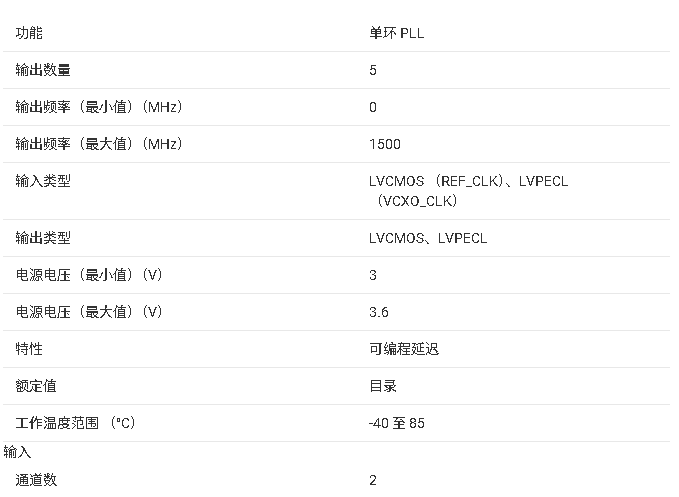

參數(shù)

?1. 產(chǎn)品概述?

CDC7005是德州儀器(TI)推出的3.3V高性能時(shí)鐘合成器與抖動(dòng)清除器,專為高頻時(shí)鐘同步設(shè)計(jì),具有以下核心特性:

- ?同步功能?:支持兩路時(shí)鐘輸入(VCXO_IN與REF_IN),最高同步頻率達(dá)800 MHz(VCXO_IN)。

- ?輸出配置?:提供5路差分LVPECL輸出,每路可通過(guò)SPI編程選擇分頻比(×1、/2、/4、/8、/16),輸出相位噪聲低且支持可調(diào)延遲。

- ?集成組件?:內(nèi)置低噪聲運(yùn)算放大器(OPA)用于外部低通濾波器設(shè)計(jì),支持靈活的環(huán)路帶寬調(diào)整。

- ?控制接口?:SPI可編程接口,支持分頻比、延遲、電荷泵電流等參數(shù)配置。

?2. 關(guān)鍵特性?

- ?高性能PLL?:支持頻率比VCXO_IN/REF_IN = (N×P)/M,通過(guò)外部VCXO和濾波器組件可定制環(huán)路帶寬。

- ?低抖動(dòng)與低偏斜?:優(yōu)化的相位噪聲性能,輸出偏斜低至30 ps(同頻模式下)。

- ?電源管理?:3.3V供電,工業(yè)級(jí)溫度范圍(-40°C至85°C),支持上電輸出三態(tài)保護(hù)。

?3. 封裝與引腳?

- ?封裝選項(xiàng)?:64引腳BGA(0.8 mm間距)或48引腳QFN(RGZ)。

- ?關(guān)鍵引腳?:

- ?控制接口?:CTRL_LE(SPI使能)、CTRL_CLK(時(shí)鐘)、CTRL_DATA(數(shù)據(jù))。

- ?狀態(tài)指示?:STATUS_LOCK(鎖相狀態(tài))、STATUS_REF/VCXO(輸入時(shí)鐘有效性)。

- ?模擬接口?:CP_OUT(電荷泵輸出)、OPA_IN/OUT(運(yùn)算放大器接口)。

?4. 應(yīng)用場(chǎng)景?

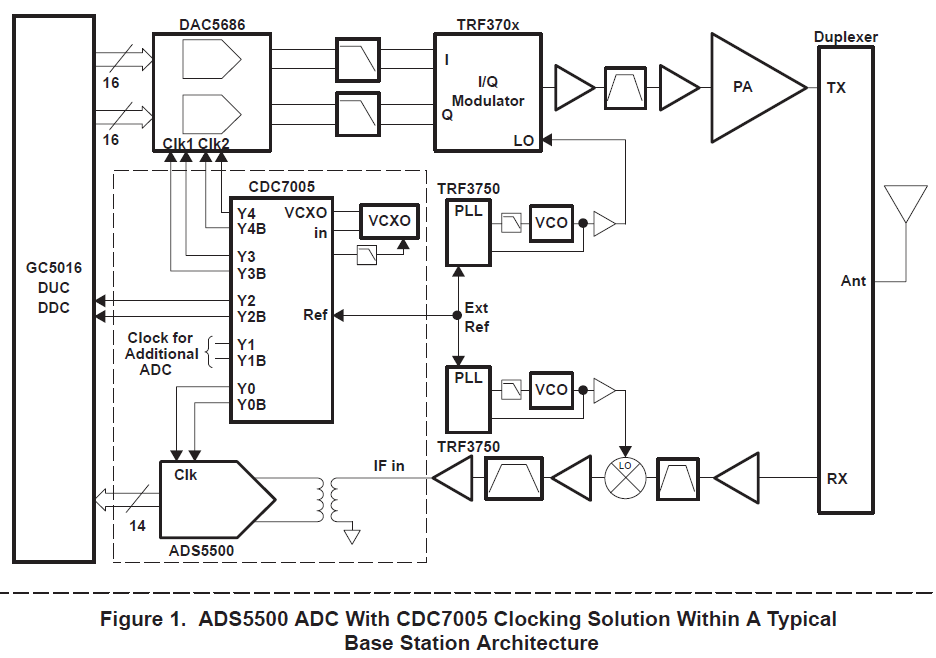

- ?高速數(shù)據(jù)轉(zhuǎn)換器時(shí)鐘?:如DAC5686等插值DAC的采樣時(shí)鐘生成,支持多路相位對(duì)齊輸出(±200 ps偏斜)。

- ?通信系統(tǒng)?:3G基站中的時(shí)鐘分配,支持245.76 MHz高頻與61.44 MHz數(shù)據(jù)時(shí)鐘同步。

?5. 電氣特性?

- ?相位噪聲性能?(典型值):

- 10 Hz: -105 dBc/Hz

- 100 kHz: -152 dBc/Hz

- ?功耗?:全輸出激活時(shí)典型電流265 mA(3.6V供電)。

?6. 設(shè)計(jì)支持?

- ?參考電路?:提供被動(dòng)環(huán)路濾波器設(shè)計(jì)示例(如圖7),優(yōu)化相位噪聲與穩(wěn)定性。

- ?文檔擴(kuò)展?:參考應(yīng)用筆記SCAA067獲取VCXO選型與相位噪聲測(cè)試數(shù)據(jù)。

?7. 注意事項(xiàng)?

- ?熱管理?:需確保封裝散熱焊盤接地,BGA封裝熱阻54°C/W(無(wú)氣流)。

- ?SPI時(shí)序?:嚴(yán)格遵循CTRL_LE/CLK/DATA的建立/保持時(shí)間(詳見(jiàn)圖1時(shí)序圖)。

本文檔完整覆蓋CDC7005的功能、配置、電氣參數(shù)及典型應(yīng)用,適用于高頻時(shí)鐘系統(tǒng)的硬件設(shè)計(jì)參考。

-

分頻器

+關(guān)注

關(guān)注

43文章

537瀏覽量

53566 -

時(shí)鐘

+關(guān)注

關(guān)注

11文章

1993瀏覽量

135121 -

晶體振蕩器

+關(guān)注

關(guān)注

9文章

749瀏覽量

33352 -

清除器

+關(guān)注

關(guān)注

0文章

56瀏覽量

6105 -

同步器

+關(guān)注

關(guān)注

1文章

117瀏覽量

15676

發(fā)布評(píng)論請(qǐng)先 登錄

能有效降低高速網(wǎng)絡(luò)誤碼率的超低抖動(dòng)時(shí)鐘合成器

敏捷合成器的技術(shù)原理和應(yīng)用場(chǎng)景

詳解頻率合成器高性能架構(gòu)的實(shí)現(xiàn)

超低抖動(dòng)時(shí)鐘合成器的設(shè)計(jì)挑戰(zhàn)

限制性試劑影響ADC的信噪比性能和CDC7005與ADS5500的比較詳細(xì)概述

CDC7005高性能時(shí)鐘頻率合成器和抖動(dòng)消除器數(shù)據(jù)表

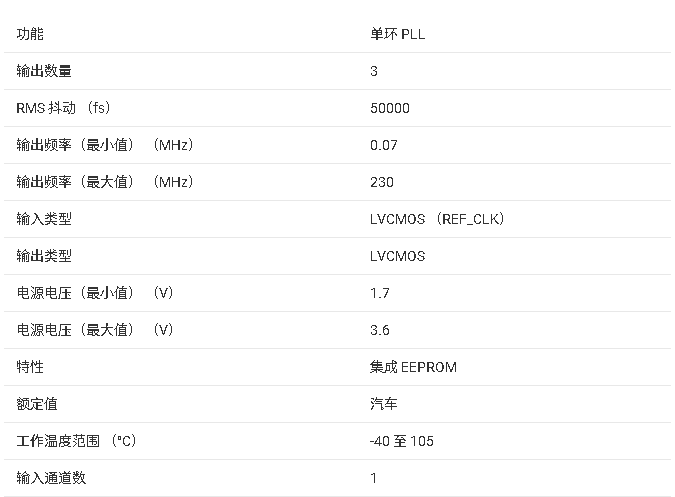

高性能時(shí)鐘抖動(dòng)清除器LMK04714-Q1技術(shù)解析

?CDCE813-Q1 可編程時(shí)鐘合成器與抖動(dòng)清除器技術(shù)文檔總結(jié)

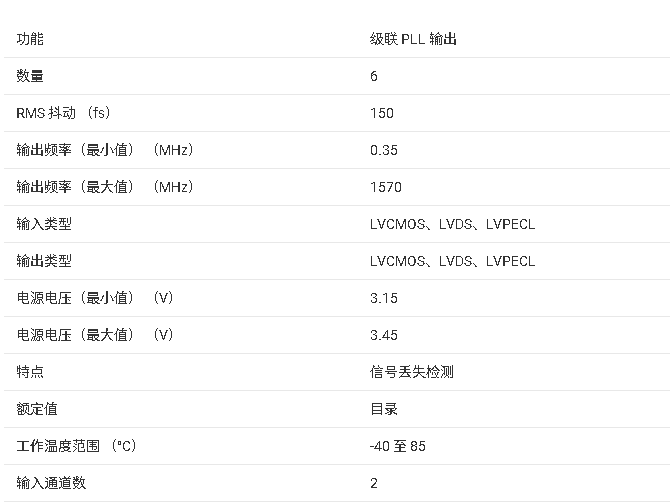

LMK04131 抖動(dòng)清除器技術(shù)文檔總結(jié)

LMK04102 抖動(dòng)清除器技術(shù)文檔總結(jié)

?CDCM7005 高性能時(shí)鐘同步器和抖動(dòng)清除器技術(shù)文檔總結(jié)

?CDC7005高性能時(shí)鐘合成器與抖動(dòng)清除器技術(shù)文檔總結(jié)

?CDC7005高性能時(shí)鐘合成器與抖動(dòng)清除器技術(shù)文檔總結(jié)

評(píng)論