CDC7005:高性能時鐘合成器與抖動消除器

在電子工程師的日常工作中,時鐘合成器與抖動消除器是至關重要的元件,它們能夠為系統提供精準且穩定的時鐘信號。今天要給大家介紹一款性能卓越的產品——德州儀器(Texas Instruments)的CDC7005,一款3.3 - V高性能時鐘合成器與抖動消除器。

文件下載:cdc7005.pdf

一、產品概述

CDC7005是一款高性能的時鐘同步器,具備低相位噪聲、低偏移等出色特性,能夠將壓控晶體振蕩器(VCXO)的頻率與參考時鐘同步。其可編程的預分頻器M和N為參考時鐘與VCXO的頻率比提供了高度的靈活性,計算公式為:$VCXO_IN / REF_IN =(NxP) / M$,VCXO_IN時鐘的工作頻率最高可達800 MHz。

該器件采用3.3 - V電源供電,擁有兩個時鐘輸入(VCXO_IN和REF_IN),能夠同步高達800 MHz的頻率,并支持五個差分LVPECL輸出,每個輸出頻率可通過x1、/2、/4、/8、/16進行選擇,且所有輸出均能保持同步。此外,它還集成了低噪聲運算放大器(OPA),可用于外部低通濾波器,能夠有效篩選抖動,具有低相位噪聲的特點。產品支持可編程延遲用于相位調整、預分頻器環路帶寬調整,并且可通過SPI控制進行分頻設置。在電源方面,當$V_{CC} < 1.5 V$時,上電控制會使LVPECL輸出處于三態。

CDC7005提供兩種封裝形式,分別是64 - 引腳的BGA(0.8 mm間距 - ZVA)或48 - 引腳的QFN(RGZ),適用于工業溫度范圍(–40°C至85°C)。

二、引腳功能與結構

2.1 引腳分配

| CDC7005的引腳眾多,不同引腳具有不同的功能。例如,AVCC為3.3 - V模擬電源供電引腳,CP_OUT為電荷泵輸出引腳,CTRL_LE、CTRL_CLK和CTRL_DATA則是SPI接口的控制引腳,用于對器件進行配置。詳細的引腳分配可參考下面的表格: | PIN | BGA | QFN | TYPE | DESCRIPTION |

|---|---|---|---|---|---|

| AVCC | C3, C4, C5, C6, C7 | 27, 30, 32, 38, 39 | Power | 3.3 - V模擬電源供電 | |

| CP_OUT | A4 | 31 | O | 電荷泵輸出 | |

| CTRL_LE | A1 | 36 | I | LVCMOS輸入,用于SPI的控制負載使能 | |

| CTRL_CLK | A2 | 35 | I | LVCMOS輸入,SPI的串行控制時鐘輸入 | |

| CTRL_DATA | A3 | 33 | I | LVCMOS輸入,SPI的串行控制數據輸入 | |

| ...... | ...... | ...... | ...... | ...... |

2.2 功能框圖

CDC7005的功能框圖展示了其內部結構和信號流向。它主要由PFD電荷泵、可編程分頻器、邏輯控制單元、LVPECL輸出模塊等部分組成。參考時鐘REF_IN和VCXO時鐘VCXO_IN經過一系列處理后,通過LVPECL輸出端輸出同步的時鐘信號。OPA模塊用于外部低通濾波器,可有效減少抖動。

三、SPI控制接口

CDC7005的串行接口是一個簡單的SPI兼容接口,用于對器件的寄存器進行寫入操作。它由三根控制線(CTRL_CLK、CTRL_DATA和CTRL_LE)組成,共有四個32位寬的寄存器,可通過傳輸字的兩個最低有效位(bit 0和bit 1)進行尋址。每個傳輸的字必須為32位,且從最高有效位(MSB)開始。

在初始化時,建議在電源上電且NPD變為高電平后,立即對Word 0、Word 1、Word 2和Word 3進行編程。SPI傳輸通過CTRL_LE的下降沿啟動,當CTRL_LE為高電平時,數據無法傳輸;當CTRL_LE為低電平時,可進行數據寫入。數據需在CTRL_DATA上提供,并在CTRL_CLK的上升沿之前保持穩定。傳輸結束于CTRL_LE的上升沿,此時新的字將異步傳輸到內部寄存器。

四、寄存器功能

4.1 寄存器編程

CDC7005的四個32位寄存器(Word 0、Word 1、Word 2和Word 3)分別控制著器件的不同功能。例如,Word 0控制著參考分頻器M、PFD脈沖寬度、CP電流設置、輸出三態等功能;Word 1控制著VCXO分頻器N、MUX選擇、CP調節方向等功能。詳細的寄存器位功能可參考文檔中的表格。

4.2 編程示例

在實際應用中,我們需要根據具體需求對寄存器進行編程。例如,如果需要設置參考分頻器M的值為128,可通過Word 0中的M0 - M9位進行設置。假設我們使用SPI接口進行編程,代碼示例如下(這里只是一個簡單的示意,實際代碼需根據具體的硬件平臺進行調整):

// 假設SPI通信函數已經實現

// 設置Word 0的M0 - M9位為對應的值(128的二進制編碼為00000111111)

uint32_t word0_value = 0x000000FF; // 根據實際需求修改

// 發送Word 0到CDC7005

SPI_SendData(word0_value);五、性能指標

5.1 電氣參數

CDC7005在電氣性能方面表現出色,在推薦的工作條件下,其電源電流ICC典型值為230 mA($f{VCXO} = 245 MHz$,$f{REF_IN} = 30 MHz$,$V{CC} = 3.6 V$,$AV{CC} = 3.6 V$,$f{PFD} = 240 kHz$,$I{CP} = 2 mA$)。LVCMOS輸入電流在$V{I} = 0 V$或$V{CC}$時,典型值為±5 μA;LVPECL輸出的差分輸出電壓在10 ≤ $f_{OUT}$ ≤ 800 MHz時,典型值為500 mV。

5.2 噪聲性能

在噪聲方面,CDC7005在不同頻率下的相位噪聲表現良好。例如,在30.72 MHz參考時鐘下,10 Hz時的相位噪聲典型值為?77 dBc/Hz,100 Hz時為?95 dBc/Hz,1 kHz時為?118 dBc/Hz。在245.76 MHz VCXO時鐘下,相位噪聲也能滿足大多數應用的需求。

5.3 時序要求

CDC7005對輸入信號的時序有一定要求。REF_IN時鐘頻率范圍為3.5 - 180 MHz,上升和下降時間在20% - 80% $V{CC}$時最大為4 ns,占空比為40% - 60%。VCXO_IN和VCXO_INB時鐘頻率范圍為10 - 800 MHz,在80 MHz - 800 MHz時,上升和下降時間在20% - 80% $V{INPP}$時最大為3 ns,占空比為40% - 60%。

六、應用場景

6.1 高速ADC和DAC時鐘生成

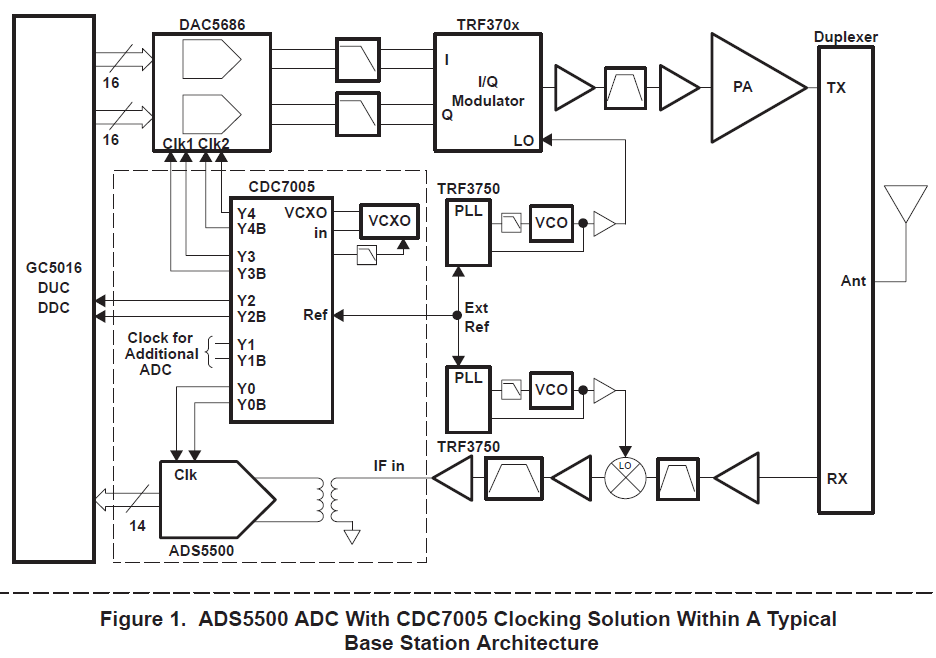

CDC7005憑借其出色的相位噪聲性能,成為高速ADC和DAC的理想采樣時鐘發生器。特別是對于集成了插值濾波器的新型高速DAC,如DAC5686,CDC7005能夠提供滿足其要求的時鐘信號。在3G系統中,常見的高速DAC采樣率為245.76 MSPS,通過四倍插值,數字輸入所需的數據速率可降低至61.44 MSPS,這一數據速率可由數字端輕松支持。CDC7005能夠生成數據輸入時鐘和DAC時鐘,并保證兩個時鐘信號的邊緣相位在±500 ps內對齊,確保數據正確鎖存。

6.2 其他應用

除了高速ADC和DAC時鐘生成,CDC7005還可應用于其他對時鐘信號要求較高的領域,如通信設備、測試儀器、數據采集系統等。其低相位噪聲和低偏移特性能夠為這些系統提供穩定、精準的時鐘信號,提高系統的性能和可靠性。

七、總結

CDC7005是一款功能強大、性能卓越的時鐘合成器與抖動消除器,具有高度的靈活性和穩定性。其豐富的功能和出色的性能使其在眾多領域都有廣泛的應用前景。在實際設計中,電子工程師可以根據具體需求,合理配置寄存器,選擇合適的外部元件,以實現最佳的性能表現。同時,在使用過程中,要注意滿足其電氣參數和時序要求,確保器件的正常工作。大家在實際應用中是否遇到過時鐘信號不穩定的問題呢?CDC7005是否能為你解決這些問題?歡迎在評論區分享你的經驗和見解。

-

時鐘合成器

+關注

關注

0文章

113瀏覽量

8891

發布評論請先 登錄

能有效降低高速網絡誤碼率的超低抖動時鐘合成器

詳解頻率合成器高性能架構的實現

超低抖動時鐘合成器的設計挑戰

超低抖動時鐘合成器的設計挑戰

超低抖動時鐘合成器的設計挑戰

超低抖動時鐘合成器的設計挑戰

限制性試劑影響ADC的信噪比性能和CDC7005與ADS5500的比較詳細概述

CDC7005:高性能時鐘合成器與抖動消除器

CDC7005:高性能時鐘合成器與抖動消除器

評論