LMK04100系列精密時鐘調節器無需高性能VCXO模塊即可提供抖動清除、時鐘倍增和分配。

當連接到恢復的系統基準時鐘和VCXO時,該器件可生成5個LVCMOS、LVDS或LVPECL格式的低抖動時鐘。

*附件:lmk04102.pdf

特性

- 級聯 PLLatinum PLL 架構

- PLL1冗余基準輸入信號丟失

檢測自動和手動選擇

基準時鐘輸入 - PLL2相位檢測器速率高達100 MHz輸入

倍頻器集成VCO

- PLL1冗余基準輸入信號丟失

- 輸出

- LVPECL/2VPECL、LVDS 和

LVCMOS 格式 - 支持高達 1080 MHz 的時鐘速率

- 五個專用通道分頻器模塊

- 支持的常見輸出頻率:

30.72 MHz、61.44 MHz、62.5 MHz、

74.25 MHz、75 MHz、77.76 MHz、100 MHz、

106.25 MHz、125 MHz、122.88 MHz、

150 MHz、155.52 MHz、156.25 MHz、159.375 MHz、

187.5 MHz、200 MHz、

212.5 MHz、245.76 MHz、250 MHz、311.04 MHz、

312.5 MHz、368.64 MHz、

491.52 MHz、622.08 MHz、625 MHz、983.04 MHz

- LVPECL/2VPECL、LVDS 和

- MICROWIRE (SPI) 編程接口

- 工業溫度范圍:–40 至 85 °C

- 3.15 V 至 3.45 V 工作電壓

- 封裝:48 引腳 WQFN(7.0 × 7.0 × 0.8 mm)

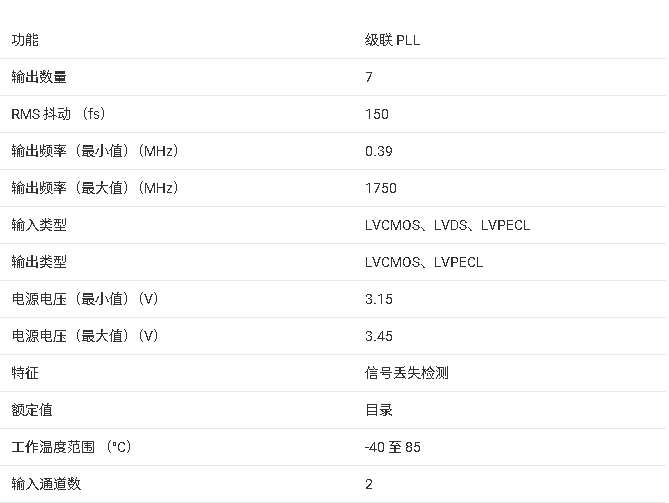

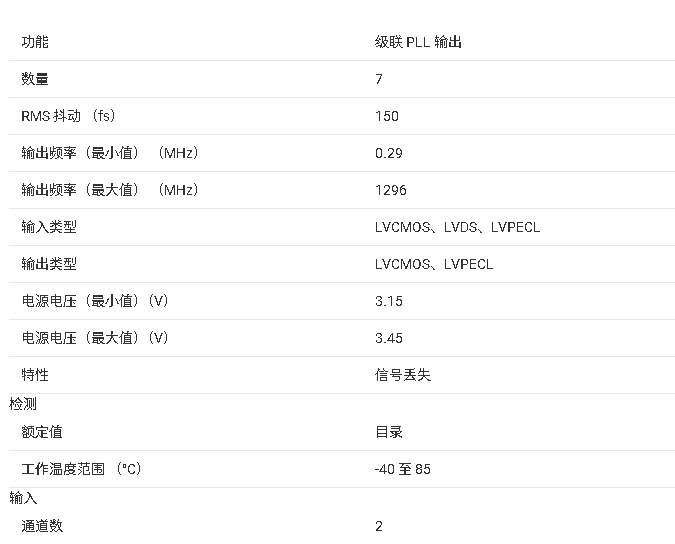

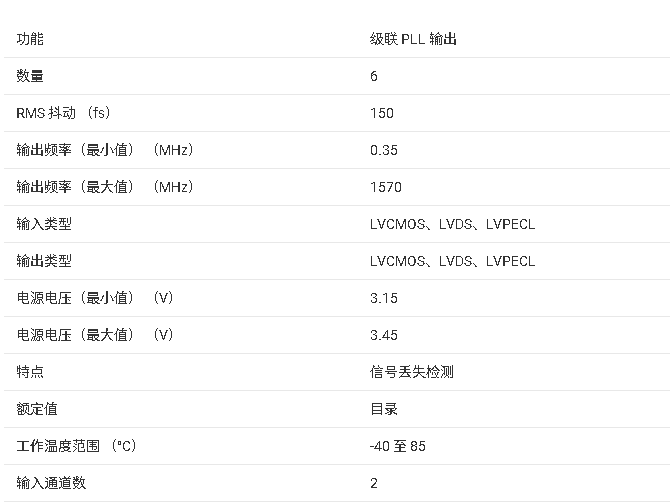

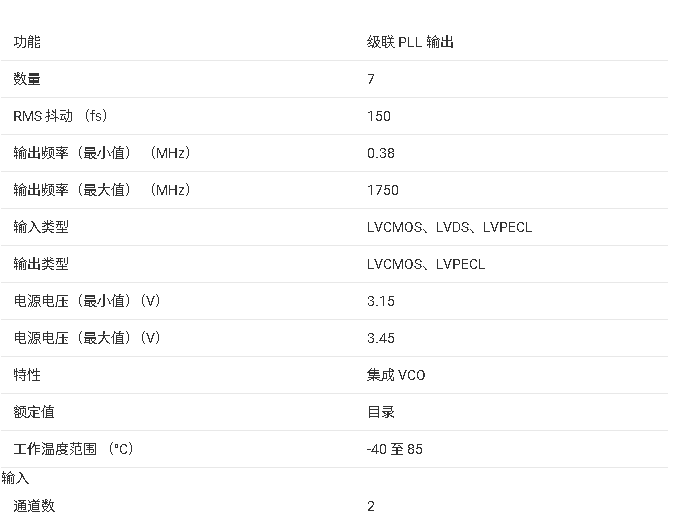

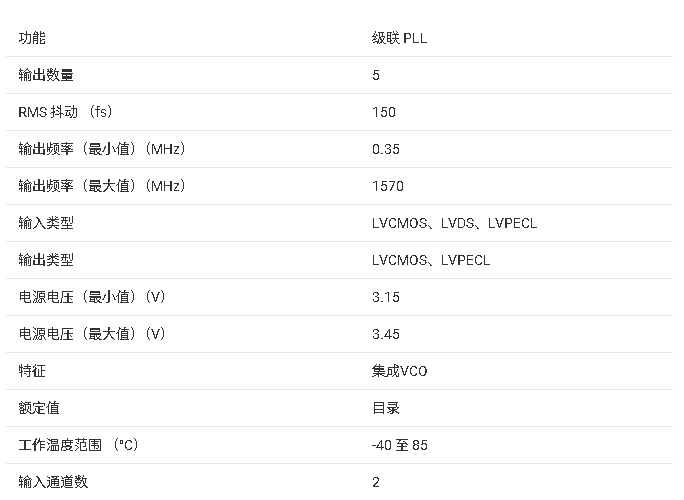

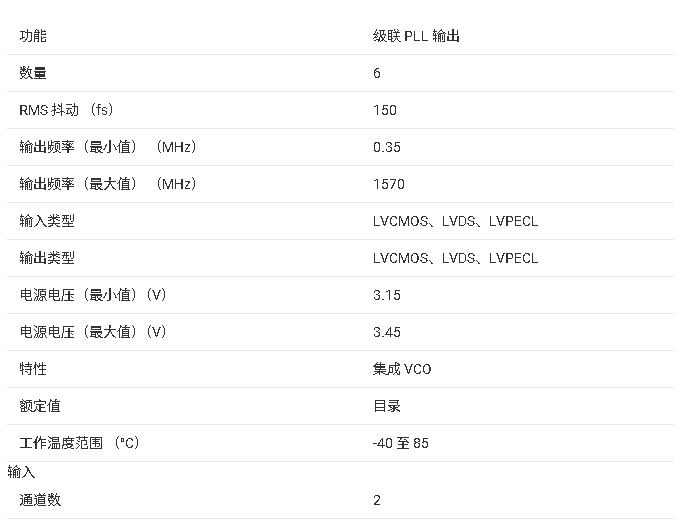

參數

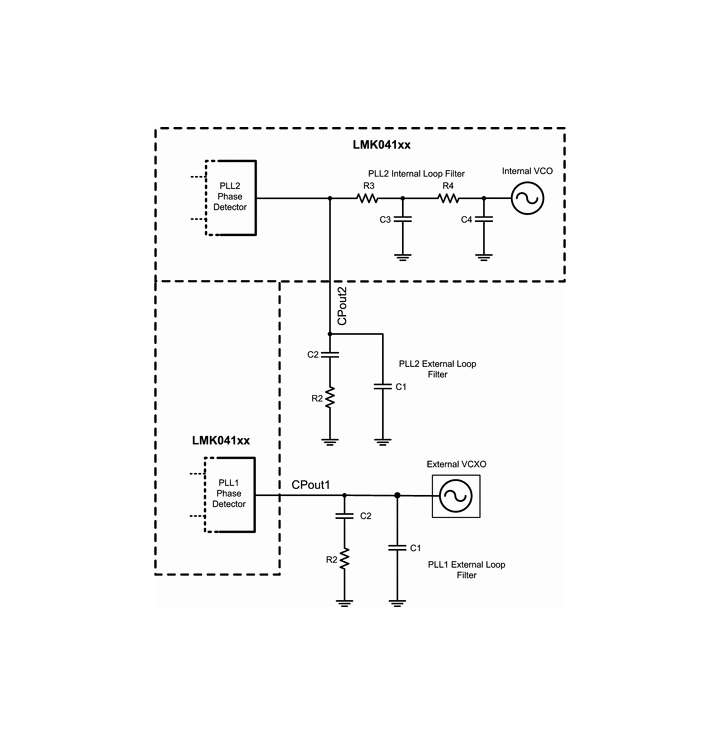

方框圖

?1. 產品概述?

LMK04100系列(含LMK04100/01/02/10/11/31/33等型號)是德州儀器(TI)推出的精密時鐘調理芯片,采用級聯PLL架構,專為低抖動時鐘生成、乘法及分配設計。核心特點包括:

- ?雙PLL架構?:PLL1支持冗余參考輸入(CLKin0/1)和信號丟失檢測,PLL2集成VCO并支持高達100MHz的相位檢測速率。

- ?多格式輸出?:提供LVPECL/2VPECL、LVDS、LVCMOS格式輸出,頻率覆蓋30.72MHz至983.04MHz。

- ?工業級性能?:工作溫度-40°C至85°C,3.15V至3.45V供電,48引腳WQFN封裝(7.0×7.0×0.8mm)。

?2. 關鍵特性?

- ?PLL1?:支持自動/手動參考時鐘切換,電荷泵電流可編程(20μA至400μA),窄帶寬設計(10Hz–200Hz)優化參考時鐘噪聲抑制。

- ?PLL2?:集成VCO(頻率范圍1185–2160MHz),支持頻率倍增器,寬帶寬(50kHz–200kHz)降低高頻相位噪聲。

- ?輸出配置?:5個獨立可編程通道,支持分頻(2–510)、同步(SYNC*引腳)及全局使能(GOE引腳)。

?3. 應用場景?

?4. 電氣特性?

- ?抖動性能?:12kHz–20MHz積分RMS抖動低至140fs(LVDS@122.88MHz)。

- ?功耗?:典型值435mA(全輸出使能),支持可編程省電模式。

- ?接口?:MICROWIRE(SPI)編程,支持寄存器配置PLL參數、輸出格式及分頻比。

?5. 設計支持?

- ?環路濾波器?:PLL2支持集成3/4階濾波器(可編程R/C值),減少外部元件需求。

- ?熱管理?:裸露焊盤(DAP)需連接PCB地平面,θJA=27.4°C/W(建議布局散熱過孔)。

- ?參考設計?:提供晶體振蕩器(OSCin)及VCXO連接方案,含環路濾波器計算示例。

?6. 文檔結構?

- ?寄存器映射?:詳細描述32位寄存器配置(如R0–R4控制輸出分頻/使能,R12–R15配置PLL參數)。

- ?時序圖?:包括uWire編程時序、鎖相檢測信號(LD)輸出選項。

- ?性能曲線?:涵蓋輸出擺幅、噪聲基底與頻率關系。

?總結?:LMK04100系列通過級聯PLL和靈活輸出配置,為高速通信和數據處理系統提供高精度、低抖動的時鐘解決方案,適用于嚴苛環境下的多頻段、多模式應用。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

pll

+關注

關注

6文章

985瀏覽量

138301 -

調節器

+關注

關注

5文章

913瀏覽量

49589 -

清除器

+關注

關注

0文章

56瀏覽量

6108 -

VCXO

+關注

關注

0文章

58瀏覽量

10120 -

LVCMOS

+關注

關注

1文章

142瀏覽量

12029

發布評論請先 登錄

相關推薦

熱點推薦

LMK04832-SP時鐘抖動清除器

SYSREF分頻器SYSREF時鐘的25ps步進模擬延遲設備時鐘和SYSREF的數字延遲和動態數字延遲PLL1的保持模式PLL1或PLL2的0延遲環境溫度范圍:–55°C至125°CLMK5C33216LMK04816LMK04808LMK04832-SPLMK04906LMK

發表于 03-24 16:13

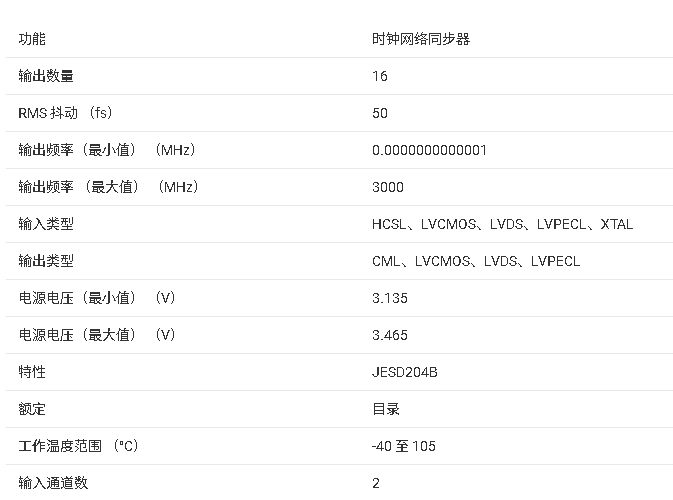

?LMK5C33216A 網絡同步器與抖動清除器總結

LMK5C33216A是一款高性能網絡同步器和抖動清除器,旨在滿足無線通信和基礎設施應用的嚴格要求。

該器件集成了三個 DPLL 和三個 APLL,通過可編程環路帶寬 (LBW)

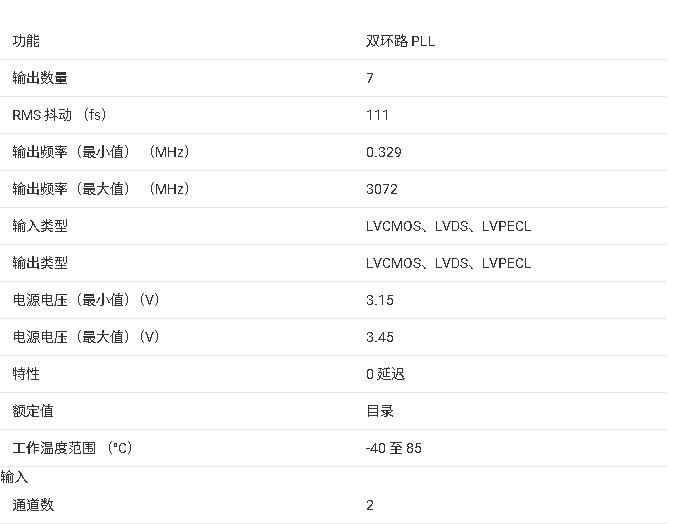

?LMK04208低噪聲時鐘抖動清除器技術文檔總結

LMK04208是一款高性能時鐘調節器,具有卓越的時鐘抖動清除功能, 生成和分發具有高級功能,以滿足下一代系統要求。 雙環路PLLatinum?架構能夠 使用低噪聲VCXO模塊的RMS

?LMK04100系列時鐘抖動清除器技術文檔總結

LMK04100系列精密時鐘調節器無需高性能VCXO模塊即可提供抖動清除、時鐘倍增和分配。

當連接到恢復的系統基準時鐘和VCXO時,該器件可生成5個LVCMOS、LVDS或LVP

LMK04131 抖動清除器技術文檔總結

LMK04100系列精密時鐘調節器無需高性能VCXO模塊即可提供抖動清除、時鐘倍增和分配。

當連接到恢復的系統基準時鐘和VCXO時,該器件可生成5個LVCMOS、LVDS或LVP

LMK5C33414A:高性能網絡同步器與抖動清除器的深度剖析

LMK5C33414A:高性能網絡同步器與抖動清除器的深度剖析 在無線通信和基礎設施應用領域,時鐘同步和抖動控制至關重要。TI推出的

低噪聲時鐘抖動清除器LMK04610:技術拆解與應用設計

低噪聲時鐘抖動清除器LMK04610:技術拆解與應用設計 在電子設備的世界里,時鐘信號就如同心臟的跳動,穩定而精準的時鐘對于各類系統的正常運行至關重要。今天,我們要深入探討的就是一款在

LMK0482x系列時鐘抖動清除器:高性能時鐘解決方案解析

LMK0482x系列時鐘抖動清除器:高性能時鐘解決方案解析 在電子設計領域,時鐘信號的穩定性和低抖動對于系統性能至關重要。LMK0482x系

探索LMK04100系列時鐘抖動清除器:特性、應用與設計要點

探索LMK04100系列時鐘抖動清除器:特性、應用與設計要點 引言 在電子設計領域,時鐘信號的穩定性和低抖動特性對于眾多應用至關重要。德州儀器(TI)的

深入解析LMK04100系列時鐘抖動清除器:從特性到應用

深入解析LMK04100系列時鐘抖動清除器:從特性到應用 在電子設計領域,時鐘信號的穩定性和低抖動對于系統性能至關重要。TI的LMK0410

LMK04000 系列低噪聲時鐘抖動清除器:功能、應用與設計指南

LMK04000 系列低噪聲時鐘抖動清除器:功能、應用與設計指南 在電子設計領域,時鐘抖動的控制至關重要,它直接影響著系統的性能和穩定性。TI 的

LMK04102 抖動清除器技術文檔總結

LMK04102 抖動清除器技術文檔總結

評論