電子發燒友網報道(文/李彎彎)近日消息,英特爾與軟銀集團宣布達成戰略合作,共同開發具有劃時代意義的AI專用內存芯片。這項合作將致力于突破當前AI計算中的能耗瓶頸,有望將芯片功耗降低50%,為全球AI基礎設施建設帶來革命性變化。

隨著AI技術的快速發展,高性能、低功耗的計算硬件需求日益增長。然而,現有的AI內存技術存在高成本、高功耗及發熱問題,限制了AI數據中心的進一步擴展和效率提升。據悉,軟銀與英特爾將研發一種創新的堆疊式DRAM芯片,采用全新的布線架構,完全不同于現有高帶寬內存(HBM)技術方案。

這種新型AI內存芯片可能在哪些方面進行創新呢?首先,在架構層面,現有HBM技術主要采用TSV(硅通孔)垂直互連技術實現芯片堆疊,而創新方案采用全新布線架構,可能突破傳統TSV的布局限制,通過更優化的布線設計減少信號傳輸路徑的曲折和干擾,從而降低信號延遲和功耗。例如,可能采用新的層間互連方式,使數據在芯片堆疊層之間的傳輸更加直接高效。

HBM通過寬接口和并行傳輸實現高帶寬,創新方案可能進一步優化通道數量和數據接口設計。比如增加通道數量,或者改進數據接口的信號傳輸機制,提高數據傳輸的效率和穩定性,在相同甚至更低的功耗下實現更高的帶寬。

在芯片堆疊與封裝層面,不同于HBM的堆疊方式,創新方案可能采用全新的芯片堆疊結構,提高堆疊密度和穩定性。例如,采用更緊密的堆疊方式,減少芯片之間的間隙,從而降低整體封裝尺寸和信號傳輸距離。

還可以通過改進封裝技術,提高芯片的散熱性能和電氣連接可靠性。例如,采用更高效的散熱材料和封裝結構,及時將芯片產生的熱量散發出去,避免因過熱導致的性能下降和功耗增加;同時,優化芯片與封裝基板之間的電氣連接,降低連接電阻,減少功耗。

據稱,英特爾與軟銀這種突破性設計不僅大幅提升能效比,更將為AI數據中心的綠色轉型提供關鍵技術支持。業內專家指出,該技術若能成功商業化,將顯著降低AI計算的運營成本,對推動可持續發展具有重要意義。

為推進這一重大項目,雙方聯合成立了專門公司Saimemory,負責芯片的設計和專利管理。制造環節則委托專業代工廠完成,這種分工協作模式有望最大化研發效率。研發團隊將采用不同于現有HBM技術的布線方式,通過垂直堆疊多顆DRAM芯片,并改進芯片間的互連技術,實現至少大一倍的存儲容量,同時將耗電量減少40%以上。

根據項目規劃,研發團隊將在兩年內完成芯片原型設計,之后啟動量產評估程序,目標是在本世紀二十年代末實現商業化應用。項目總投資額預計達100億日元(約合5億元人民幣),其中軟銀作為領投方已承諾注資30億日元(約1.5億元人民幣)。

不過,盡管軟銀與英特爾在芯片設計和制造方面擁有豐富的經驗和技術積累,但新型AI內存芯片的研發仍面臨諸多技術挑戰,如這種創新的式DRAM芯片的良率控制、量產成本能否真正低于HBM等。

當然,隨著AI技術的廣泛應用和數據中心規模的不斷擴大,高性能、低功耗的內存技術需求將持續增長。如果新型AI內存芯片能夠成功商業化并滿足市場需求,將具有廣闊的市場前景和商業價值。

-

DRAM

+關注

關注

41文章

2392瀏覽量

189134 -

HBM

+關注

關注

2文章

431瀏覽量

15831

發布評論請先 登錄

不同于HBM垂直堆疊,英特爾新型內存ZAM技術采用交錯互連拓撲結構

消息稱英偉達HBM4訂單兩家七三分,獨缺這一家

創新的高帶寬DRAM解決方案

Kioxia研發核心技術,助力高密度低功耗3D DRAM的實際應用

SK海力士HBS存儲技術,基于垂直導線扇出VFO封裝工藝

HBM技術在CowoS封裝中的應用

新思科技UCIe IP解決方案實現片上網絡互連

突破堆疊瓶頸:三星電子擬于16層HBM導入混合鍵合技術

簡單認識高帶寬存儲器

美光12層堆疊36GB HBM4內存已向主要客戶出貨

芯片晶圓堆疊過程中的邊緣缺陷修整

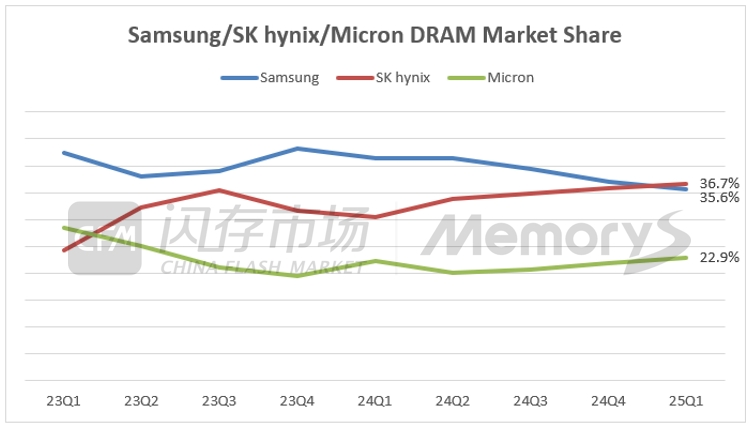

HBM重構DRAM市場格局,2025年首季DRAM市占排名

不同于HBM,這種創新的堆疊式DRAM,功耗有望降低50%

不同于HBM,這種創新的堆疊式DRAM,功耗有望降低50%

評論